Verilog CIC 滤波器设计(代码自取)_cic截止频率-程序员宅基地

前言:积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器,资源消耗少,运算速率高,可实现高速滤波,常用在输入采样率最高的第一级,在多速率信号处理系统中具有着广泛应用。

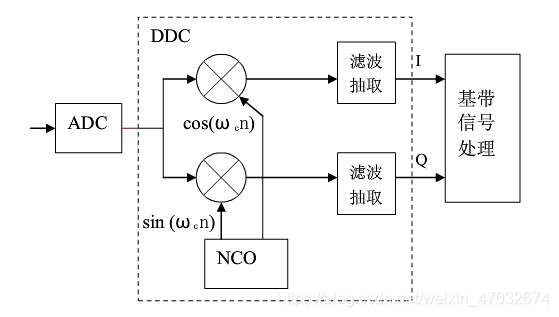

1. DDC 原理

DDC 主要由本地振荡器(NCO) 、混频器、滤波器等组成,如下图所示。

DDC 将中频信号与振荡器产生的载波信号进行混频,信号中心频率被搬移,再经过抽取滤波,恢复原始信号,实现了下变频功能。

中频数据采样时,需要很高的采样频率来确保 ADC(模数转换器)采集到信号的信噪比。经过数字下变频后,得到的基带信号采样频率仍然是 ADC 采样频率,所以数据率很高。此时基带信号的有效带宽往往已经远小于采样频率,所以利用抽取、滤波进行数据速率的转换,使采样率降低,避免资源的浪费和设计的困难,就成为 DDC 不可缺少的一部分。

而采用 CIC 滤波器进行数据处理,是 DDC 抽取滤波部分最常用的方法。

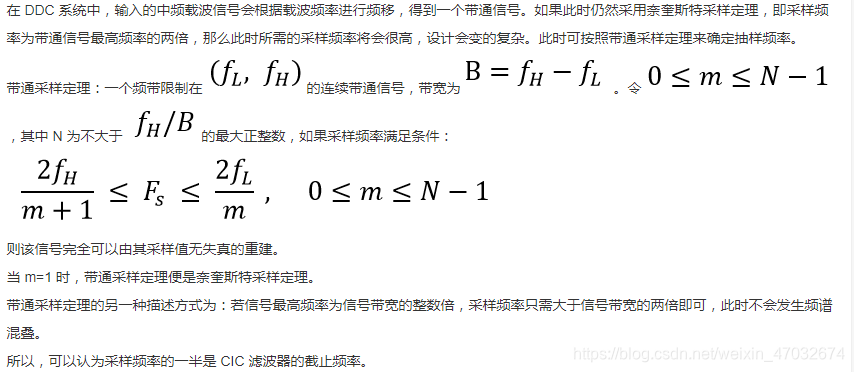

2.带通采样定理

3. DDC 频谱搬移

例如一个带宽信号中心频率为 60MHz,带宽为 8MHz, 则频率范围为 56MHz ~ 64MHz,m 的可取值范围为 0 ~ 7。取 m=1, 则采样频率范围为 64MHz ~ 112MHz。

取采样频率为 80MHz,设 NCO 中心频率为 20 MHz,下面讨论复信号频谱搬移示意图。

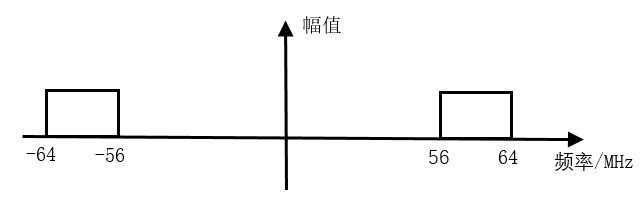

(1)考虑频谱的对称性,输入复信号的频谱示意图如下:

(2)80MHz 采样频率采样后,56~64MHz 的频带被搬移到了 -24~ -16MHz 与 136 ~ 144MHz(高于采样频率被滤除)的频带处,-64~ -56MHz 的频带被搬移到 -144~ -136MHz(高于采样频率被滤除)与 16~24MHz 的频带处。

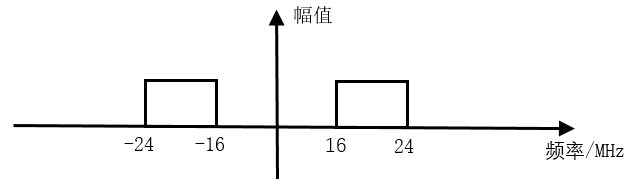

采样后频带分布如下:

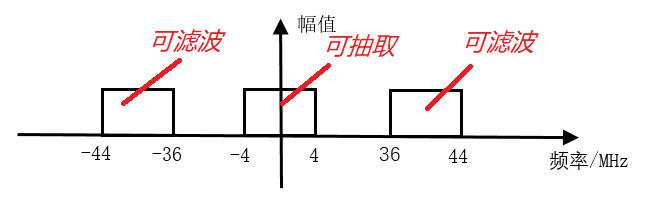

(3)信号经过 20MHz NCO 的正交电路后, -24~ -16MHz 的频带被搬移到 -4~4MHz 与 -44~ -36MHz 的频带处,16~24MHz 的频带被搬移到 -4~4MHz 与 36~44MHz 的频带处,如下所示。

(4)此时中频输入的信号已经被搬移到零中频基带处。

-44~ -36MHz 和 36~44MHz 的带宽信号是不需要的,可以滤除;-4~4MHz 的零中频信号数据速率仍然是 80MHz,可以进行抽取降低数据速率。而 CIC 滤波,就是要完成这个过程。

上述复习了很多数字信号处理的内容,权当抛 DDC 的砖,引 CIC 的玉。

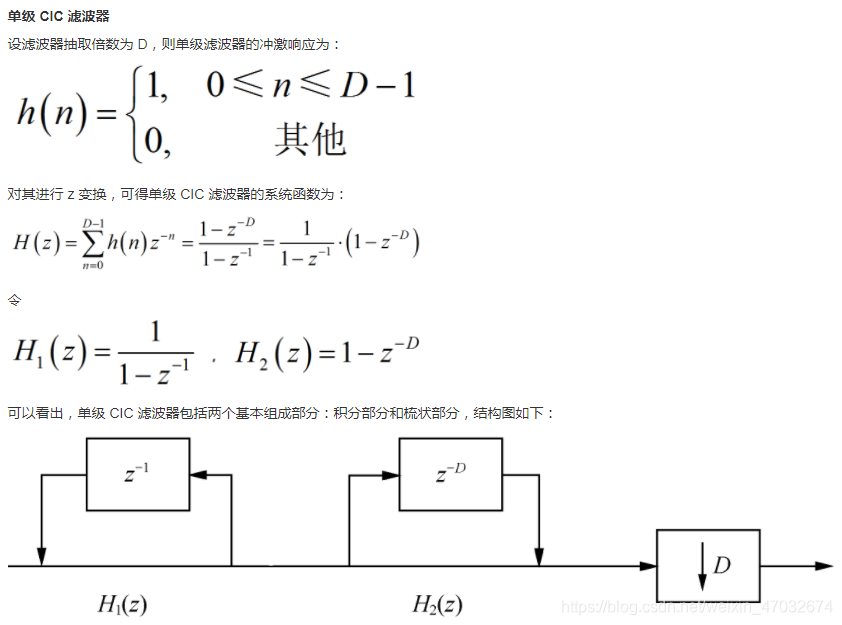

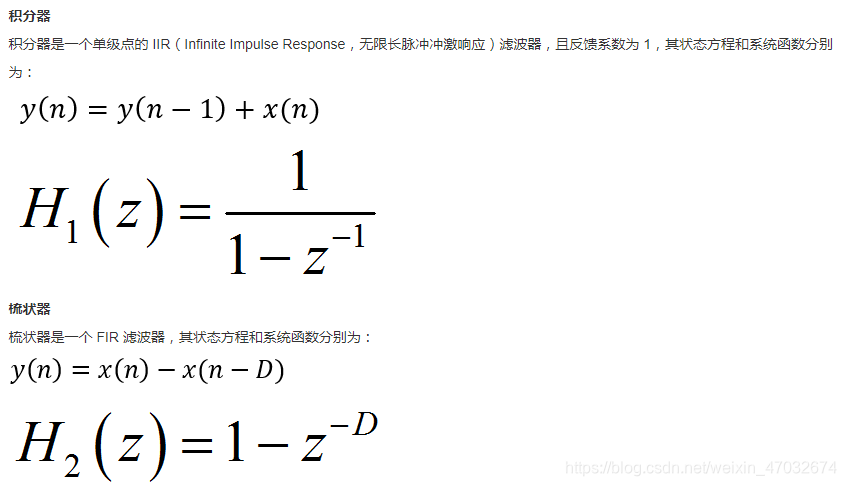

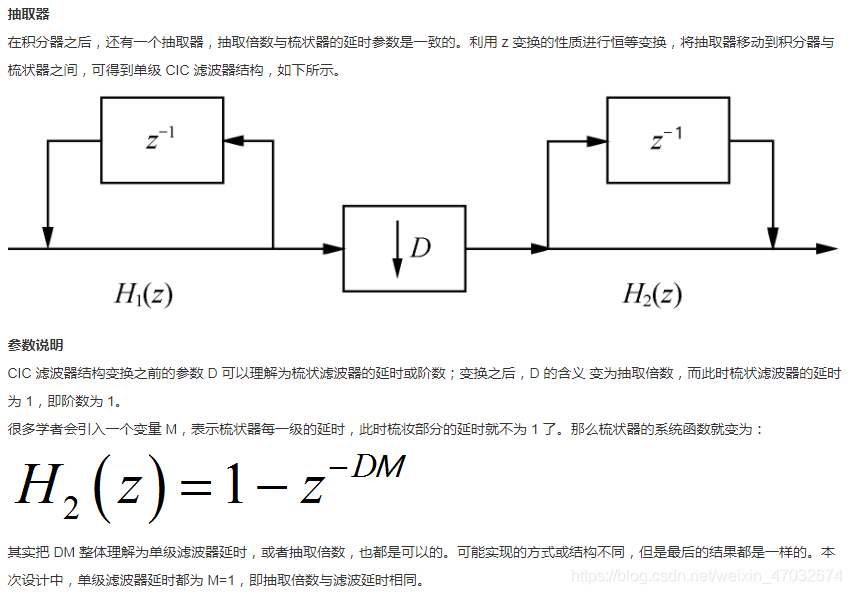

4.CIC 滤波器原理

多级 CIC 滤波器

单级 CIC 滤波器的阻带衰减较差,为了提高滤波效果,抽取滤波时往往会采用多级 CIC 滤波器级联的结构。

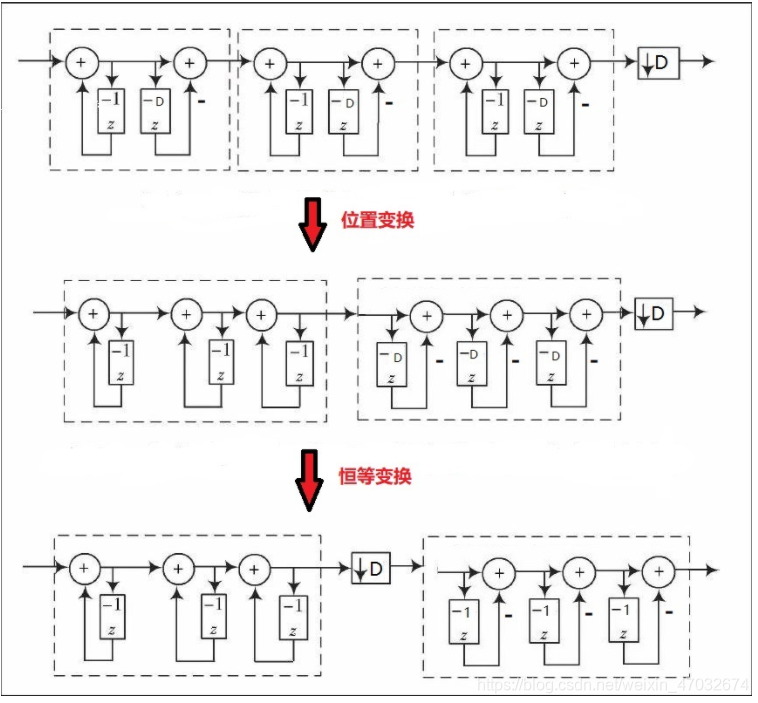

实现多级直接级联的 CIC 滤波器在设计和资源上并不是最优的方式,需要对其结构进行调整。如下所示,将积分器和梳状滤波器分别移至一组,并将抽取器移到梳状滤波器之前。先抽取再进行滤波,可以减少数据处理的长度,节约硬件资源。

当然,级联数越大,旁瓣抑制越好,但是通带内的平坦度也会变差。所以级联数不宜过多,一般最多 5 级。

5.CIC 滤波器设计

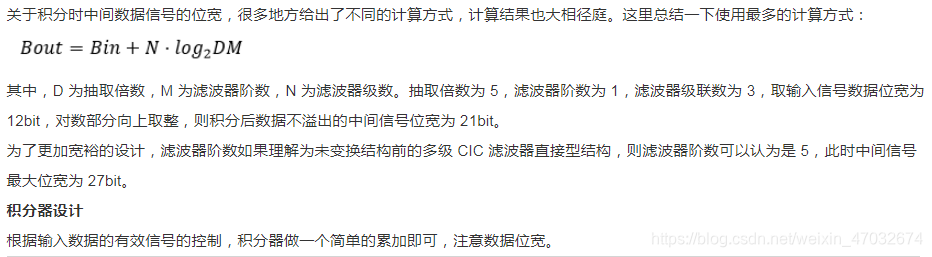

设计说明

CIC 滤波器本质上就是一个简单的低通滤波器,截止频率为采样频率除以抽取倍数后的一半。输入数据信号仍然是 7.5MHz 和 250KHz,采样频率 50MHz。抽取倍数设置为 5,则截止频率为 5MHz,小于 7.5MHz,可以滤除 7.5MHz 的频率成分。设计参数如下:

输入频率: 7.5MHz 和 250KHz

采样频率: 50MHz

阻带: 5MHz

阶数: 1(M=1)

级数: 3(N=3)

//3 stages integrator

module integrator

#(parameter NIN = 12,

parameter NOUT = 21)

(

input clk ,

input rstn ,

input en ,

input [NIN-1:0] din ,

output valid ,

output [NOUT-1:0] dout) ;

reg [NOUT-1:0] int_d0 ;

reg [NOUT-1:0] int_d1 ;

reg [NOUT-1:0] int_d2 ;

wire [NOUT-1:0] sxtx = {

{(NOUT-NIN){1'b0}}, din} ;

//data input enable delay

reg [2:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else begin

en_r <= {en_r[1:0], en};

end

end

//integrator

//stage1

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d0 <= 'b0 ;

end

else if (en) begin

int_d0 <= int_d0 + sxtx ;

end

end

//stage2

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d1 <= 'b0 ;

end

else if (en_r[0]) begin

int_d1 <= int_d1 + int_d0 ;

end

end

//stage3

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d2 <= 'b0 ;

end

else if (en_r[1]) begin

int_d2 <= int_d2 + int_d1 ;

end

end

assign dout = int_d2 ;

assign valid = en_r[2];

endmodule

抽取器设计

抽取器设计时,对积分器输出的数据进行计数,然后间隔 5 个数据进行抽取即可。

module decimation

#(parameter NDEC = 21)

(

input clk,

input rstn,

input en,

input [NDEC-1:0] din,

output valid,

output [NDEC-1:0] dout);

reg valid_r ;

reg [2:0] cnt ;

reg [NDEC-1:0] dout_r ;

//counter

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 3'b0;

end

else if (en) begin

if (cnt==4) begin

cnt <= 'b0 ;

end

else begin

cnt <= cnt + 1'b1 ;

end

end

end

//data, valid

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

valid_r <= 1'b0 ;

dout_r <= 'b0 ;

end

else if (en) begin

if (cnt==4) begin

valid_r <= 1'b1 ;

dout_r <= din;

end

else begin

valid_r <= 1'b0 ;

end

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

梳状器设计

梳状滤波器就是简单的一阶 FIR 滤波器,每一级的 FIR 滤波器对数据进行一个时钟延时,然后做相减即可。因为系数为 ±1,所以不需要乘法器。

module comb

#(parameter NIN = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

//en delay

reg [5:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else if (en) begin

en_r <= {en_r[5:0], en} ;

end

end

reg [NOUT-1:0] d1, d1_d, d2, d2_d, d3, d3_d ;

//stage 1, as fir filter, shift and add(sub),

//no need for multiplier

always @(posedge clk or negedge rstn) begin

if (!rstn) d1 <= 'b0 ;

else if (en) d1 <= din ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d1_d <= 'b0 ;

else if (en) d1_d <= d1 ;

end

wire [NOUT-1:0] s1_out = d1 - d1_d ;

//stage 2

always @(posedge clk or negedge rstn) begin

if (!rstn) d2 <= 'b0 ;

else if (en) d2 <= s1_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d2_d <= 'b0 ;

else if (en) d2_d <= d2 ;

end

wire [NOUT-1:0] s2_out = d2 - d2_d ;

//stage 3

always @(posedge clk or negedge rstn) begin

if (!rstn) d3 <= 'b0 ;

else if (en) d3 <= s2_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d3_d <= 'b0 ;

else if (en) d3_d <= d3 ;

end

wire [NOUT-1:0] s3_out = d3 - d3_d ;

//tap the output data for better display

reg [NOUT-1:0] dout_r ;

reg valid_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

dout_r <= 'b0 ;

valid_r <= 'b0 ;

end

else if (en) begin

dout_r <= s3_out ;

valid_r <= 1'b1 ;

end

else begin

valid_r <= 1'b0 ;

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

顶层例化

按信号的流向将积分器、抽取器、梳状器分别例化,即可组成最后的 CIC 滤波器模块。

梳状滤波器的最终输出位宽一般会比输入信号小一些,这里取 17bit。当然输出位宽完全可以与输入数据的位宽一致。

module cic

#(parameter NIN = 12,

parameter NMAX = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

wire [NMAX-1:0] itg_out ;

wire [NMAX-1:0] dec_out ;

wire [1:0] en_r ;

integrator #(.NIN(NIN), .NOUT(NMAX))

u_integrator (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (en_r[0]),

.dout (itg_out));

decimation #(.NDEC(NMAX))

u_decimator (

.clk (clk),

.rstn (rstn),

.en (en_r[0]),

.din (itg_out),

.dout (dec_out),

.valid (en_r[1]));

comb #(.NIN(NMAX), .NOUT(NOUT))

u_comb (

.clk (clk),

.rstn (rstn),

.en (en_r[1]),

.din (dec_out),

.valid (valid),

.dout (dout));

endmodule

testbench

testbench 编写如下,主要功能就是不间断连续的输入 250KHz 与 7.5MHz 的正弦波混合信号数据。输入的混合信号数据也可由 matlab 生成,具体过程参考《并行 FIR 滤波器设计》一节。

module test ;

parameter NIN = 12 ;

parameter NMAX = 21 ;

parameter NOUT = NMAX ;

reg clk ;

reg rstn ;

reg en ;

reg [NIN-1:0] din ;

wire valid ;

wire [NOUT-1:0] dout ;

//=====================================

// 50MHz clk generating

localparam T50M_HALF = 10000;

initial begin

clk = 1'b0 ;

forever begin

# T50M_HALF clk = ~clk ;

end

end

//============================

// reset and finish

initial begin

rstn = 1'b0 ;

# 30 ;

rstn = 1'b1 ;

# (T50M_HALF * 2 * 2000) ;

$finish ;

end

//=======================================

// read cos data into register

parameter SIN_DATA_NUM = 200 ;

reg [NIN-1:0] stimulus [0: SIN_DATA_NUM-1] ;

integer i ;

initial begin

$readmemh("../tb/cosx0p25m7p5m12bit.txt", stimulus) ;

i = 0 ;

en = 0 ;

din = 0 ;

# 200 ;

forever begin

@(negedge clk) begin

en = 1 ;

din = stimulus[i] ;

if (i == SIN_DATA_NUM-1) begin

i = 0 ;

end

else begin

i = i + 1 ;

end

end

end

end

cic #(.NIN(NIN), .NMAX(NMAX), .NOUT(NOUT))

u_cic (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (valid),

.dout (dout));

endmodule // test

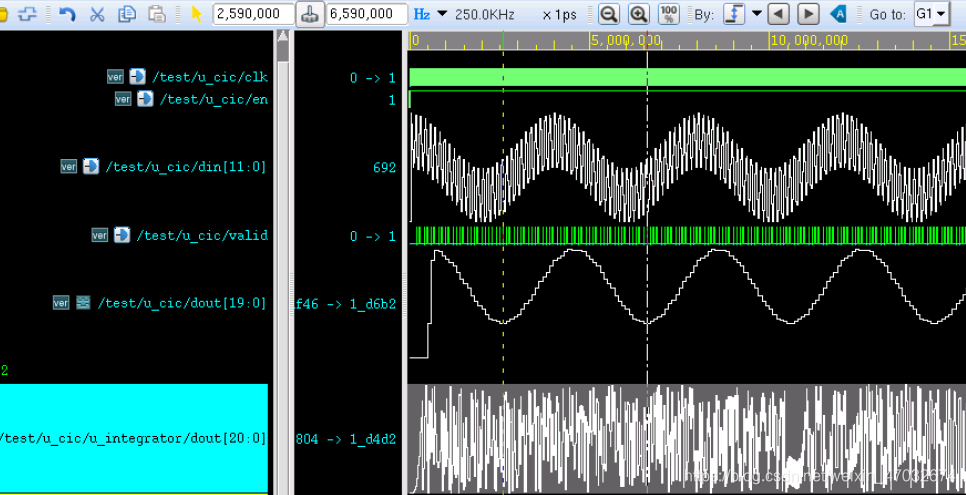

6.仿真结果

由下图仿真结果可知,经过 CIC 滤波器后的信号只有一种低频率信号(250KHz),高频信号(7.5MHz)被滤除了。

但是波形不是非常完美,这与设计的截止频率、数据不是持续输出等有一定关系。

此时发现,积分器输出的数据信号也非常的不规则,这与其位宽有关系。

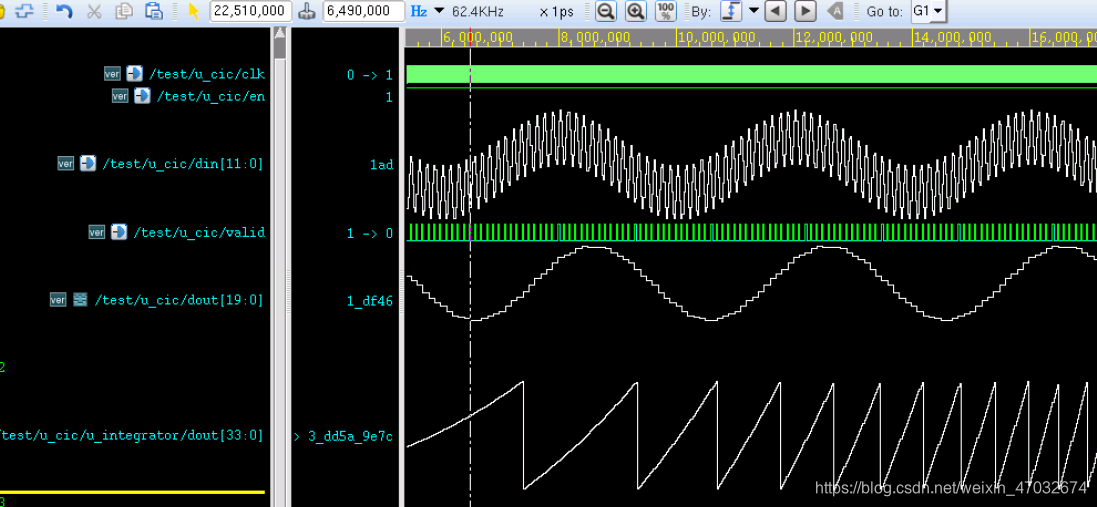

为了更好的观察积分器输出的数据,将其位宽由 21bit 改为 34bit,仿真结果如下。

此时发现,CIC 滤波器的数据输出并没有实质性的变化,但是积分器输出的数据信号呈现锯齿状,也称之为梳状。这也是梳状滤波器名字的由来。

智能推荐

使用IPSET屏蔽美国IP_ipset封禁国外ip-程序员宅基地

文章浏览阅读387次,点赞6次,收藏8次。最近被美国IP盯上了,瞄的不间断攻击ADD-TO-CART页面。记录下用IPSET屏蔽过程。执行如下脚本,将IP地址段中的记录转换为Ipset指令,保存在。_ipset封禁国外ip

nodejs的字符串操作模块_nodejs 字符串操作模块-程序员宅基地

文章浏览阅读3.2w次。nodejs字符串操作简介需要引入querystring对象,querystring对象的方法有stringifyquerystring.stringify(“对象”,“分隔符”,“分配符”),将一个json对象,转为字符串,通过指定的分隔符,以及分配符 具体代码:var querystring = require('querystring');var result = querystring.s_nodejs 字符串操作模块

李宏毅机器学习笔记第1周-机器学习基本概念_anomaly compression-程序员宅基地

文章浏览阅读855次。机器学习基本概念_anomaly compression

MD5碰撞-程序员宅基地

文章浏览阅读9.4k次,点赞29次,收藏109次。在CTF中可以说是经常碰到md5加密了,一般都是进行强比较抑或是弱比较,考法非常多,但是万变不离其中。只要我们掌握了原理,一切问题便迎刃而解了。文章首发于我的博客,格式可能比较清晰,有兴趣了解CTF中MD5碰撞的伙伴可以移步查看。_md5碰撞

普里姆算法c语言(详细解读)_c语言普里姆算法-程序员宅基地

文章浏览阅读854次,点赞5次,收藏12次。找到与这个系统邻接的边(0,1),(5,4),比较两者的权值,容易发现权值最小的为25,因此加入边(5,4),同时加入结点4和边(5,4)。4.将0,5,4,3以及相关的边看成一个整体,与其邻接的边有(0,1)28,(4,6)24,(3,6)18,(3,2)12,四个边中权值最小的边是(3,2),所以加入结点2以及边(3,2)。5.与4中所构成的整体邻接的边有(0,1)28,(4,6)24,(3,6)18,(2,1)16,四者中权值最小的边为(2,1),所以加入结点1以及边(2,1)。_c语言普里姆算法

nohub 和 & 在linux上不间断后台运行程序-程序员宅基地

文章浏览阅读3.1k次,点赞2次,收藏15次。长时间在服务器上运行深度学习代码,使用nohub 命令行 & 可以让代码不间断在后台运行_nohub

随便推点

docker配置国内镜像源_docker国内镜像源-程序员宅基地

文章浏览阅读3.3w次,点赞9次,收藏25次。刚开始学习docker,发现下载镜像非常的慢。如果不经过,docker的镜像下载都来源于国外,因此需要配置国内的镜像源。Docker中国区官方镜像。_docker国内镜像源

Unity中怎么播放视频_unity 播放视频-程序员宅基地

文章浏览阅读1.9w次,点赞40次,收藏209次。一.首先在场景中新建UI中的Raw Image可以按住Alt再点击下图红色箭头所示将Raw Image铺满游戏全屏(也可以自己调整大小)二.给Raw Image添加Video Player组件三.在Assets或者自己想要的文件夹中创建Render Texture四.将准备好的视频(这里用到的视频格式是mp4)拖入项目中并做如下修改这里我把新建的Render Texture命名为2,拖入的视频也命名为2(随便命的,不要在意)这里我们看到这个Render Te..._unity 播放视频

使用BOOTICE 恢复系统启动项_bootice保存后没用-程序员宅基地

文章浏览阅读9.7k次,点赞2次,收藏9次。使用BOOTICE 恢复系统启动项我在安装deepin 系统的时候,经常遇到重启进不去系统,每次重启都会进入windows 系统,这让我感到特别头疼,试了好多次都不成功,有些情况是,成功后再次重启又回到了windows系统。后来终于在PE中利用一款叫做BOOT ICE的工具成功解决。BOOTICE— 引导扇区维护工具简介BOOTICE 是一个启动相关的维护的小工具,主要用于安装、修复、备份和恢复磁盘_bootice保存后没用

文本分类与SVM_svm分类-程序员宅基地

文章浏览阅读9.5w次,点赞54次,收藏202次。之前做过一些文本挖掘的项目,比如网页分类、微博情感分析、用户评论挖掘,也曾经将libsvm进行包装,写了一个文本分类的开软软件Tmsvm。所以这里将之前做过一些关于文本分类的东西整理总结一下。1 基础知识1. 1 样本整理文本分类属于有监督的学习,所以需要整理样本。根据业务需求,确定样本标签与数目,其中样本标签多为整数。在svm中其中如果为二分类,样本标签一般会设定为-1和_svm分类

力扣——206.反转链表_力扣链表反转-程序员宅基地

文章浏览阅读141次。题目python代码方法一:利用新列表,创建新的链表# Definition for singly-linked list.# class ListNode(object):# def __init__(self, val=0, next=None):# self.val = val# self.next = nextclass Solution(object): def reverseList(self, head): ""_力扣链表反转

如何解决深度冲突(Z-fighting),画面闪烁的问题-程序员宅基地

文章浏览阅读3.6k次,点赞3次,收藏6次。参考:OpenGL教程:深度测试深度冲突一个很常见的视觉错误会在两个平面或者三角形非常紧密地平行排列在一起时会发生,深度缓冲没有足够的精度来决定两个形状哪个在前面。结果就是这两个形状不断地在切换前后顺序,这会导致很奇怪的花纹。这个现象叫做深度冲突(Z-fighting),因为它看起来像是这两个形状在争夺(Fight)谁该处于顶端。防止深度冲突第一个也是最重要的技巧是永远不要把多个物体摆得太靠近,以至于它们的一些三角形会重叠。通过在两个物体之间设置一个用户无法注意到的偏移值,你可以完全避免这两个物体之_深度冲突