直接说正题,帮助一下刚刚入门的朋友们,也算是学习IC设计...我们这里只讨论数字电路设计。实际上就是如何把我们从课堂上学到的逻辑电路使用原理图(很少有人用这个拉),或者硬件描述语言(Verilog/VHDL)来实现,或许...

”数字电路设计“ 的搜索结果

本实验用于数字电路实验设计,包括设计思路,以及设计实物图,仿真波形图。也有实验结果,上传者为湖南师范大学工程与设计学院电子系。

数字电路设计实验-简易密码锁.pdf数字电路设计实验-简易密码锁.pdf数字电路设计实验-简易密码锁.pdf数字电路设计实验-简易密码锁.pdf数字电路设计实验-简易密码锁.pdf数字电路设计实验-简易密码锁.pdf数字电路设计...

探索Verilog:数字电路设计的新里程 项目地址:https://gitcode.com/seldridge/verilog 项目链接 在电子工程和计算机科学领域,Verilog是一种强大的硬件描述语言(HDL),用于设计、模拟和验证复杂的数字系统。通过...

数字电路-时序逻辑电路

标签: 时序逻辑电路

数字电路的设计方法与技术

标签: 硬件架构

本页只是主要来自于硬件架构的艺术这本书。

常见数字电路模块设计,仅自学使用

(6) 在要求(5)的基础上,可利用八段数码管替代LED灯,或增加LED灯数量,构成LED阵列等,实现数字或文字的时间控制显示电路(此要求为选做)。(2) 以移位寄存器为核心器件,自主设计一套基于时钟信号的跑马灯...

有助于更好理解数字电路中的组合逻辑电路

总结而言,通过Verilog语言在FPGA中实现各种应用数字电路的步骤包括准备工作、创建项目、创建模块、连接模块、生成比特流文件、配置FPGA以及测试和调试。实现这些步骤需要掌握Verilog语言的语法和概念,理解电路的...

数字电路这一块最近见识到了UCSD(加州大学)的国际一流水准的课程,深受震惊,所以打算从这里开始,但这个教程还是属于提纲性的,不会把用到的每个东西都解释清楚,但我会告诉大家需要哪些知识。 本系列打算开如下...

五、设计内容: (1) 以555定时器为核心器件,自主设计一套时钟... (6) 在要求(5)的基础上,可利用八段数码管替代LED灯,或增加LED灯数量,构成LED阵列等,实现数字或文字的时间控制显示电路(此要求为选做)。

探索数字电路设计的新纪元:Logisim-Evolution 项目地址:https://gitcode.com/logisim-evolution/logisim-evolution Logisim-Evolution 是一个强大的、开源的数字逻辑电路设计与模拟软件。它基于原始的 Logisim 项目...

数字电路 1、同步电路和异步电路的区别是什么?(仕兰微电子) 2、什么是同步逻辑和异步逻辑?(汉王笔试) 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 3、什么是...

1数字电路设计流程与SOC芯片架构图

标签: 芯片

ASIC和SOC设计的流程相近。ASIC主要是在PC端,现在SOC是主流。 一、需求分析 产品要解决什么问题,预测未来3-5年的走势和趋向,确保芯片是有卖点和前瞻性,面向未来。 客户向fabless提出设计要求,包括芯片需要...

*单片机设计介绍,基于数字电路演讲计时protues仿真设计。

*单片机设计介绍,基于数字电路八路抢答器仿真设计。

数字电路设计,数字电路设计

标签: 数字电路设计

数字电路设计 数字电路设计 数字电路设计 数字电路设计

*单片机设计介绍,基于数字电路的彩灯控制器系统设计。

*单片机设计介绍,基于数字电路的音响放大器Proteus仿真设计。

日本学者编写的数字电路设计与安装方面的书籍。

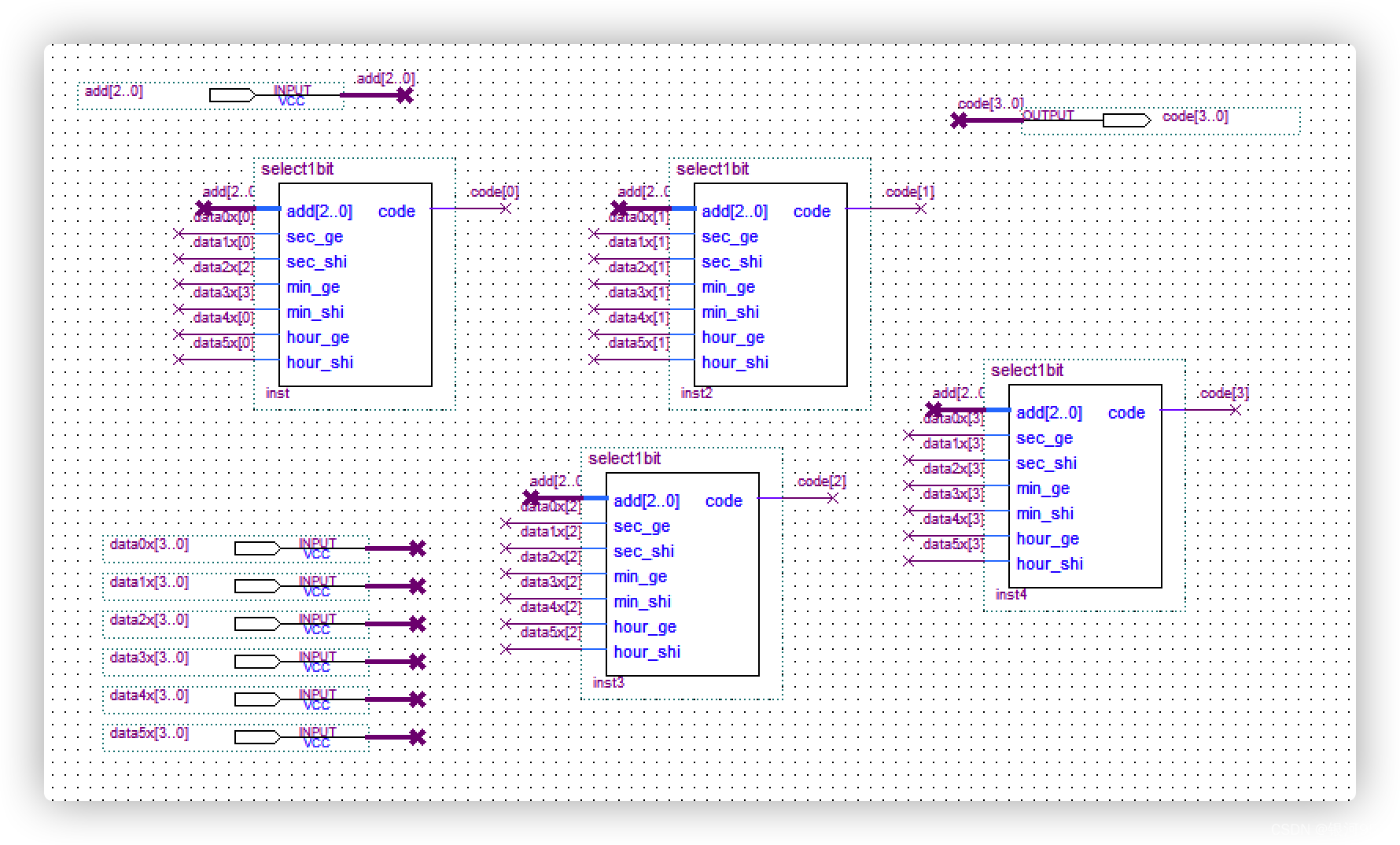

数字电子钟是一种用数字电路设计实现的时分秒计时的装置,它与机械式的时钟相比,具有更高的,准确的和直观性,且无机械装置具有更长的使用寿命。从原理上讲,数字电子钟是一种典型的数字电路,其中包括了组合逻辑...

数字电路设计:竞争冒险以及消除方法 竞争冒险 在设计数字电路过程中,往往会忽略组合逻辑中各个路径存在延迟。 (1)竞争:对于同一个模块中的同一个变量,可能会有正反输入的情况,而这两个信号来自不同的路径。 ...

适合于数字电路设计,关于数字电路和模拟电路设计的典型电路的设计方法

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地