FPGA/CPLD简介 一、可编程逻辑器件主要有两个类型: (一)、现场可编程门阵列(FPGA)(Field Programmable Gate Array) (二)、复杂可编程逻辑器件(CPLD)(Complex Programmable Logic Device) 二、FPGA...

”fpga/cpld“ 的搜索结果

《Altera FPGA/CPLD设计(高级篇)(第2版)》是一本针对FPGA/CPLD设计的进阶教材,主要介绍了复杂的FPGA/CPLD设计、高级的硬件描述语言和设计方法。 本书从FPGA和CPLD的基础入手,系统地介绍了各种FPGA/CPLD的设计...

《Altera FPGA/CPLD设计基础篇(第2版)》是一本介绍使用Altera公司的FPGA/CPLD开发工具进行硬件设计的基础指南。本书内容包括FPGA/CPLD的基础知识、Quartus II的使用方法、设计调试和仿真等。 本书通过实例讲解了...

可编程逻辑器件FPGA/CPLD原理.结构与描述语言详解。

Altera FPGA/CPLD设计是指使用Altera公司的FPGA(现在被英特尔收购)和CPLD芯片进行数字电路设计。FPGA是可编程逻辑器件,可以根据用户的需求进行编程,实现各种数字电路功能。CPLD是复杂可编程逻辑器件,也可以实现...

FPGA(现场可编程逻辑门阵列)和 CPLD(可编程逻辑门阵列)是数字电路设计中常用的可编程逻辑器件。它们的设计流程大致包括以下几个步骤: 1. 需求分析:根据项目需求,确定逻辑电路的功能和性能指标,例如时序、...

完整的《Xilinx ISE 9.x FPGA/CPLD设计指南》开发资料,若不能下载请留言

基于Altera FPGA/CPLD的电子系统设计及工程实践 第7,10,11源代码

Altera_FPGA_CPLD设计基础篇 高级篇(第2版高清).part3

根据FPGA 和CPLD 器件的结构特点,提出了利用VHDL硬件描述语言对FPGA和CPLD器件进行开发时应注意的事项和一些经验技巧,供广大电子设计师参考。

FPGA加密技术,CPLD加密技术,CPLD实现FPGA加密等

配套的光盘,好像很难找到,上传给大家用吧!

Altera FPGA/CPLD基础篇设计光盘例程

Altera FPGA/CPLD设计 基础篇 EDA先锋工作室编著 人民邮电出版社

特权的《FPGA/CPLD边练边学—快速入门Verilog/VHDL》配套例程。

做了一个月的文档,收集了很多的资料,希望能帮到你们。

FPGA中消除毛刺的常用方法是: 1.触发器输出 通过添加触发器,使输出信号在clk跳变沿进行读取,并输出,能有效地降低毛刺的发生几率。但这样的话,延时也就增大。但是,毛刺的产生是不定时的,如果毛刺在时钟跳变...

据说是不错的书,altera公司参与编写的,应该挺好的,贡献给大家

期末试卷

好东西 分享下,下载个东西真心好难啊,以后会多上传些免费的东西给大家。要分时没办法啊

1、设计规范到VHDL描述 根据最终设计所期望的描述,构造一个合理的设计,自然语言编写。 形成规范后,通过数学公式或逻辑公式进行抽象的描述。 再用硬件描述语言将其转化为RTL级的描述 ...使用表达设计环境的激励...

Altera FPGA CPLD基础篇 PDF文档,不包含光盘内容

本文基于Quartus II 13.0版本举例说明原理图编辑的流程。 1 .建立新的工程 1). 指定工程名称:File->New Project Wizard打开向导对话框,选择工程路径和填写工程名和实体名(工程名和实体名相同),如下图 ...

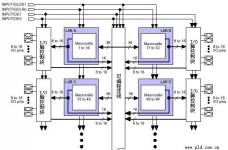

设计一种基于MCS51单片机与FPGA/CPLD的总线接口逻辑电路,实现单片机与可编程逻辑器件数据与控制信息的可靠通信,使可编程逻辑器件与单片机相结合,优势互补,组成灵活的、软硬件都可现场编程的控制系统。...

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是: 将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列、Altera的MAX7000S系列和Lattice(原Van...

基于Altera FPGA/CPLD的电子系统设计及工程实践 作者名称:刘延飞 郭锁利 王晓戎 李琪 常春藤 人民邮电出版社

第一章 FPGA/CPLD概述 第二章 ALTERA可编程逻辑器件 第三章 HS102型FPGA/CPLD实验板 第四章 Max+plusII10.2的使用 第五章 Quartus4.2软件的使用 第六章 HS101型FPGA/CPLD实验板设计实例

推荐文章

- Python Django 版本对应表以及Mysql对应版本_django版本和mysql对应关系-程序员宅基地

- Maven的pom.xml文件结构之基本配置packaging和多模块聚合结构_pom <packaging>-程序员宅基地

- Composer 原理(二) -- 小丑_composer repositories-程序员宅基地

- W5500+F4官网TCPClient代码出现IP读取有问题,乱码问题_w5500 ping 网络助手 乱码 send(sock_tcps,tcp_server_buff,-程序员宅基地

- Python 攻克移动开发失败!_beeware-程序员宅基地

- Swift4.0_Timer 的基本使用_swift timer 暂停-程序员宅基地

- 元素三大等待-程序员宅基地

- Java软件工程师职位分析_java岗位分析-程序员宅基地

- Java:Unreachable code的解决方法_java unreachable code-程序员宅基地

- 标签data-*自定义属性值和根据data属性值查找对应标签_如何根据data-*属性获取对应的标签对象-程序员宅基地