当第一代RISC微处理器刚出现时,标准存储器元件的速度比当时微处理器的速度快。很快,半导体工艺技术的进展被用来提高微处理器的速度。标准DRAM部件虽然也快了一些,但其发展的主要精力则放在提高存储容量上。 ...

”高速缓冲存储器Cache“ 的搜索结果

高速缓冲存储器Cache的原理、设计及实现 更多资源请访问http://www.59186618.com

PC系统高速缓冲存储器Cache的原理、设计及实现

高速缓冲存储器(Cache) 相关知识介绍

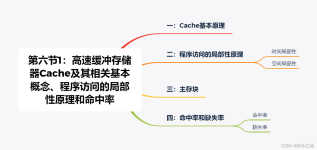

cpu欲访问的信息在cache中的比率称为cache的命令率。为了提高访问效率,命中率H越高(越接近1)越好。一个程序执行期间,cache的总命中次数为。设cpu采用同时访问cache和主存的策略。设cpu采用同时访问cache和主存的策略...

cache是一种小容量高速度的sram存储器,用于匹配cpu的存取速度,在cpu和主存之间。根据局部性原理,将逻辑或空间相邻的部分数据先存入cache与cpu通信。

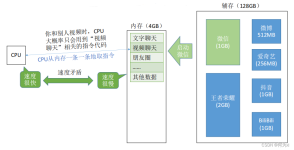

因为写入主存速度慢,所以一般不直接写入主存,而是写入“写缓冲区”,由“写缓冲区”将信息逐一写入主存。CPU读取数据时,将逻辑地址拆分为逻辑页号和页内地址,找到逻辑页号在页表中对应的主存块号,与页内地址...

选择题1、对于二进制码10000000,若其表示的真值为-128,则它是()表示的A)原码B)反码C)补码D)移码2、在()表示中,二进制数11111111表示的十进制数-1A)原码B)反码C)补码D)移码3、8位二进制补码的表数范围为()A)-127-+...

高速缓冲存储器cache介绍

标签: cache

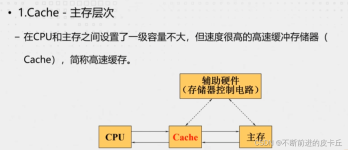

为了解决存储器系统的容量、存取速度及单位成本之间的矛盾,可以采用 Cache- 主存存储结构,即在主存和 CPU 之间设置高速缓冲存储器 Cache ,把正在执行的指令代码单元附近的一部分指令代码或数据从主存装入 Cache...

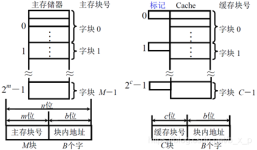

任何时刻都有主存块处在缓存块中,CPU想访问主存某字时,有两种可能,一种是所需的字已在缓存中,直接访问cache(CPU与cache之间通常一次传输一个字),另一种是所需的字不在cache中,此时需将该字所在的主存整个字...

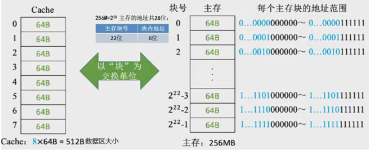

缓存是计算机系统中常见的一种高速存储器,用于临时存储常用数据,以便快速访问。在缓存中,有三种常见的映射方式,分别是直接映射、全相联映射和组相联映射。

正确答案: B高速缓冲存储器(Cache.一般采用DRAM构成题目:下列叙述中,错误的是解析:即高速缓冲存储器是位于CPU和主存储器DRAM(Dynamic RAM)之间的规模较小的但速度很高的存储器,通常由SRAM组成。举一反三的答案...

文章目录1.0 概述1.1 为什么用Cache?1.2 Cache的工作原理1.3 Cache的基本结构1.4 Cache的...我在前面总结存储器的时候有写到过出现Cache的背景, 1.2 Cache的工作原理 1.3 Cache的基本结构 1.4 Cache的读写操作 1...

缓存的写策略指的是确定何时将数据写入缓存或主存的策略。

缓存替换算法用于确定在缓存满时需要替换哪些缓存块以便为新的数据腾出空间。

Cache引用原因 cpu空等现象:IO设备与cpu都需要访问内存,IO设备优先级较高,速度较慢,因此cpu需要等待IO访问内存从而出现空等现象。将热点数据缓存在Cache中可以有效避免cpu空等现象,直接从缓存中访问数据; ...

简要了解cache

高速缓冲存储器 问题的提出 CPU空等问题 ...因此出现了Cache高速缓冲存储器。CPU可以不直接访问主存,而与高速的Cache交换信息。 程序的局部性原理 时间局部性:当前正在使用的指令和数据在不久的将来还会被使

(1)在多体并行存储系统中,由于I/O设备向主存请求的级别高于CPU访存,这就出现了CPU等待I/O设备访存的现象,...(2)主存速度的提高始终跟不上CPU的发展,Cache的出现也是为了解决主存与CPU之间速度不匹配的问题。

高速缓冲存储器⭐ cache出现的原因: 避免速度差造成的拥堵 时间局部性:未来要用到的信息可能是我现在正在用的信息 空间局部性:未来要用的信息,从存储角度说,可能在我正在用的信息的附近 所以我把正在使用的信息,和...

本文主要是针对存储系统中高速缓冲存储器Cache进行练习。

Q:怎么判断此时要存储的cache行内是否存在数据呢? A:可以通过设置有效位来判断cache行内是否有数据存在。 Q:还有一个问题,因为我们是在cache内随机存储的,那么该怎么判断这一行数据是代表主存里的哪行数据? A:...

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地