”系统时钟“ 的搜索结果

系统时钟的设计

标签: 系统时钟的设计 其它

在设计FPGA时,有时需要将整块板或整个系统的时钟综合起来考虑,本节主要介绍系统时钟的设计。 芯片之间互连时,有源同步和系统同步两种方式。无论采用何种同步方式,在需要调整时钟数据相位时,应参考DOM和PLL...

实验报告_实验5CC2530系统时钟的设置共3页.pdf.zip

在页面特定地方调用系统时钟,显示时间。是web页面开发经常用到的小工具。

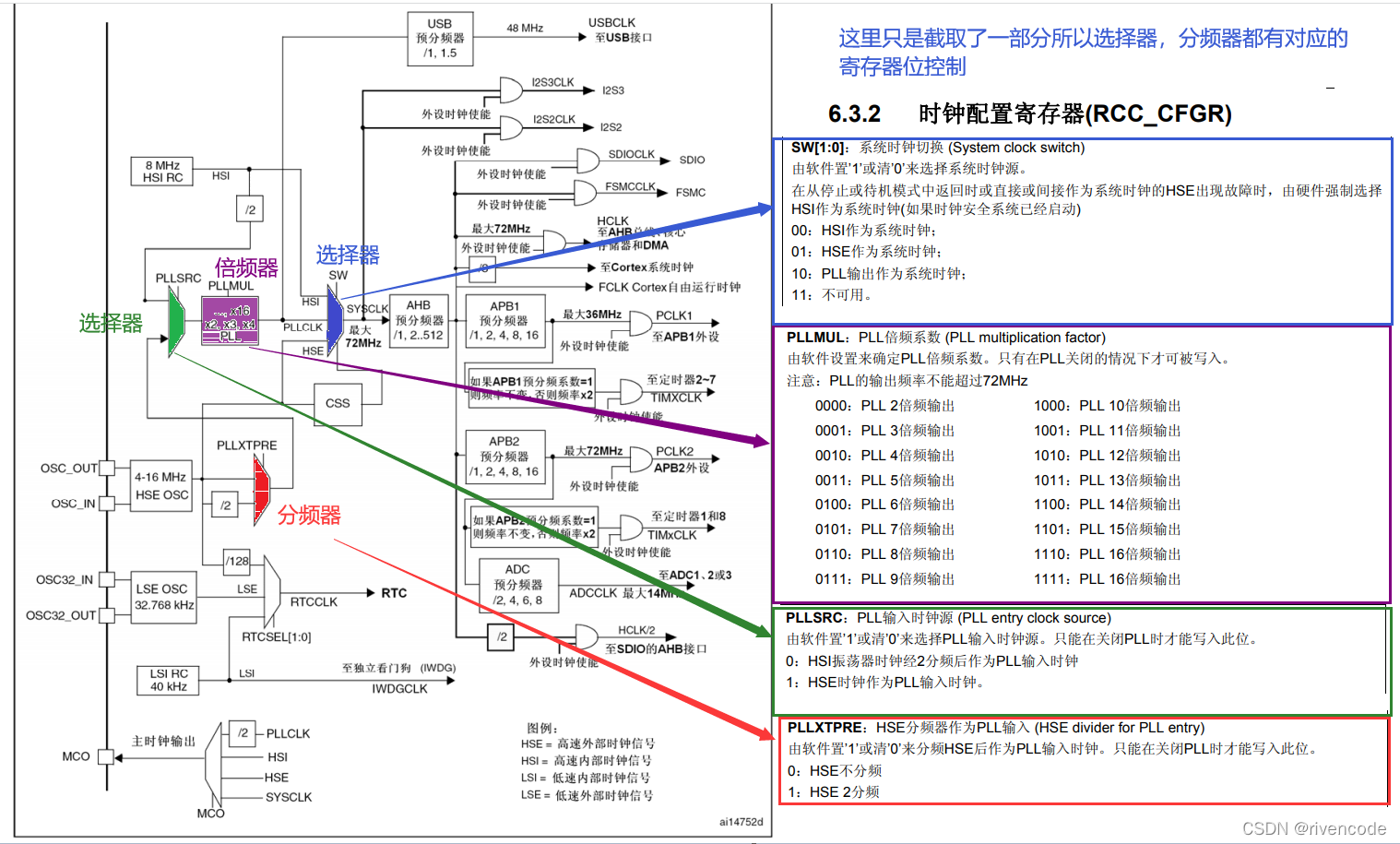

由系统时钟SYSCLK分频得到,一般不分频,等于系统时钟,HCLK是高速外设时钟,是给外部设备的,比如内存,flash。时钟发生器(Clock Generator):时钟发生器接收振荡器提供的时钟信号,并根据需要生成其他频率的时钟...

中文名系统时钟释义基于CMOS工艺的高性能处理器特点集成PLL可以从内部触发性能设计频率为200MHz系统时钟定义语音通常所说的系统时钟就是指时钟系统,它是由振荡器(信号源)、定时唤醒器、分频器等组成的电路。...

时钟的相关概念、时钟源、时钟安全系统(CSS),F411时钟树讲解、F411CubeMX时钟讲解、配置系统时钟流程及代码分析

FreeRTOS_时间管理

STM32系统时钟默认设置

4.配置系统时钟思路及方法

标签: 单片机

一个时钟树一般先对复杂,我们先调出主频(及编程好时钟源、PLL倍频这一部分)其他的之后再说,如此编程才不会太复杂。实际上这个一般厂家会给一个配置文件的,但是如果要自己做些超频之类的操作,就要彻底掌握时钟...

STM32的时钟系统比较复杂,初学者一看时钟树必然蒙圈,我该怎么用?怎么设置?搞不懂,就根据开发板源码很快完成设置,虽然能用起来,碰到问题或自己改代码时必然蒙圈。要做好底层驱动设计,还是要对STM32的时钟有...

每次进入系统时钟节拍服务等待表和就绪表更新后,若有更高优先级任务就绪,操作系统内核将启动任务切换。/* 等待表为空 则将xNextTaskUnblockTime赋值成最大值 *//* 设置任务切换标志 *//* 设置任务切换标志 */)/* ...

STM32本身十分复杂,外设非常多 但我们实际使用的时候只会用到有限的几个外设,使用任何外设都需要时钟才能启动,但并不是所有的外设都需要系统时钟那么高的频率,为了兼容不同速度的设备,有些高速,有些低速,如果...

时钟是单片机运行的基础,

系统时钟分析配置与定时器实战,工程创建经验与架构经验,主要是为了实际应用所设定,没有太多原理介绍,主讲实战。

学习系统时钟架构和时钟树,验证及学习笔记如下,如有错误,欢迎指正。主要记录了总线下挂载外设,总线时钟源以及系统时钟的配置。

用硬件时钟同步系统时钟: 用系统时钟同步硬件时钟: 同步网络时间 查看和修改Linux的时间 时钟--详解 硬件时钟 系统时钟 时间同步 时间标准 网络时间 ntp时钟同步服务 chrony时钟同步服务 备注 ntp...

SysTick(System Timer)是一种系统计时器,它是一个24位只能向下递减的计数器(计数器每计数一次的时间为1/SYSCLK),通常用于嵌入式系统中,用于提供基本的系统定时和时钟服务。SysTick定时器是ARM Cortex-M处理器...

以上三种,可选择一种作为系统时钟。系统时钟最大频率不能超过72MHz。2、等待外部高速时钟HSE准备就绪。9、等待PLL作为系统时钟设置成功。5、FLASH延时两个周期。8、选择PLL作为系统时钟。4、设置PLL倍频器。

推荐文章

- 反编译delphi_反编译Delphi(1/3)-程序员宅基地

- node_acl用法示例_node acl-程序员宅基地

- 使用STM32提供的DSP库进行FFT_stm32的dsp库 直流分量-程序员宅基地

- VScode 报错 :crbug/1173575, non-JS module files deprecated._crbug/1173575是什么原因-程序员宅基地

- C++学习_3-程序员宅基地

- eigen 构造变换矩阵(Eigen::Isometry3d或者Eigen::Matrix4d)的几种方式-程序员宅基地

- C++ 如何初始化静态类成员(静态成员必须在.cpp文件中初始化)_c++ 静态成员变量初始化-程序员宅基地

- 48,原子核物理实验方法篇_短时间的高剂量照射后果-程序员宅基地

- el-dialog修改默认内边距_el-dialog__body修改padding-程序员宅基地

- 公网下远程树莓派Raspberry Pi的SSH/WOL/监控/桌面的实现_ssh wol-程序员宅基地