时序约束和时序分析在FPGA开发和数字IC设计中是重要的概念,本文主要阐述数字电路中时序路径基本概念和时序约束的基本分析方法

”时序约束“ 的搜索结果

1)【抢先版】小梅哥FPGA时序约束从遥望到领悟.pdf 2) 通向FPGA之路---七天玩转Altera之时序篇V1.0.pdf 3) Verilog_HDL_那些事儿_时序篇v2.pdf 4) Altera时序分析模型及同源系统的时序约束方法.pdf

主时钟通常是FPGA器件外部的板级时钟(如晶振、数据传输的同步时钟等)或FPGA的高速收发器输出数据的同步恢复时钟信号等。

如果约束S为0,不存在...set_false_path是不对路径进行时序处理,时序弧仍有效,如果该时序弧相关的时序路径有多条,伪路径只作用于部分路径,时序工具会计算所有时序路径,但只对存在时序约束的时序路径进行分析。

触发器是一种只能存储1个二进制位(bit)的存储单元,可以用作时序逻辑电路的记忆元件,FPGA逻辑元件内的D触发器,在CLK信号(时钟)的上升沿将输入值传送至输出Q。...保持时间(Th:hold time)为什么要做时序约束?

时序约束教程

XILINX 时序约束使用指南笔记 ——时序约束介绍 时序约束方法 时序约束原则等

小梅哥FPGA时序约束从遥望到领悟详解

FPGA时序约束、时序分析[归纳].pdf

时序约束与时序分析系列博客,完整版PDF指导文件。博客地址: https://blog.csdn.net/qq_33486907/article/details/89380368

正点原子FPGA静态时序分析与时序约束_V1.0.pdf

时序约束是fpga设计中最基本也是最重要的步骤之一,也是难点之一。

从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下: 0. 核心频率约束 这是最基本的,所以标号为0。 1. 核心频率约束+时序例外约束 时序例外约束包括...

4 时序约束与时序分析.pdf

标签: 时序约束

时序约束与时序分析

FPGA的时序分析与约束需要设计者根据实际的系统功能,通过时序约束的方式提出时序要求;FPGA编译工具根据设计者的时序要求,进行布局布线;编译完成后,FPGA编译工具还需要针对布局布线的结果,套用特定的时序模型,...

FPGA时序约束与分析

标签: fpga开发

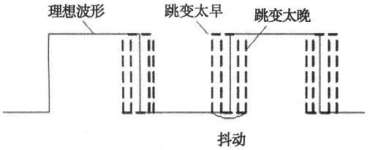

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。 1.时钟相关 时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真...

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下

很好的数字IC后端时序约束问题汇总,非常详细。

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现FPGA 设计的...

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

推荐文章

- Java---简单易懂的KNN算法_jf.knn-%; 9 &-程序员宅基地

- 最新版ffmpeg 提取视频关键帧_从视频中获取flag-程序员宅基地

- 【ARM Cache 系列文章 11 -- ARM Cache 直接映射 详细介绍】

- Objective-C学习计划

- 【数据结构】最小生成树(Prim算法、Kruskal算法)解析+完整代码

- python访问组策略_python 模块 wmi 远程连接 windows 获取配置信息-程序员宅基地

- html把div做成透明背景,DIV半透明层 CSS来实现网页背景半透明-程序员宅基地

- 关机恶搞小程序

- mnist手写数字分类的python实现_TensorFlow的MNIST手写数字分类问题 基础篇-程序员宅基地

- wxpython窗口跳转_WxPython-用按钮打开一个新窗口-程序员宅基地