数字IC前端后端设计流程,本文档主要讲述了数字IC的设计的流程,包括前端设计和后端设计的详细步骤。

”数字IC“ 的搜索结果

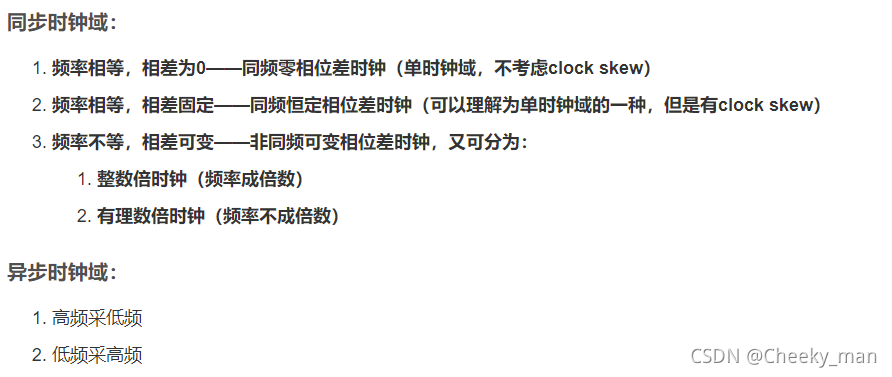

在集成电路进入深亚微米阶段,决定时钟频率的主要因素有两个,一是组合逻辑部分的最长电路延时,二是同步元件内的时钟偏斜(clock skew),随着晶体管尺寸的减小,组合逻辑电路的开关速度不断提高,时钟偏斜成为影响...

华为2021-2023年数字IC笔试真题

数字IC设计前端推荐设计

标签: 前端

数字前端rtl风格很重要,因为综合工具对不同的编码风格解释的结果是不一样的,这会影响到设计门数和时序性能。下面推荐的一些基本设计技术,可以确保得到优化的设计结果,同时避免不可靠和不稳定性。

高级数字ic.docx

标签: 数字ic

期末复习同步时序逻辑的优点 冒险不会影响功能 (时钟和异步复位除外) 电路中所有节点在存储操作时都已稳定。 在正确设计的电路中不会存在时序违规,免于亚稳态现象。 在设计时只需要考虑极少的时序约束。

数字ic设计自学ing

标签: 数字ic

为方便快速进行查找该专栏的内容,将所有内容链接均放在此篇博客中整理不易,欢迎订阅~~

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第六套

数字电路目前几乎都是CMOSIC,如果局限于此,则如图1所示,与IC的输人端子相串联,插人限流电阻R即可。当然,接受外部信号时应使用施密特型IC。 图1 CMOS逻辑电路的限流电阻 这种电路采用74系列用HS CMOS...

2018年各个公司数字IC工程师岗位设计的笔试题,如寒武纪,联发科,紫光,中兴,海康威视,科达,忆芯等等.....

11、32bit位宽 128bitAHB和APB需要传输多少周期。14、AXI的outstanding和乱序传输如何理解。10、项目都是今年的 SV和UVM学了多久。15、flash、sram、dram的区别。12、AHB的error信号有哪几种。10、AHB和APB协议的...

汇总整理在面试过程中常见的问题,如果都能回答下来,那么面试肯定不成问题的。

数字IC设计工程师面试100题.docx

数字IC笔试面试常考问题及答案

标签: IC

4、假如复位不同步怎么办,master先复位,发送数据,slave端还没有复位。6、 第三段输出组合逻辑或时序逻辑,分别根据什么进行判断。8、 跨时钟域单bit由快到慢,多bit跨时钟域的方法。询问家庭情况,老家哪里,几个...

15、ahb写或者读的数据存储起来了嘛,ahb读的话,apb这边是怎样的。19、覆盖率收集的时候有没有哪些是很难收集到的,然后写了定向测试。2、C++有学过嘛 还记得C++的什么内容 C++成绩多少。12、config_db机制用过嘛 ...

亚稳态是在数字IC设计中常见的问题,该文件主要是阐述了亚稳态产生的原因、危险以及相应的解决方案电路。

数字IC系统设计.pdf

标签: 数字IC设计

内容清新,数字IC设计必备工具书籍。

技术栈比较搭,基本用过的东西都是一模一样的。快手终面喜欢问智力题,校招也是终面问智力题,大家要准备一下一些经典智力题。如果排列组合、概率论这些基础忘了,建议回去补一下。网上学习资料一大堆,但如果学到的...

基于FPGA的BRAM资源实现多读多写RAM

21ic下载_《FPGA&数字IC开发工程师》笔试100题 的充值学校宣传传输层 早点睡多多多多多多多多多多多

数字IC笔试面试汇总

标签: 数字IC 笔试面试

该文档主要包括 海思、联发科、芯原、复旦微电子等公司的部分笔试面试题汇总

本资源为2020届大疆数字IC笔试题目,本人对文档中的题目进行了解答和注释,大部分题目应该都是对的,欢迎大家下载讨论

收录近500篇数字IC博客文章!DEMO版! 方向:数字IC学习路线,通用技能篇,数字电路,硬件描述语言(Verilog),linux操作系统,C语言微机原理,汇编语言,计算机组成原理,计算机体系架构,STA,SystemVerilog,UVM,...

数字IC与模拟IC到底哪个更适合你?

各大公司招聘笔试题汇总 数字ic fpga面试题目100道,硬件工程师面试题

思朗科技,2022提前批,数字IC验证,笔试题:异步FIFO的UVM环境搭建及验证。 给了一个异步FIFO的代码工程,要求自己搭建UVM验证环境去验证这个设计,结果包括覆盖率收集以及错误点等等。 适合2023届目标IC验证领域的...

数字IC设计面试笔试题,详细准确,帮助你快速入门

fpga数字ic开发工程师资料笔试100题.doc

推荐文章

- php 上传图片 缩略图,PHP 图片上传类 缩略图-程序员宅基地

- scrapy爬虫框架_3.6.1 scrapy 的版本-程序员宅基地

- 微信支付——统一下单——java_小程序统一下单接口-程序员宅基地

- (已解决)报错 ValueError: Tensor conversion requested dtype float32 for Tensor with dtype resource-程序员宅基地

- 记录el-table树形数据,默认展开折叠按钮失效_eltable一刷新展开的子节点展开按钮消失-程序员宅基地

- 设计模式复习-桥接模式_csdn天使也掉毛-程序员宅基地

- CodeForces - 894A-QAQ(思维)_"qaq\" is a word to denote an expression of crying-程序员宅基地

- java毕业生设计移动学习网站计算机源码+系统+mysql+调试部署+lw-程序员宅基地

- 14种神笔记方法,只需选择1招,让你的学习和工作效率提高100倍!_1秒笔记 高级-程序员宅基地

- 最新java毕业论文英文参考文献_计算机毕业论文javaweb英文文献-程序员宅基地