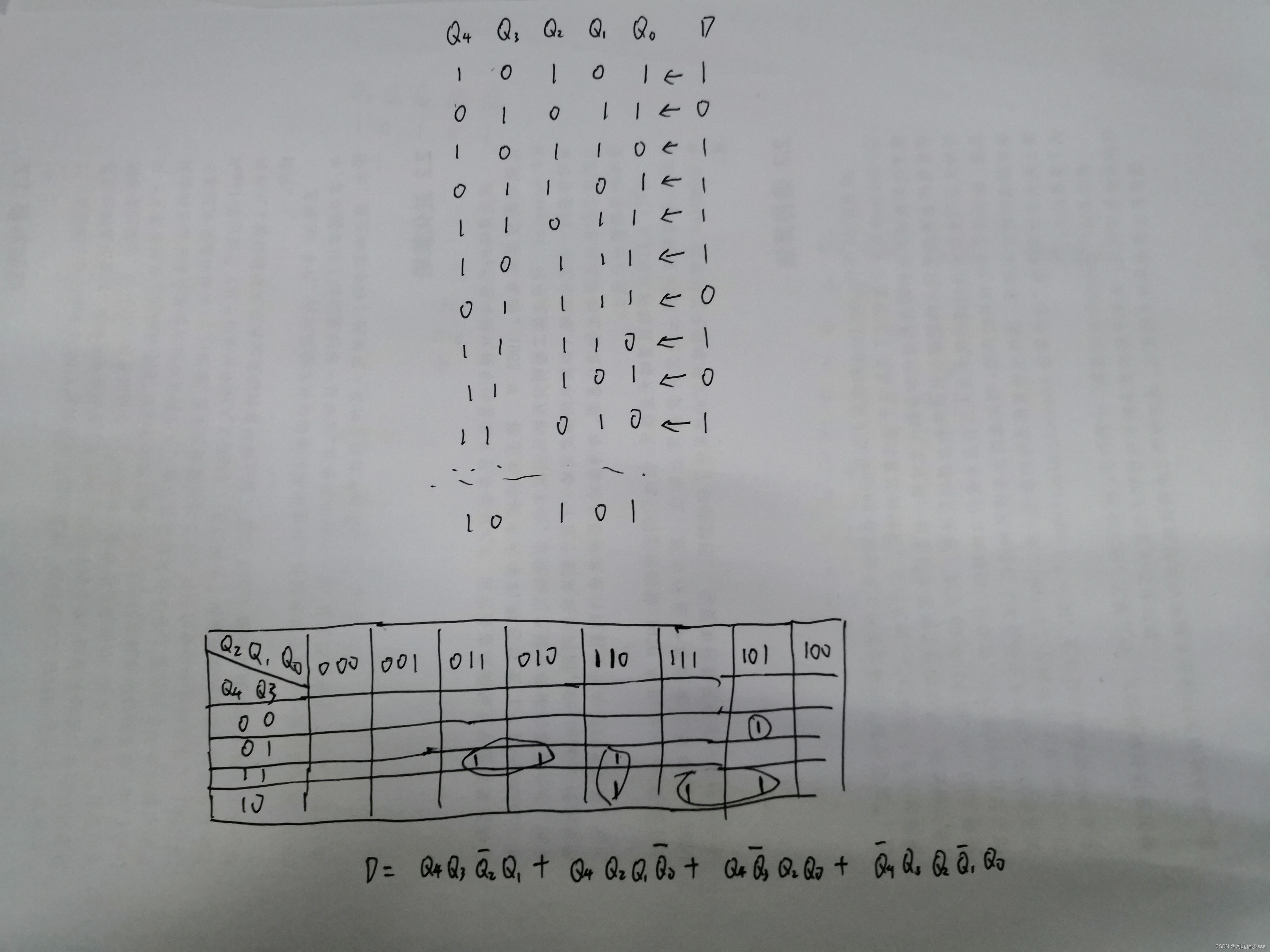

计数型序列信号发生器能产生多组序列信号,这是移位型发生器所没有的功能.计数型序列信号发生器是由计数器和组合电路构成的。 本实验的目的就是设计一个序列信号发生器。设计产生序列11100100、11100100、···...

”序列信号产生器“ 的搜索结果

能产生这种信号的逻辑器件就称为序列信号发生器.根据结构不同,它可分为反馈移位型和计数型两种. 1、移位型序列信号发生器 1.移位型序列信号发生器的组成 移位型序列信号发生器是由移位寄存器和组合电路两...

用一个不断循环的状态机,循环...直接给出verilog HDL设计代码://有限状态机方式实现001011序列信号产生器 module sequence_signal_fsm(clk, rst_n, dout); input clk, rst_n; output dout; reg dout; ...

本次主要介绍一下关于EDA的实验:序列信号发生器,包括两种考虑分频和不考虑分频的模12计数器型序列信号发生器、以及长度为N的序列信号发生器。

SOS电路是一种简单而重要的电子电路,用于产生和传输紧急信号。我们将介绍SOS电路的连接思路,包括所需的组件选择以及信号的连接方式。

能产生这种信号的逻辑器件就称为序列信号发生器.根据结构不同,它可分为反馈移位型和计数型两种. 1、移位型序列信号发生器 1.移位型序列信号发生器的组成 移位型序列信号发生器是由移位寄存器和组合电路两...

用计数器和数据选择器配合产生序列信号 110100。 实验设备与器材 1.实验组合箱一台 2.74LS000 四二输入与非门一片,74LS153 一片,74LS161 一片

Verilog实现序列信号发生器

标签: fpga

VHDL产生序列信号发生器

标签: fpga开发

VHDL产生序列信号发生器,产生“01111110”的序列

混沌信号发生器-用于产生各种混沌序列,能够实现分岔、周期、混沌等现象的演示

一、状态转移型的序列信号产生器的verilog HDL 设计用一个不断循环的状态机,循环产生序列信号001011。过程过于简单,我就不画状态图了。直接给出verilog HDL设计代码://有限状态机方式实现001011序列信号产生器 ...

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种伪随机序列。是由移位寄存器、反馈抽头及模2加法器组成。m序列一旦反馈多项式及移位寄存器初值给定,则就是可以预先...

序列信号1011101共7位, 则电路共需要7个有效状态: 可先用同步置数法将74LS161设计为同步7进制计数器. (由于multisim7中只有74163, 故这里用74163替代74161) 如此设计后, 电路共有7个状态(都是有效状态)0000、0001、...

本电路总体的设计方法,可以参照教材,“照葫芦画瓢”,可以说并不算太难。但是在模拟软件上连接电路时,出现了诸多问题,导致花费了大量时间和精力。第一,两个元件在连接过程中,看起来是接在一起了,实际上是断开...

1001序列检测器实验报告,内含modelsim仿真代码和测试代码,Multisim仿真截图。

verilog产生01011011101111…序列 模块 //function module module test0 ( input clk, input rst, output q ); parameter S0=1'b0, S1=1'b1; reg state; reg [7:0] run,des; always@(posedge clk) if(rst) ...

本次课程设计的内容为串行序列信号延时测试系统,首先需要明晰其整体需要实现的功能:本测试系统送出串行的序列信号,该串行序列信号经过延时电路产生一定的延迟时间以后送到了接收电路,系统收到信号以后会根据接收...

序列信号发生器的设计

标签: 信号发生器的设计

了解序列信号发生器的原理,掌握原理图和语言描述的层次设计方法

安捷伦科技(Agilent Technologies)宣布推出业界最快速的序列脉冲数据产生器Agilent 81142A,能产生高达13.5 GHz的激发信号。可为新的高速序列总线设计,以及从事基础实验研究的科学家,提供可靠的精确度高、...

序列信号发生器,能在clk信号作用下周期性输出“0010110111”这是采用寄存器模型 思路:几位数字就是几位的寄存器,写一个10位的寄存器,先输出最高位,左移一位,并将输出赋给低位进行循环 //序列检测器 周期性的...

之前我们已经学习过该如何使用74160/74163实现序列信号发生器的方法, 下面我们再学习另一种实现序列信号发生器的设计方法——这种方法比用74160/74163加门电路/74151/74153的设计方法难度要大, 须大家仔细推敲. ...

对于序列信号001010, 选择四位: 0010->0101->1010->0100->1000->0001->0010->...... 无重复状态, 则选择该种设计方案(若选择三位会产生重复状态). 由此, 得到状态顺序表. 状态顺序表 CLK...

对于001011序列信号, 选择三位: 001->010->101->011->110->100->001->...... 无重复状态, 则选择该方案进行设计.(最小代价设计) 由上面选择的方案, 得到状态顺序表. 状态顺序表 CLK顺序 ...

对于001101序列信号, 选择三位: 001->011->110->101->010->100->001->...... 无重复状态, 则选择该方案进行设计. 由上面的选择, 得到下述状态序列表. 状态顺序表 CLK顺序 Q2 Q1 ...

对于序列信号0010111, 选择三位: 001->010->101->011->111->110->100->001->...... 无重复状态, 则选择该设计方案进行设计. 根据上面状态的序列, 绘制状态顺序表(并根据Q0的变化加入D0列)...

设计一个序列信号发生器电路,能在CLK信号作用下周期性输出“0010110111”的序列信号. module sequence( input clk, input rst_n, output out ); reg [9:0] sequence; always@(posedge clk or negedge rst_n) ...

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地