用Verilog HDL语言编写的SDRAM控制器,在DE2-70的开发板上实现。

”sdram“ 的搜索结果

SDRAM原理(强烈推荐)

标签: SDRAM

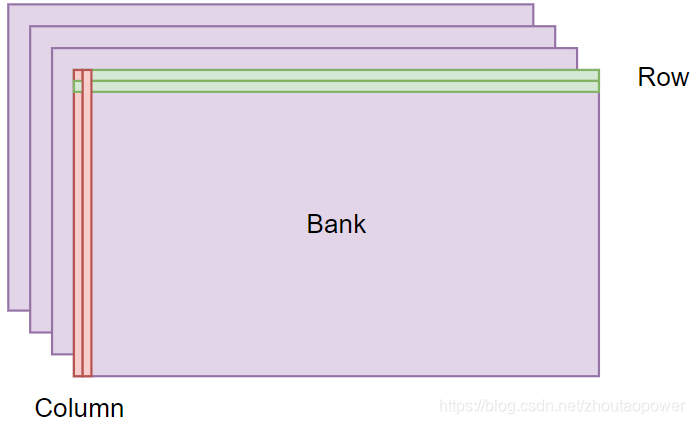

关于SDRAM原理的文章,人个感觉很不错。DRAM 的逻辑 BANK 概念是针对内存颗粒内部的。大家都知道 DRAM 内部的存储单元是以阵列形式 排列的。如下图所示。行列地址总线分别经过行列地址译码器译码后分别指向一行和一...

23 SEMC外扩SDRAM

标签: 嵌入式硬件

除了时钟、地址和数据线,控制 SDRAM 还需要很多信号配合,它们具体作用在描述时序图时进行讲解。RT1052 系列芯片扩展内存时可以选择 SRAM 和 SDRAM。给 RT1052 芯片扩展内存与给 PC 扩展内存的原理是一样的。

完整英文电子版JEDEC JESD79-4D:2021 DDR4 SDRAM Standard(DDR4 SDRAM 标准)。本文件定义了DDR4 SDRAM规范,包括特性、功能、AC和DC特性、封装和球/信号分配。本标准的目的是为符合JEDEC标准的2Gb至16Gb的x4、x8和...

vhdl 编写的sdram controler, 双通道

SDRAM的初始化过程可根据我提供的参考资料,同时结合我给的源代码。很好理解的。以下我主要介绍使用的方式。 二、调试及使用 我以Xilinx(xc6slx9-2ftg256)和altera(EP4C30)的开发板都进行过下载和验证,均没有问题...

讲解了SDRAM的存储原理,并以此设计并实现了SDRAM存储控制器。

也可以参考这里:https://forum.rocketboards.org/t/de10-nano-manual-instructions-fail-to-compile-ghrd-on-ubuntu-solved/1282/9。在ubuntu系统终端输入 sudo apt-get install make。...没有修改任何东西,直接拷贝...

关于SDRAM的读写相对比较复杂,本文件是基于FPGA的SDRAM的读写,可做参考

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机访问存储器)是一种动态随机访问存储器(DRAM),它与传统的DRAM相比,最大的特点在于“同步”二字。RAM的特点是易失性的,也就是说,当电源关闭时,...

基于SDRAM的串口回环测试

标签: fpga开发

基于SDRAM的串口回环测试

完整的讲述了SDRAM的原理,特性参数以及操作方法,是你了解内存的最佳资料

LTDC全称 LCD-TFT Display Controller,LCD显示控制器,提供了RGB信号和控制信号来直接控制外部LCD显示屏。为什么是直接控制呢?

动态随机存取存储器DRAM(Dynamic Random Access Memory,DRAM)是一种半导体存储器。由于在现实中品体管会有漏电电流的现象,导致电客上所存储的电荷数量并不足以正确的判别数据,而导致数据毁损。...

用FPGA实现对sdram读写的源代码,芯片用的是Altera公司的,需要的同学可以看看!

自己做的一个SDRAM控制器,供大家参考啊!

rt thread studio stm32h7 sdram错误1.cubemx 配置fmc在上面路径找到drv_sdram.c文件复制到drivers下面在上面路径找到sdram_port.h复制到drivers下include里。

本文记录了如何使用stm32cubeMX配置stm32h743iit6的硬件FMC外设与与 SDRAM 通信(W9825G6KH)。具体比较深的内容不作介绍。

实现一个通过串口调试助手发送“指令和数据”来控制SDRAM 读写操作的小项目。

多端口SDRAM控制器RTL级(verilog)代码,采用异步时钟,适用于各种SDRAM芯片,可以根据实际需求以及sdram带宽进行多端口的添加来实现多个模块间的数据交互。

DDR2 SDRAM SPECIFICATION,JEDEC Standard,Package ballout & addressing,Functional description

本文提出了一种基于文件结构存储方式的数据缓存系统,该系统利用FPGA设计结构化状态机实现对SDRAM的控制,完成了对数据的缓存与重组帧,具有速度快、可靠性高、灵活性强和功能可扩展等优点。

基于FPGA的DDR3_SDRAM控制器设计.caj

SDRAM的原理和时序,对于实现对SDRAM操作非常有帮助!

SDRAM的原理和时序,适合初学者入门,比较简单易懂~~

SDRAM fpga 存储器

STM32与FPGA通信 读取SDRAM数据

非常简单好用的SDRAM控制器,使初学者更加容易理解SDRAM的控制的操作,在Quatrtus环境中验证没问题。

推荐文章

- vuex中state对象会数组中的值更新后getters没有监听到state数据的改变的问题state数据跟新页面不刷新问题_vue对象数组改变元素没有getter-程序员宅基地

- 《Centos7——手动部署prometheus》_prometheus centos7-程序员宅基地

- iOS 数据保存几种方式总结_苹果ld都会保留那些数据-程序员宅基地

- quartus生成qdb文件_quartus 生成qxp和vqm文件的方法-程序员宅基地

- Servlet学习笔记3,及回忆。_attributeadded(servletrequestattributeevent ev)方法的-程序员宅基地

- cv::putText详解-程序员宅基地

- tomcat优化_tomcat ajp端口干嘛用的 关闭会怎么样-程序员宅基地

- (UVA)11916 Emoogle Grid-程序员宅基地

- 指针_定义一个指针变量他的值是多少-程序员宅基地

- 《Java基础——异常的捕获与抛出》_java捕获异常和抛出异常-程序员宅基地