soc-fpga2sdram-测试 在 Altera Cyclone V SoC 上测试 FPGA2SDRAM 接口

”sdram“ 的搜索结果

DDR4最新规范:JESD79-4_DDR4 SDRAM

的自动刷新类似于简化版的初始化操作,只是缺少了上电后的等待时间和模式寄存器配置部分,只包含一次预充电操作和两次自动刷新操作。自动刷新时序图可知,

在 t1、t3、t5 时刻图像都是残缺帧(新老帧各显示一半图片),在 t2、t4 时刻图像才是完整的一帧,而 VGA 那边可不管,每个时间点都会要一帧图像,这就是错帧现象。,因为当OV5640 帧率 30fps,VGA 帧率 60fps,仿佛...

用于 DE2-115 IS42S16320D 的 SDRAM 控制器 128mbytes --- 32M x 32bits DRAM Clk:133mhz Controller Clk:133mhz -150deg CAS:2 Burst:1 双通道(访问 DE2-115 上的两个芯片)

访问晶体管在SDRAM技术中的应用是电子工程设计的一个杰出范例。它展示了如何通过精密的电子控制来实现复杂的数据存储和管理功能。随着技术的不断发展,我们可以期待访问晶体管以及相关内存技术的进一步优化,以支持...

SDRAM通过其同步技术、动态刷新机制以及行缓冲区优化,提供了高效率和高性能的数据存储解决方案。随着技术的不断进步和对高性能内存的持续需求,SDRAM将继续在提升电子设备性能方面发挥关键作用。在未来,我们可以...

JESD79-4 DDR4 SDRAM 标准,英文文档

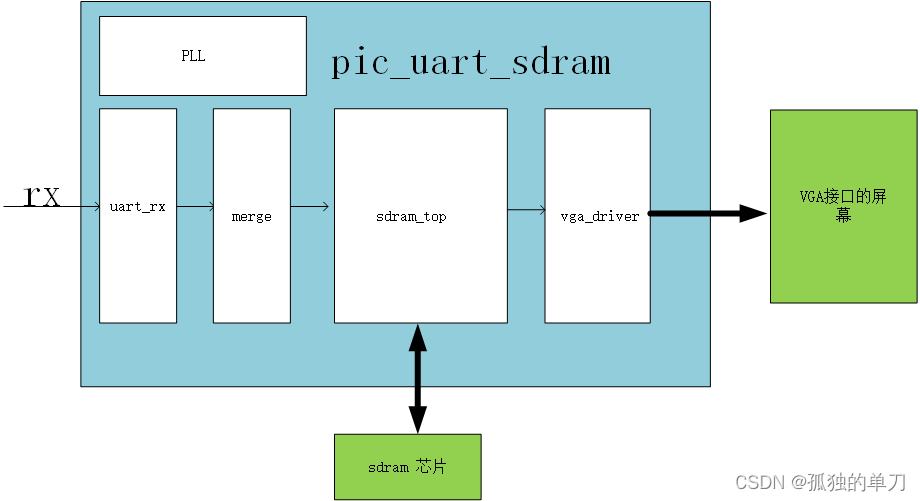

0 引言 SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适合那些需要海量存储器的应用领域,例如视频方面。 这里有一个视频项目要求将非标准的ITU-R BT.656视频...

STM32微控制器因其卓越的性能、灵活的内存配置选项以及广泛的应用领域而...这时,通过添加外部SDRAM来扩展存储容量成为了一个可行的解决方案。本文将引导您了解在STM32微控制器中如何实现外部SDRAM的连接、配置和使用。

STM32微控制器提供的片内RAM、片内Flash和SDRAM等存储选项,为设计高效、可靠的嵌入式系统提供了强大的支持。理解这些存储技术的特点和应用场景,对于开发能够满足不同需求的产品至关重要。STM32微控制器的存储选项...

完整的sdram控制代码,及其modelsim仿真,sdram verilog 控制实现。非常棒。

辅线1_硬件知识 SDRAM的设置 CPU发送地址给内存控制,由内存控制去访问外面SDRAM SDRAM逻辑结构图 SDRAM 有4个块 BANK 0 、BANK 1、 BANK2、BANK3,上图所示每块里面的每个格子表示的是16位数据 先发出片选信号...

BF518接的是比较古老的SDRAM,关于这个外存的详解,请看本文。

此外,在写数据和读数据通道,还包含一个LAST信号,以表示所传输的数据是否为最后一位。整体设计框图如下图所示,控制器由DDR3_control_top、DDR3_control_WR、MIG(IP核)以及异步FIFO:W_FIFO、W_FIFO组成,ddr3_...

本文介绍在FPGA设计中SDRAM电路的设计,对SDRAM的相关应用有很大的帮助。

STM32H743开发板移植micropython并外扩32M的SQPI flash和32M的SDRAM的源码,将本源码放到micropython/ports/stm32/boards/下,再回到micropython根目录用命令:make -C ports/stm32 BOARD=MYBOARD编译出固件,再下载...

23 SEMC外扩SDRAM

标签: 嵌入式硬件

除了时钟、地址和数据线,控制 SDRAM 还需要很多信号配合,它们具体作用在描述时序图时进行讲解。RT1052 系列芯片扩展内存时可以选择 SRAM 和 SDRAM。给 RT1052 芯片扩展内存与给 PC 扩展内存的原理是一样的。

完整英文电子版JEDEC JESD79-4D:2021 DDR4 SDRAM Standard(DDR4 SDRAM 标准)。本文件定义了DDR4 SDRAM规范,包括特性、功能、AC和DC特性、封装和球/信号分配。本标准的目的是为符合JEDEC标准的2Gb至16Gb的x4、x8和...

sdram model plus,SDRAM仿真模型,可用于SDRAM仿真实现。 parameter tAC = 6.5; //test 6.5 parameter tHZ = 5.5; parameter tOH = 2; parameter tMRD = 2.0; // 2 Clk Cycles parameter tRAS = 48.0; ...

文档是我当初设计SDRAM控制器的资料,希望能起到抛砖引玉的作用

为满足出租车拼车系统对LCD(Liquid ...设计中采用自定义图形处理命令,使用高速SDRAM (Synchronous Dynamic Random Access Memory)作为显存,以提升像素填充率、DMA(Direct Memory Access)操作方式和硬件多缓冲帧同步切换

完整的sdram模块 可以直接应用到项目中 有详细注释 自己手打

STM32F750驱动程序,HAL库。 项目支持STM32F7系列单片机调测和移植。 项目代码可直接编译、运行。

启用 SDRAM 外设 在 STM32F429 上有一个 SDRAM 控制器,可用于驱动 DRAM 芯片。 连接到演示板的是一个 8MB DRAM,所以这个演示配置它并让我们探索它,放入和取出东西。 --查克

在实际对SDRAM的读写中,我们一般不会对存储器一个一个存储单元的去读写,这样有耗时又耗力,需要不停的发送列地址与读写命令,虽然读写延迟相同可以让数据的传输在I/O端是连续的,但是会消耗大量的内存/控制资源,...

它是美国爱荷华州立大学的约翰·文森特·阿塔纳索夫(John Vincent Atanasoff)教授和他的研究生克利福特·贝瑞(Clifford Berry)在1937年设计的。 遗憾的是当时仅仅用于求解线性方程组,也没有申请,爱荷华州立...

在基于DSP的嵌入式应用中,存储器系统逐渐成为功耗的主要来源。例如Micron公司的MT48LC2Mx32B2-5芯片,在读写时功耗最大可以到达924 mW,而大...本文主要以访问外部SDRAM为例来说明降低外部存储系统功耗的设计方法。

推荐文章

- 【UBUNTU】ubuntu18.04安装及更新_ubuntu18更新-程序员宅基地

- OpenSSL心脏滴血漏洞(CVE-2014-0160)_openssl漏洞的原因是-程序员宅基地

- 数据结构实验-哈夫曼编码_待编码数据-程序员宅基地

- dataframe的索引遍历_pandas | 如何在DataFrame中通过索引高效获取数据?-程序员宅基地

- 位置传感器_lbk位置传感器-程序员宅基地

- dubbo 报错:java.lang.NoClassDefFoundError: org/I0Itec/zkclient/exception/ZkNoNodeException_dubbo nested exception is java.lang.noclassdeffoun-程序员宅基地

- Spring Boot 2.x 整合 ShardingSphere 5.0.0 实现分库分表_整合shardingsphere-jdbc-core-spring-boot-starter-程序员宅基地

- 表白编码C语言,C语言告白代码,一闪一闪亮晶晶~-程序员宅基地

- mycat_wrapper-linux-aarch64-64-程序员宅基地

- 支持向量机的核函数选择:影响性能的关键因素-程序员宅基地