”sdram“ 的搜索结果

SDRAM的仿真模型sdram_model_plus 作者:李晟、陈乃奎、罗瑶 在进行SDRAM初始化模块编写时使用

SDRAM指令

标签: SDRAM指令 其它

SDRAM也具有RAS、CAS及WE信号,其名称与异步DRAM相同,功能上也存在相似的地方,但其实际的处理方式是通过3条线的结合,对SDRAM发出指令。在异步DRAM的情况下,例如,如果使CAS信号在RAS信号前有效,则成为CAS先于...

摘要:介绍SDRAM的主要控制信号和基本命令时序,提出一种应用于解复用的支持多路读写的SDRAM接口设计,为需要大容量存储器的电路设计提供了新思路。 关键词:SDRAM 解复用 接口存储器是容量数据处理电路的重要组成...

详述DDR4的VREFDQ训练细节

1.SDRAM基础知识

标签: fpga开发

它是系统时钟引脚:SDRAM 由系统时钟驱动,所有 SDRAM 输入 信号都在时钟上升沿采样,同时 CLK 还递增内部突发计 数器并控制输出寄存器。2.CKE:位宽为1Bit,类型为 Input。它是时钟使能引脚:屏蔽系统时钟,冻结...

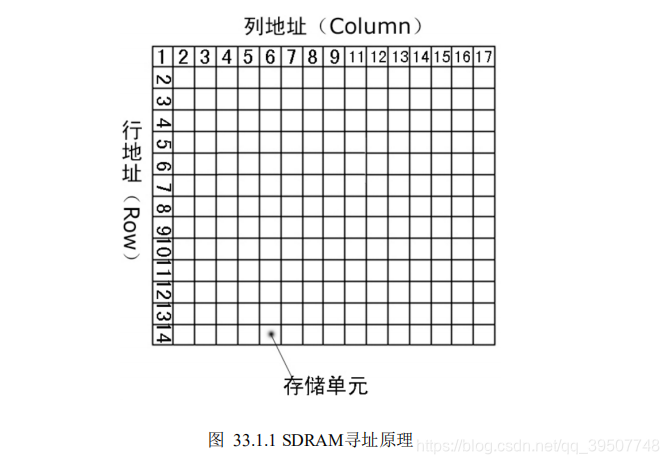

对于DQM(Data I/O Mask)信号,每个DQM控制屏蔽8bit数据,对于这款SDRAM,它是16bit的,UDQM可屏蔽高8位,LDQM可屏蔽低8位。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地...

OV5640摄像头+SDRAM显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档资料,FPGA为CYCLONE10LP系列中的10CL025YU256C8. 完整的Quartus工程文件,可以做为你的学习设计参考。 采用 500 万像素的 OV5640 ...

STM32单片机读写 SDRAM(MT48LC4M32B2TG)软件例程源码,可供学习参考。 SDRAM为 MT48LC4M32B2TG-7 容量16M字节,32Bit 在使用SDRAM前,必须调用 bsp_InitExtSDRAM() 函数配置FMC。 外部SDRAM的物理地址为 0xC000 ...

详述DDR4的ODT功能,以及新增RTT_PARK的用意。

tRCD 是 SDRAM 的一个重要时序参数,广义的 tRCD 以时钟周期数为单位,比如 tRCD=2,就代表延迟周期为两个时钟周期。具体到确切的时间,则要根据时钟频率而定,对于 STM32H7 驱动 SDRAM,采用的 200MHz,实际使用要...

全称为(Double Data Rate Synchronous Dynamic Random Access Memory,Double Data Rate SDRAM,),中文名为“双数据率同步动态随机存储器”或者“双数据率SDRAM”。DDR是在原有的SDRAM的基础上改进而来。此时为了...

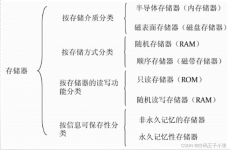

SDRAM 英文全称“Synchronous Dynamic Random Access Memory”,译为“同步动态随机存取内存”或“同步动态随机存储器”,是动态随机存储器(Dynamic Random Access Memory,简称 DRAM)家族的一份子。

介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元,这是内存芯片寻址的基本原理,这...

DDR5 SDRAM的主要特性是芯片容量,而不仅仅是更高的性能和更低的功耗。DDR5预计将带来4266至6400 MT / s的I / O速度,电源电压降至1.1 V,允许的波动范围为3%(即±0.033V)。每个模块使用两个独立的32/40位通道(不...

SDRAM 的基本概念、数据存储原理、存储容量、操作命令的简单介绍。

SDRAM电路设计

JESD79-4C:DDR4 SDRAM Standard(DDR4标准)-最新完整版-带详细标签(265页) 全网带最详细书签版。。。完整英文电子版 JEDEC JESD79-4C ,带最详细书签。本文档定义了 DDR4 标准,包括特性、功能、交流和直流特性、封装...

基于cyclone4E FPGA (EP4CE10E22C8+SDRAM) 最小系统开发板评估板硬件(原理图+PCB+封装库),AD09设计的项目工程文件,仅供学习设计参考。

基于cyclone4E FPGA (EP4CE10E22C8+SDRAM) 最小系统开发板评估板硬件(原理图+PCB+封装库),AD09设计的项目工程文件,仅供学习设计参考。

嵌入式实时图像处理系统中SDRAM控制器的实现,介绍一种用于嵌入式实时图像处理系统的SDRAM控制器的实现方案。根据实时系统对数据传输速率及连续性的要求,将SDRAM配置为全页突发操作模式,并采用异步FIFO作为FPGA与...

SDRAM参考设计文档资料学习手册+cyclone4e FPGA读写SDRAM例程Verilog语言quartus18.0工程源码,可做为你的学习设计参考。 DDR2_SDRAM操作时序.pdf H57V2562GTR.pdf HY57V561620_32MB.pdf SDRAM_ipcore_(Altera_中文)....

DDR3 SDRAM(Double Data Rate 3 Synchronous Dynamic RAM),即第三代双倍速率同步动态随机存储器。本系列文章尝试剖析缓存技术的基础原理,并通过FPGA进行实现。

SDRAM各种读写模式的时序总结

镁光SDRAM仿真模型(免费共享),用于SDRAM仿真

JEDEC 收费,标准文档不好找,供大家参考下载 This document defines the DDR4 SDRAM specification, including features, functionalities, AC and DC characteristics, packages, and ball/signal assignments.

本文档定义了 DDR4 SDRAM 规范,包括特性、功能、交流和直流特性、封装和球/信号分配。本标准的目的是为 x4、x8 和 x16 DDR4 SDRAM 设备定义符合 JEDEC 的 2 Gb 到 16 Gb 的最低要求。该标准是根据 DDR3 标准 (JESD...

包含两季的代码: 开源骚客第一季源代码-Sdram_Controller 开源骚客第二季源代码-SDRAM那些事儿

推荐文章

- SMT的基本知识介绍_smt行业基础知识-程序员宅基地

- 43.基于SSM的口腔护理网站|基于SSM框架+ Mysql+Java设计与实现(可运行源码+数据库+lw)-程序员宅基地

- HTML中Table表格的使用与漂亮的表格模板_html table 样式-程序员宅基地

- Linkage Mapper中的局部和全局地图比较实践指南(含实例分析)-程序员宅基地

- 线性筛求欧拉函数-程序员宅基地

- 初中几何题_初中几何题解-程序员宅基地

- jQuery 放大镜效果_jquery放大效果-程序员宅基地

- Python构建快速高效的中文文字识别OCR_中文ocr python-程序员宅基地

- SQL语句用case when实现if-else条件逻辑_case when里面可以加if else吗-程序员宅基地

- 数据结构实验课程设计报告求工程的最短完成时间_(1)用字符文件提供数据建立aoe网络邻接表存储结构; (2)编写程序,实现图中顶点的-程序员宅基地