”risc-v“ 的搜索结果

软件。

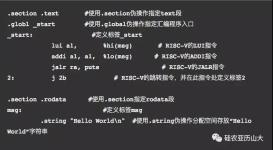

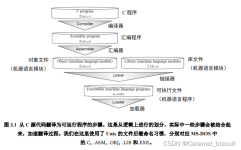

views of a file’s contents, reflecting the differing needs of these activities. Fidai 写RISC-V、C++ gure 3 shows the。

引入: 简单的介绍一下X86、ARM、RISC-V三种cpu架构的区别和应用场景。X86、ARM和RISC-V是三种不同的CPU架构,它们在设计理念、指令集和应用场景上有一些区别。

学习资料:RISC-V原子指令LR/SC_lr sc-程序员宅基地

对于该中断的处理过程,与正常中断处理流程一致,可参考《RISC-V特权架构 - 模式切换与委托》中《中断处理时模式切换》章节。设置mip寄存器中的STIP字段,相当于把M模式下的定时器中断,注入S模式,并由S模式的操作...

第 一部分 CPU与RISC-V综述 第 1章 一文读懂CPU之三生三世 2 1.1 眼看他起高楼,眼看他宴宾客,眼看他楼塌了——CPU众生相 3 1.3 人生已是如此艰难,你又何必拆穿——CPU从业者的无奈 17 1.4 无敌是多么寂寞——...

项目地址:https://gitcode.com/T-K-233/RISC-V-Single-Cycle-CPU 在这个数字化的时代,了解并参与计算机硬件的设计变得越来越重要。今天,我们向您推荐一个开源项目——RISC-V单周期CPU,这是一个基于RISC-V指令集...

探索形式验证:RISC-V Formal项目详解 项目地址:https://gitcode.com/SymbioticEDA/riscv-formal 在计算机硬件设计中,形式验证是一种确保芯片设计准确无误的重要方法。它通过数学证明的方式验证硬件描述语言(如...

RISC-V架构学习

标签: RISC-V

RISC-V架构RISC-V简介RISC-V起源RISC-V大事件RISC-V 指令特点设计哲学-简单就是美无病一身轻——架构的篇幅能屈能伸——模块化的指令集浓缩的都是精华——指令的数量RISC-V指令集简介模块化的指令子集规整的指令编码...

探索未来计算:RISC-V PK项目解析 项目地址:https://gitcode.com/riscv/riscv-pk [GitHub仓库地址] 在当今计算机世界中,RISC-V架构正在迅速崛起,以其开源、精简和可扩展性吸引了全球的关注。RISC-V PK(Process ...

【代码】Cross-Compiling Dynamorio for RISC-V。

RISC-V特权级别

标签: risc-v

所以内核分两部分,运行在M模式下的代码为内核提供访问硬件资源的能力,而S模式下的代码则更加灵活。里的最高权限模式,它具有访问所有资源的权限,它的代码是百分百可信的,通常运行在这个模式下的为。...

物联网产业链专题报告-RISC-V大有可为.docx

We have provided a template code using C++.写RISC-V CPU Pipeline Simulation You can refer to this code for your work, or。

XV6 RISC-V 解决方案:一款开源操作系统学习平台 项目地址:https://gitcode.com/KuangjuX/xv6-riscv-solution 项目简介 XV6 RISC-V Solution 是一个基于经典 XV6 操作系统的移植版本,专门为 RISC-V 架构设计。XV6 ...

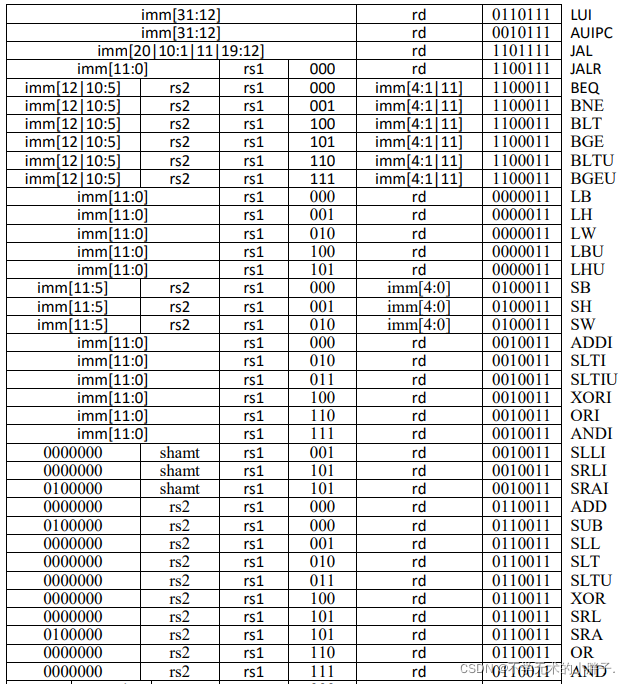

本文采用RISC-V架构设计CPU,实现单周期CPU,设计取指、译码、执行、访存、写回五个阶段,扩展实现了RV32I指令集,通过该指令集所有指令的仿真测试。工具采用了iverilog和GTKwave。(具体仿真调试过程见下一篇文章)

RISC-V工具链和QEMU编译测试

随着摩尔定理的几近失效,传统的追求通用...介绍了开源芯片的作用和发展历史,讨论了有望成为下一代芯片开发根基的RISC-V指令集架构的特点和影响以及前端设计中的敏捷开发实践,并对芯片开发的新发展与不足做出了总结。

总之,学习RISC-V需要掌握计算机系统的基础知识,熟悉RISC-V指令集架构和微体系结构,理解RISC-V的编程模型和编译工具链,并实践项目开发,才能真正掌握RISC-V的开发和应用。

RISC-V指令集体系结构分析。

RISC-V架构采用了基于定长指令(Fixed-length instruction)和模块化设计方案。具体来说,RISC-V的指令长度为32位,在指令长度相同的前提下,RISC-V的指令数量比ARM、x86等指令集更少,使得其指令执行效率更高。此外...

RISC-V还是一个非常年轻的指令集架构,同时其十分瞩目精简、开源的特性也十分有利于我们学习,所以在未来的一段时间内,将把主要精力放在对RISC-V的指令集架构,包括基本指令集和拓展指令集的学习,不定时在此更新

推荐文章

- C++语法基础--标准库类型--bitset-程序员宅基地

- [C++] 第三方线程池库BS::thread_pool介绍和使用-程序员宅基地

- 如何使用openssl dgst生成哈希、签名、验签-程序员宅基地

- ios---剪裁圆形图片方法_ios软件圆形剪裁-程序员宅基地

- No module named 'matplotlib.finance'及name 'candlestick_ochl' is not defined强力解决办法-程序员宅基地

- 基于java快递代取计算机毕业设计源码+系统+lw文档+mysql数据库+调试部署_快递企业涉及到的计算机语言-程序员宅基地

- RedisTemplate与zset redis_redistemplate zset-程序员宅基地

- 服务器虚拟化培训计划,vmware虚拟机使用培训(一)概要.ppt-程序员宅基地

- application/x-www-form-urlencoded方式对post请求传参-程序员宅基地

- 网络安全常见十大漏洞总结(原理、危害、防御)-程序员宅基地