”Verilog设计综合“ 的搜索结果

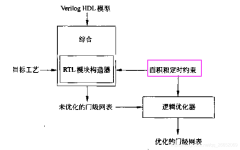

综合就是将Verilog描述的RTL级的电路模型构造出门级网表的过程。综合只是个中间步骤,综合后生成的网表文件,就是由导线相互连接的寄存器传输级功能块(像是触发器、算术逻辑单元和多路选择器等)组成的。这里就需要...

在数字电子钟设计中,我们需要深入了解数字电子钟的工作原理、设计需求以及Verilog实现数字电子钟的优势和挑战。让我们一起来探讨这些内容: ### 2.1 数字电子钟的工作原理 数字电子钟是一种基于数字电子技术的...

事实上,Verilog定义的语法非 常之多,但绝大部分都是为了仿真测试来使用的,只有少部分才是用于电路设计,详细可以参考本书 的“可综合逻辑设计”一节。比如“#100”之类的延时功能, 简单的门器件是无法实现延时...

verilog中可综合和不可综合的变量、函数、关键词等

Verilog HDL数字设计与综合(第二版) 第六章课后习题答案.pdfVerilog HDL数字设计与综合(第二版) 第六章课后习题答案.pdfVerilog HDL数字设计与综合(第二版) 第六章课后习题答案.pdfVerilog HDL数字设计与综合(第二版...

逻辑综合的目的是产生物理电路门级结构,并在逻辑、时序上进行一定程度的优化,寻求逻辑、面积、功耗的平衡,增强电路的可测试性。正确地分析了用户的电路需求后,就可以进行逻辑功能的总体设计,设计整个电路的功能...

解决:设计可综合状态机的指导原则! 解决:设计各种基础的组合逻辑电路和时序逻辑电路! 解决:如何设计有实用价值的高性能的数字逻辑电路系统!

用verilog HDL语言通过两种方法实现设计2倍频 用verilog HDL语言通过两种方法实现设计2倍频

Verilog数字系统设计教程erilog数字系统设计教程下载 书籍大小:123MB书籍语言:简体中文 书籍类型:国产软件书籍授权:免费软件更新时间:2019-07-24 17:08:33书籍类别:编程其它.

通过逻辑综合,设计工程师可以优化电路的性能、面积和功耗,以满足设计要求。综合过程:运行综合工具,并提供综合脚本作为输入。综合工具将读取Verilog代码,并进行语法分析、优化和转换,生成等效的门级电路描述。...

所以目前 Verilog 大多数用于描述数字设计的行为级层次(RTL),一般只注重设计实现的算法或流程,而不用特别关心具体的硬件实现方式。有些设计,例如门控时钟,就需要使用基本门单元,来增加电路的可控性与可靠性。

Verilog HDL数字设计与综合(第二版).pdf

用verilog编写的抢答器实验设计.rar

代码规范要讲述的内容与编码风格是不一样的。...除非针对某种特殊的设计,或个人轻车熟路、把握十足,可以稍微的越界 Verilog 代码规范,否则在设计中还是建议多注意这些规范。尤其初学者特别容易触犯此类问题。

Verilog设计小技巧同步时序逻辑: Ø 同步时序逻辑的状态寄存器组的值只可能在唯一的触发条件发生时可改变。异步时序逻辑的状态寄存器值改变的触发条件

由于Verilog HDL硬件描述语言语法灵活、易懂,非常接近c语言的风格,所以逐渐成为集成电路设计领域中为流行的设计语言。正是由于硬件描述语言的出现,才使得大规模、超大规模、特大规模、甚至千万门系统级SOC设计...

基于模块化的设计思想, 采用 Verilog HDL 语言设计一个能进行时、分、秒计时的二十四小时制的数字电子钟, 并具有整点报时功能。 采用数码管进行时间显示,要求显示格式为:小时-分钟-秒钟。

Pyverilog 是用于 Verilog HDL 的开源硬件设计处理工具包。所有源代码都是用 Python 编写的。 Pyverilog 包括(1) 代码解析器、(2) 数据流分析器、(3) 控制流分析器和 (4) 代码生成器。您可以基于此工具包创建自己的...

本书从用户角度全面产阐述了Verilog HDL 语言的重要细节和基本设计方法

verilog hdl数字设计与综合(第二版)

【资料】Verilog HDL数字设计与综合PDF-附件资源

FPGA,verilog语言设计ADC和DAC,课设需要,货真价实!

采用verilog实现的有限域GF(28)弱对偶基乘法器设计

Verilog HDL主要用于数字电路设计的描述,因此缩写的程序需要是可综合的语句。而Verilog HDL语法中有大量的仿真验证语句,这些都属于仿真测试时使用,不能被综合成电路。所以在实际设计电路系统时,需要注意区分可...

Verilog逻辑综合等重要类容

标签: A+

很多开发板的程序写的很烂,我也做过一段时间的开发板设计,我觉得很大程度上,开发板在误人子弟。不过原厂提供的正品开发板,代码很优秀的,可以借鉴。只有了解了FPGA内部的结构才能明白为什么写Verilog和写C整体...

VerilogHDL是目前应用最广泛的一种硬件描述语言,用于数字电子系统的设计。可用它进行各种级别的逻辑设计,并进行数字逻辑系统的仿真验证,时序分析,逻辑综合。小波滤波器的设计属于复杂算法的电路设计,因此利用...

采用verilog语言实现数据的发送与接收设计

推荐文章

- 如何将xml转换为json_xml转json-程序员宅基地

- TCP 的那些事 | TCP报文格式解析_.tcp文件是图片吗-程序员宅基地

- python——stack()和unstack()用法_unstack函数-程序员宅基地

- C语言调用sqlite3命令语句实现将txt文件导入到数据库中_从txt导入到sqlite-程序员宅基地

- AOP与OOP有什么区别,谈谈AOP的原理是什么,大厂Android高级面试题汇总解答-程序员宅基地

- 最小费用流_单向图费用流-程序员宅基地

- Python中的5个高阶概念属性的知识点!你要了解明白哦!_python属性的五大类-程序员宅基地

- python 基于PHP+MySQL的装修网站的设计与实现_python抓取装修需求-程序员宅基地

- ubuntu完美的nvidia驱动安装方式(ubuntu16+驱动410+cuda10.0)or(ubuntu16+驱动455+cuda11.1)_乌班图英伟达驱动选着哪个版本-程序员宅基地

- 解决redis超时io.lettuce.core.RedisCommandTimeoutException: Connection timed out after 5s-程序员宅基地