”ISE“ 的搜索结果

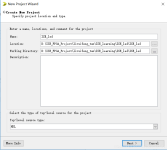

本篇博客介绍了ISE开发软件的相关使用,包括了新建工程,下载程序等

ISE.1.ISE产品介绍 ISE.10.有线802.1x.1 ISE.10.有线802.1x.2 ISE.11.无线802.1x上 ISE.11.无线802.1x下 ISE.12.Web Auth ISE.13.Guest Service介绍. ISE.14.Profiler Service介绍 ISE.15.1.Client Provisioning ISE...

ISE14.7 license 亲测可用

FPGA实现 CIC抽值滤波 滤波器 verilog 仿真和matlab simulink仿真 vivado ise quartus软件均可以,匹配滤波器系数生成等 含说明 doc,电子ZL售出不退,这个需要一定的数字信号处理知识和熟练操作相应软件,目前还做...

ise 洗衣机

标签: isi is ise

ise verilog语言编写洗衣机控制系统。。

CISCO ISE 3.1 中文版

ISE中的Tcl功能可以完成重新创建工程,添加项目文件并设定编译选项等工作,ISE版本10.1中也提供了用于源代码控制的相应菜单。 利用Tcl控制版本的好处如下。 (1)Tcl脚本是文本文件,而ISE的工程文件(例如watchve...

以上是围绕“verilog实现UART:RS232串口的收发”这一主题展开的一篇技术文章,介绍了Verilog代码实现UART的收发功能,并通过波形仿真和验证确保代码的正确性,同时介绍了常用的FPGA开发工具ISE和Quartus。...

4、安装完毕后点击ISE可能会打不开,需要用以下文件进行替换,替换目录为ISE的所在目录,直接复制进去替换即可。中下拉xsetup进程(如图所示),关闭里面的xwebtalk子进程即可,需要关闭两次,才会继续安装进程,别关...

FPGA公司主要是两个Xilinx和Altera(现intel PSG),我们目前用的ISE是Xilinx的开发套件,现在ISE更新到14.7已经不更新了,换成了另一款开发套件Vivado,也是Xilinx的产品,intel的开发套件是Quartus II系列,我们...

思科无线ISE配置手册

ISE邮递员收藏思科身份服务引擎(ISE)邮递员收藏此存储库包含ISE REST API的集合。 这可能是开始使用REST API的最简单方法。 外部RESTful服务(ERS) :允许外部客户端对ISE资源执行CRUD(创建,读取,更新,删除)...

硬件问题导致的bsdl文件与读取到的idcode不匹配解决方法

第3节 基于ISE的开发流程 本节所有的讲解都以例4-3所示的代码为基础展开。 例4-3 ISE开发流程演示代码,将输入的数据加1寄存并输出。 module test(clk, din, dout); input clk; input [7:0] din; ...

ISE-固化程序方法.docx

标签: ise

ISE程序固化流程:1. 生成.bit文件 2. 生成.msc文件 点击configure target device,弹出界面,点OK继续。 进入ISE iMPACT 界面 ,双击 Create PROM File。 选择对应FLASH的种类,用的是并口的话,左边选BPI ;...

ISE 10.1版本,适用于xilinx V2系列FPGA,同时支持国产芯片开发

从LDPC码的基础理论出发,在研究前人成果的基础上,针对CMMB标准,采取理论阐述、算法仿直等方式进行了LDPC码的构造方式分析、编码技术分析和译码算法仿真比较,并最终以综合性能较好的最小和译码算法作为基础,对...

xilinx_ise_14.4_licence xilinx_ise_14.7_licence

基于SPARTAN-6系列芯片以及ISE设计工具对机器人控制电路进行了设计和仿真源码(验证了电路的正确性和可靠性。同时机器人使用了温湿度传感器、人体感应传感器、超声波传感器、震动传感器、有毒气体传感器等可对灾区的...

在本文中,我们将聚焦于FPGA在UDP纯逻辑编写方面的应用,并结合Xilinx ISE 14.7平台进行工程验证。具体而言,我们将介绍如何利用FPGA实现千兆速率下的无丢包传输,并通过添加200k128通道采集的功能进一步拓展其应用...

/*****模块名称:(2,1,7) 维特比译码器 ******////// /*****模块功能: 完成卷积编码后的接收机译码工作,共64个状态,回溯深度大于35即可,可由宏DEPTH设置******////// /*****输入:******////// ...

使用ISE14.7实现MSK调制信号通过AD9361芯片输出 ipath_generator i_path_inst ( .clka(clk), // input wire clka .rsta(rst), // input wire rsta .addra(addra), // input wire [ADDR_WIDTH-1 : 0] addra ....

ISE的语言模板中提供了系统同步接口的输入偏移约束,它按照不同的设计情形给出了许多例子,目的就是为了提供一些真实的例子教给设计者正确地把该约束与其他相关的约束一起使用。图1所示为—个系统同步接口的输入偏移...

ISE14.7的证书文件,具体安装过程见百度教程。Xilinx 已经停止对 ISE 软件的更新, 所以版本14.7为ISE开发环境的最高版本, 大家也再也不需要为软件的不断升级而疲于奔命了。

推荐文章

- Codeforces-学校排队-程序员宅基地

- 计算机毕业设计ssm基于JAVA的图书馆自习室座位预约系统194fd9 (附源码)轻松不求人_基于ssm的图书馆预约座位-程序员宅基地

- 实值复变函数求导 ——(Wirtinger derivatives)_wirtinger导数-程序员宅基地

- VMWare虚拟机设置固定IP上网方法_vm虚拟机只允许指定ip访问-程序员宅基地

- 深度学习修炼(一)线性分类器 | 权值理解、支撑向量机损失、梯度下降算法通俗理解-程序员宅基地

- 基于SpringBoot的社区团购APP+02043(免费领源码)可做计算机毕业设计JAVA、PHP、爬虫、APP、小程序、C#、C++、python、数据可视化、大数据、全套文案-程序员宅基地

- 如何在无公网IP环境下远程访问Serv-U FTP服务器共享文件-程序员宅基地

- uniapp的navigateTo页面跳转参数传递问题_uni.navigateto刷新携带参数丢失-程序员宅基地

- C++中std::getline()函数的用法-程序员宅基地

- vue 工作中的一些小总结(基础知识供刚入门的小伙伴看 vue+elementUi+vsCode+vue-router+iconfont )_mac+elementui+vscode-程序员宅基地