”IC后端“ 的搜索结果

1、了解数字ic设计全流程(√) 2、数字电子技术基础(学习ing) 目前在看mooc上东南大学的数字电子基础,在复习中 (知乎推荐闫石老师的《数字电子技术基础》,回头看看) 3、学习Verilog、System Verilog(还...

数字IC后端设计实现全流程解析

数字IC物理设计(PR)中的一些经验和解决方法

数字IC后端实战项目——基于TSMC 28nm低功耗四核A7 top的hierarchical flow物理设计实现

后端相关的学习,聊以记录,请慎重参考

数字IC后端设计实现应该如何快速入门?

数字IC前端到数字IC后端的synopsysEDA自动化流程脚本,自动处理DC、FM、PT等等软件的自动处理脚本

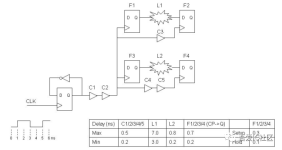

CTS就是时钟树综合。时钟树就是指从某个时钟root点长到sink点的buffer/inverter树,时钟树综合,顾名思义,就是指对时钟树进行综合:生成时钟树,使得同一时钟尽量尽快、同时地到达不同寄存器,对抗时钟源到不同终点...

史上最全的数字IC后端设计实现培训教程(整理版) 由于最近比较忙,前几天才把五月份开展活动送的书全部寄出,预计最迟明后天就会送到各位手中,希望各位多多理解!本次活动共送出八本《Low Power Flow》Physical ...

完整的后端设计由后端半定制和后端全定制两个设计部分组成: 后端全定制设计是指在设计初期最先按照设计...数字IC后端设计是指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用

虽然2022年IC行业门槛有所提高,但这也抵挡不住同学们对转行IC行业的热情,数字后端设计的发展前景和高薪也在众多岗位中脱颖而出,那么数字IC后端设计如何快速入门?下面IC修真院就带大家来了解一下。

形式验证是近几年来兴起的一种验证方法,它需要一个正确的模型作为参考,把待验证的电路与正确的模型进行比较,并给出不同版本的电路是否在功能上等效的结论,它利用理论证明的方法来验证设计结果的正确性。...

今天IC修真院为大家带来了数字IC后端的面试题目,希望大家能够用得上。

数字IC后端笔试500题出炉!(附答案) 吾爱 IC 社区 吾爱 IC 社区(52-ic.com)是一个专业交流和分享数字 IC 设计与实现技术与经验的 IC 社区 145 篇原创内容 公众号 新一年的秋招又要到了,为此小编特定编写整理了一...

其实IC面试本身并不是很复杂,但对于那些刚准备入行的同学来说,难免担心自己准备不充分,下面IC修真院就来为大家做IC面试非常有用的实战分享。

数字后端处于数字IC设计流程的后端,属于数字IC设计类岗位的一种。在IC设计中,后端设计的人数占比算是比较多的,并且随着芯片行业的不断发展,后端工程师的人才需求未来会越来越多。

芯片行业的发展过程中一个很大的问题就是人才需求量大,我国集成电路相关的毕业生有20万左右,但只有不到三万的毕业生。所以就有很多人转行,尤其是IC后端,这个岗位的需求量大,薪资高,成为了多数人转行的首选。

【机密】数字IC后端笔试面试题库(附知识星球活动) 最近很多公司的校招都陆续开始了,不知道今年应届生的小伙伴们准备好了没?如果你们是吾爱 IC 社区的老铁,平时又在看小编公众号的文章和知识星球的分享,那么...

成为一名数字IC后端工程师需要掌握哪些技能?

数字IC后端设计实现面试问答 最近知识星球官方一直在做技术更新维护,似乎已经有一周时间了,导致了很多星友无法发帖提问,包括小编也无法发表任何主题,对此小编深表抱歉。在官方维护这段时间,各位星友可以私信...

比如RAM,ROM及其他IP模块等)、IO等的大小和位置,有时候还需要提前定义一些placement blockages,groups/regions等等,是后端设计的第一步,也是后续所有P&R工作的基础。floorplan与placement的区别是。

近一周忙里偷闲,利用晚上的琐碎时间跑了一个录音芯片的后端PD流程,由于之前在课堂上学的数字EDA仅限于书本概念,一些概念的理解只是停留在表面,实践之后的确豁然开朗了很多,里面很多技术细节绝不是课堂上翻几页...

后端的总体工作用一句总结就是:运用给定的输入,在给定的时间内做出符合signoff条件的PR结果并满足各种验证。 下图对数字后端流程做了大致描述: 输入是整个数字后端工作的开始,也是最根本的基础。它包含了...

数字IC后端实现项目案例分享(文末附赠书等活动) 首先我们来看下上周分享的时钟结构案例。如果做时钟树综合时不做特殊处理,clk chain 这个 moudle 下 reg 会和其他的 reg 做 balance,导致 clk chain 中 reg 的 ...

如何用工具自动修复数字IC后端设计实现绕线后的Physical DRC? 吾爱 IC 社区的网站经过一个月的运营管理,目前每天的自然流量稳定在 180IP 左右,各项指标也呈现上升趋势。小编对网站有个小小的期许,希望未来能够...

BE Back End 后端,指IC设计中的后端设计流程 BIST Build in System Test 内建测试系统,DFT中的常见流程 CTS Clock tree synthesis 时钟树综合,是数字后端实现中的重要流程 DC design compiler synopsys公司的数字...

近年来IC行业越来越火热,不少企业纷纷加大研发、扩产和建厂,对IC高端人才的需求量非常大。尤其是数字后端设计工程师,成了很多企业的“香饽饽”。

1.1 EETOP版主面试问题 001) Why power stripes routed in the top metal layers? 为什么电源走线选用最上面的金属层? 因为顶层金属通常比较厚,可以通过较大的电流 1.高层更适合globalrouting....

RTL+SDC+Library -> 逻辑综合 -> Gate-Level Netlist -> 时序验证(粗略,仅针对setup) -> 形式验证Ⅰ -> (Floorplan -> Placement -> 时钟树综合)(物理实现) -> 形式验证Ⅱ ->...

模拟版图layout能否转数字IC后端实现? 模拟版图 OR 数字后端 APR 这两者其实最终成果都是 GDSII,都是将设计的 GDSII release 给 foundary 进行加工流片。它们的差别就在于前者是模拟版图,后者是数字版图。模拟...