”Cache“ 的搜索结果

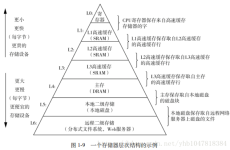

目录前言cache高速缓存直接映射全相连映射组相连映射指令缓存与数据缓存虚拟内存(重要⚠)页表缺页替换TLB例题(重要⚠)FastMath 前言 来到存储器章节的复(yu)习。首先引入 cache 高速缓存,来缓解高速的 cpu 和...

介绍CHI协议中的Cache Stashing操作和DVM操作

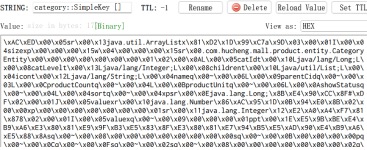

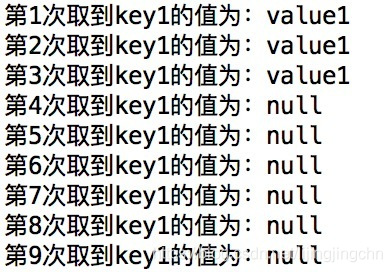

2020博客地址汇总 2019年博客汇总 项目建设过程中遇到一个问题:使用频率很高的基础数据(8MB)(可变更)。缓存到redis 存取效率不高。存在多条这样的基础数据。 ...当然,可以用ListenableFutureCallback结合...

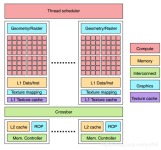

Cortex-A53处理器的L1 data cache以及L2 cache都不支持Write-Through策略,当处理器访问内存类型为Write-Through的数据时,这些数据并不会经过L1 data cache和L2。 至于L1 instruction cache,对于指令数据,处理器...

这个问题一直困扰我,直到有一天不知道在哪听到还是看到一句话(大概是这个意思):“如果把cache优化的差不多了,那么性能就几乎没有什么可优化的空间了。”听到这句话后,文化程度不高的我立马拍手叫绝,惊呼WOCAO...

TCM和CACHE简述

标签: 缓存

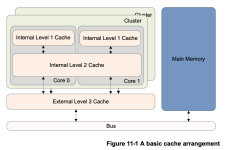

CACHE的定义 Cache存储器,电脑中为高速缓冲存储器,是位于CPU和主存储器DRAM(Dynamic Random Access Memory)之间,规模较小,但速度很高的存储器,通常由SRAM(Static Random Access Memory 静态存储器)组成。...

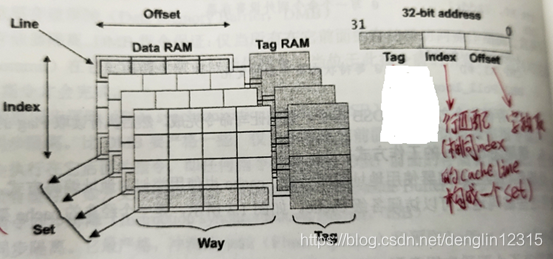

Cache总位数或总容量=标记项的总位数+数据块的总位数 标记项=有效位+脏位(全写法没有脏位,写回法有脏位)+替换控制位(有替换算法时)+标记位(与主存的高位相同) 这里我一直搞混的一点是把标记项当作地址结构中...

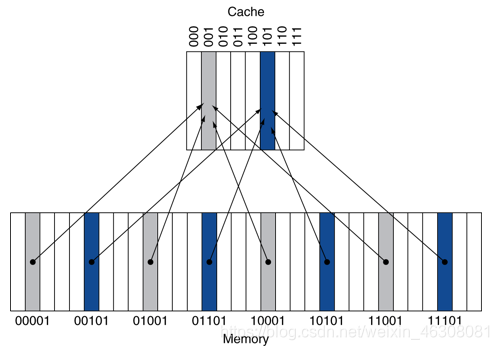

Cache的地址映射中,会以Cache的容量为标准将内存分成相同大小的块(页或者区),根据映射方法的不同,地址的表达方式也不同,常见的映射方式分为:直接映射、全相联映射和组相联映射。

Cache–主存的地址映射 由主存地址映象到cache地址称为地址映象 1.直接映射(固定的影响关系) 主存中的任意块映射到缓存中的唯一块,每个主存块只与一个缓存块相对应。 i为缓存块号,j为主存块号,C为缓存块数,...

python缓存机制

实验四 Cache 性能分析 一.实验目的: (1) 加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。 (2) 掌握Cache容量、相联度、块大小对Cache性能的影响。 (3) 掌握降低Cache不命中率的各种方法以及这些方法...

具体可以说给定内存地址后我们就有了映射的地址结构,然后找到对应的cache地址,最后比较所有可能的cache地址中的内容来判断cache命中或未命中,而这个cache块内容与cache行的位数有关。

我们说的cache为了缓解数据库的压力, 我们一般都会把热数据放到缓存, 常用的缓存只要有redis, memcache等. 但是像redis, memcache这样的缓存我们真的一定需要需要么. 非也!非也!redis, memcache这样的缓存, 更多的...

void printHelpMenu(){ printf("Usage: ./csim-ref [-hv] -s <num> -E <num> -b <num> -t <file>\n");... printf("Options:\n");... printf(" -h Print this help message.\n");...

推荐文章

- 阿里云企业邮箱的stmp服务器地址_阿里云stmp地址-程序员宅基地

- c++ 判断数学表达式有效性_高考数学大题如何"保分"?学霸教你六大绝招!...-程序员宅基地

- 处理office365登录出现服务器问题_o365登陆显示网络异常-程序员宅基地

- Nginx RTMP源码分析--ngx_rtmp_live_module源码分析之添加stream_ngx_rtmp_live_module 原理-程序员宅基地

- 基于Ansible+Python开发运维巡检工具_automation_inspector.tar.gz-程序员宅基地

- Linux Shell - if 语句和判断表达式_shell if elif-程序员宅基地

- python升序和降序排序_Python排序列表数组方法–通过示例解释升序和降序-程序员宅基地

- jenkins 构建前执行shell_Jenkins – 在构建之前执行脚本,然后让用户确认构建-程序员宅基地

- 如何完全卸载MySQL_mysql怎么卸载干净-程序员宅基地

- AndroidO Treble架构下HIDL服务查询过程_found dead hwbinder service-程序员宅基地