FPGA 20个例程篇:9.DDR3内存颗粒初始化写入并通过RS232读取(下)-程序员宅基地

技术标签: FPGA 20个例程 fpga开发

四、内存颗粒缓存,进阶之路

9.DDR3内存颗粒初始化写入并通过RS232读取

在介绍了DDR3内存颗粒的硬件设计、总结了MIG IP核官方手册的关键时序、说明了MIG IP核初始配置的详细细节后,就到了最重要的部分即完成整个例程的代码设计。

在这个例程中我们实现如下功能:在豌豆开发板上电后,从DDR3内存颗粒的0到255*16*8的地址空间中遍历写入256*128*16bits数据,前面也介绍了DDR3的burst突发长度默认最少是8,1颗DDR3内存颗粒对应的数据位宽是16bit,这就意味着每次读写数据的数量最少是8*16bit=128bit。

在程序设计中,我们使用了连续性读写的方式且设置一次性读写16个突发长度的地址,即一次性读写8 bit *16=128bit连续的地址空间,当然在后期项目实战中也可以设置成一次性读写32、64个突发长度的地址空间,而这里选择一次性读写16个突发长度的地址空间主要为了是方便向串口发送256字节的数据,因为256个字节数据刚好对应一次性读取16个突发长度的地址空间,而从DDR3内存颗粒的0到255*16*8的地址空间中遍历写入,则对应了256次写入操作。

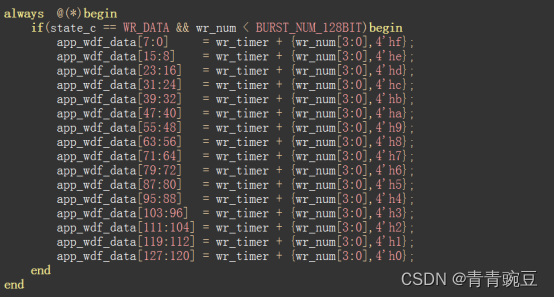

对于用户端在使用MIG IP核时,每个周期写入的128bit即16字节数据,而这16字节的数据按照如下方式写入:8位的写入操作次数+高4位的写入突发长度次数+低4位的0-15的递增循环拼接,具体细节详见下面的代码设计,这样就实现了对256次的写入操作,每次操作一次性写入16次128bit的数据,即写入连续性的128个地址空间内一共256字节数据,而每次操作一次性写入的256个数据,都是以当前写入操作的次数为初始值,按照0-255的顺序逐一循环递增。

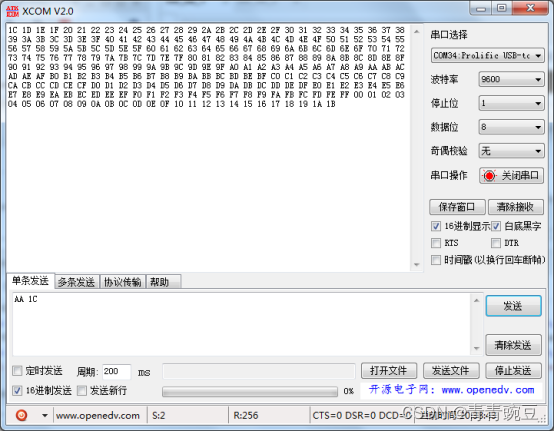

为了验证MIG IP核对于DDR3内存颗粒写入的正确性,例程中设计从串口调试助手发送报文比如8''hAA,8'h1C。其中AA和前面例程一样是固定的报文头,1C是读取DDR3内存颗粒的具体物理地址,FPGA在收到读取请求和读取地址后,即对DDR3内存颗粒发起一次读操作,读操作和写操作相似即一次性读取16次128bit的数据,也就是读取连续性的128个地址空间内一共256字节数据,如图1所示是串口助手发送读DDR3内存颗粒的物理地址指令,大家可以清楚地看到从DDR3内存颗粒读取的数据和我们写入的数据也是完全相同的。

图1 串口助手发送读DDR3内存颗粒的物理地址指令

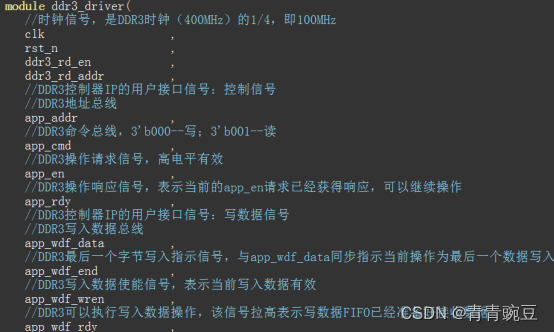

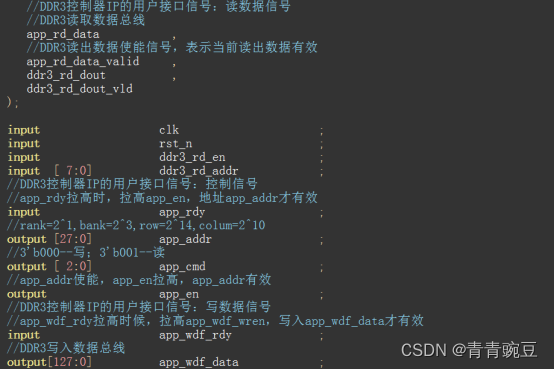

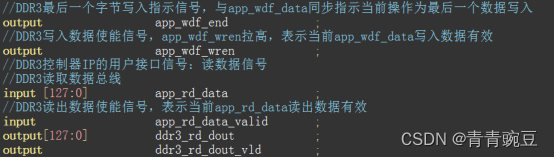

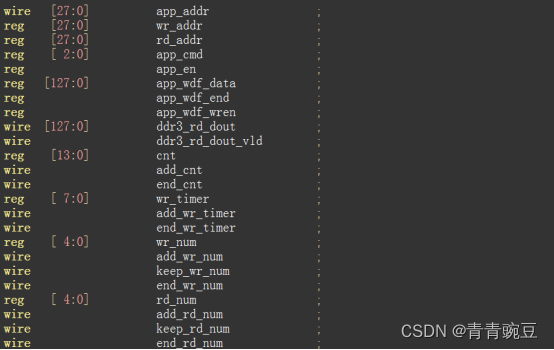

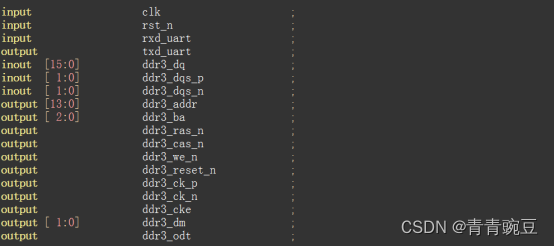

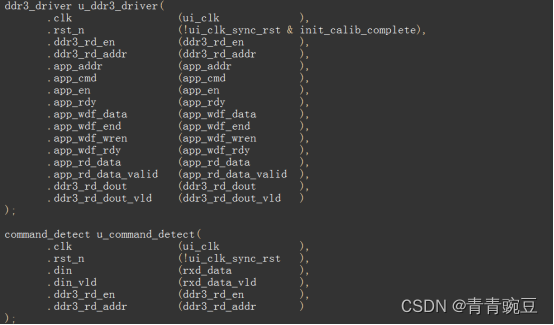

下面笔者为大家详细介绍这个例程中关键DDR3驱动模块ddr3_driver的代码设计,如表1所示是该模块的信号列表,模块实现如下功能:1.初始化从DDR3内存颗粒的0到255*16*8的地址空间中遍历写入256*128*16bits数据;2.从上游模块传入读DDR3使能信号ddr3_rd_en和读DDR3地址信号ddr3_rd_addr后,即发起读指定地址空间操作,一次性读取16次128bit的数据,通过ddr3_rd_dout和ddr3_rd_dout_vld信号送下游模块;3.实现一次性连续读写16个突发长度的地址空间的时序逻辑。

忘记MIG IP核读写逻辑的朋友,请回头再看一下上一篇博客,实际上对用户端的FPGA设计,我们只需要用代码还原官方手册的时序逻辑即可,简单地概括起来,对于DDR3的读写操作,在时序设计上有如下几个要点需要注意:

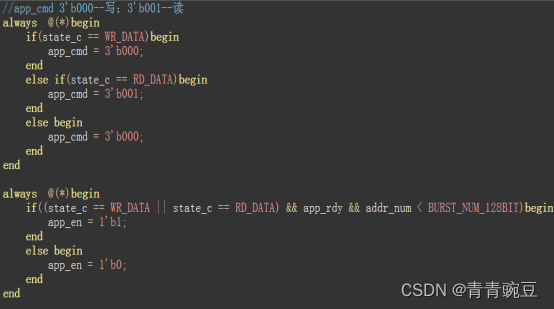

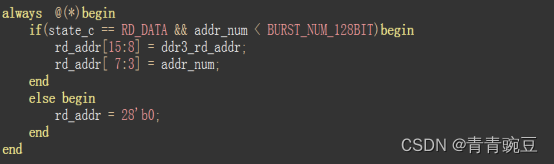

1. 不管对于写数据还是读数据,都需要进行读写地址操作,注意官方手册给出的时序要求,app_cmd、app_addr、app_en和app_rdy四个信号一定要对齐,其中app_rdy是由MIG IP核所产生的输出信号,另外三个信号均由用户端产生并输出到MIG IP核,app_cmd在写地址时为0,在读地址时为1,app_addr是当前读写的具体地址空间,在app_rdy为高时去拉高app_en,则此时app_cmd和app_addr均有效输入到MIG IP核;

2. 对于写数据操作,和读写地址操作相类似,也是四个信号app_wdf_data、app_wdf_rdy、app_wdf_wren、app_wdf_end一定要对齐,一样的其中app_wdf_rdy是由MIG IP核所产生的输出信号,另外三个信号均由用户端产生并输出到MIG IP核,当MIG IP核默认突发长度为8时,app_wdf_end和app_wdf_wren相同,在app_wdf_rdy为高时去拉高app_wdf_wren,则此时app_wdf_data数据有效输入到MIG IP核;

3. 对于读数据操作,用户只用等待MIG IP核的输入app_rd_data_valid数据有效信号被拉高时读取app_rd_data数据即可;

4. 因为MIG IP核默认突发长度为8,所以读写的地址空间需要以8为最小单位进行递增,一般性地为了充分发挥DDR3的速度优势,在程序设计中用户均会采取连续性读写,即一次性连续读写多个突发长度的地址空间,比如在做图像视频处理时选择读写连续的32和64个突发长度居多;

5. 读写数据的顺序和请求读写地址的顺序是相互对应的。

| 信号列表 |

||

| 信号名 |

I/O |

位宽 |

| clk |

I |

1 |

| rst_n |

I |

1 |

| ddr3_rd_en |

I |

1 |

| ddr3_rd_addr |

I |

8 |

| app_rdy |

I |

8 |

| app_addr |

O |

28 |

| app_cmd |

O |

3 |

| app_en |

O |

1 |

| app_wdf_rdy |

I |

1 |

| app_wdf_data |

O |

128 |

| app_wdf_end |

O |

1 |

| app_wdf_wren |

O |

1 |

| app_rd_data |

I |

128 |

| app_rd_data_valid |

I |

1 |

| ddr3_rd_dout |

O |

128 |

| ddr3_rd_dout_vld |

O |

1 |

表1 ddr3_driver模块信号列表

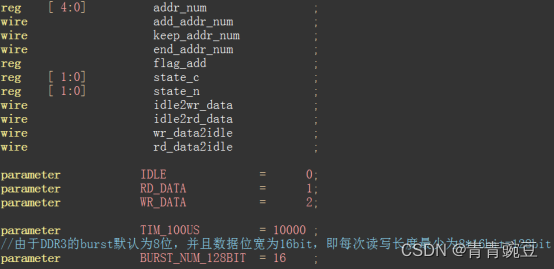

在搞清楚这些关键性的设计信息后,就可以去动手完成DDR3驱动模块ddr3_driver的代码设计,在笔者刚接触MIG IP核的时候,也参考了市面上很多开发板和培训机构的代码,实话实说太多数都不好理解,读写DDR3的状态机中夹杂了很多限制可能是迭代仿真改写逻辑后的结果,不光是对初学者很不友好,甚至工作多年的FPGA工程师也很难验证正确性,这样的代码用到项目工程中是一种隐患。

在设计FPGA时序逻辑的时候,笔者喜欢遵循最简单明了的设计方法,把复杂需求层层模块细化,然后每个模块中再去实现具体的逻辑化难为易。

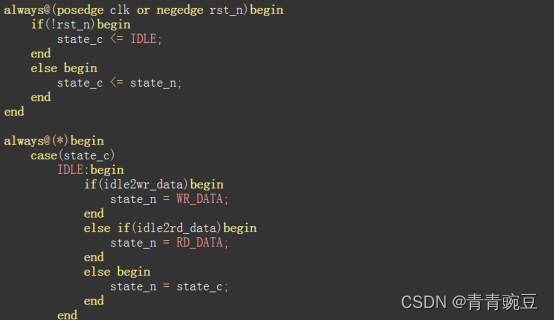

在ddr3_driver模块的设计中,注意到读写地址操作和读写数据操作的顺序是相互对应的,所以我们可以把一次性连续读写16个突发长度的地址空间做成一个状态机,即为空闲状态、写数据状态、读数据状态。

细心的同学不难发现,对于MIG IP核的读写操作,有两组信号需要用户端去刻意对齐,即在读写地址操作时,app_cmd、app_addr、app_en和app_rdy四个信号要对齐;在写数据操作时,app_wdf_data、app_wdf_rdy、app_wdf_wren和app_wdf_end四个信号也要对齐,并且对于用户端来说,app_rdy和app_wdf_rdy信号均是由MIG IP核产生的不可控。实际上笔者通过Modelsim仿真也好,ILA调试也好,观察到app_rdy和app_wdf_rdy信号在一般情况下都是高,但也存在间断性被拉低若干个周期的情况。

整个程序设计中的难点,笔者认为一方面在于用户需要把app_cmd、app_addr、app_en、app_rdy以及app_wdf_data、app_wdf_rdy、app_wdf_wren、app_wdf_end两组信号做对齐操作,另一方面读写状态机的设计中,读写地址操作和读写数据操作是相互独立的,因为对用户来说,app_rdy、app_wdf_rdy、app_rd_data_valid三个信号均是由MIG IP核产生的,而读写状态机中又需要一次性连续读写16个突发长度的地址空间,所以程序中要在读写状态中判断读写操作和读写数据都响应了16次,即在写数据时app_rdy、app_wdf_rdy都已有效16次,在读数据时app_rdy、app_rd_data_valid都已有效16次才说明一次性读写16个突发长度的地址空间成功,状态机方可跳转。

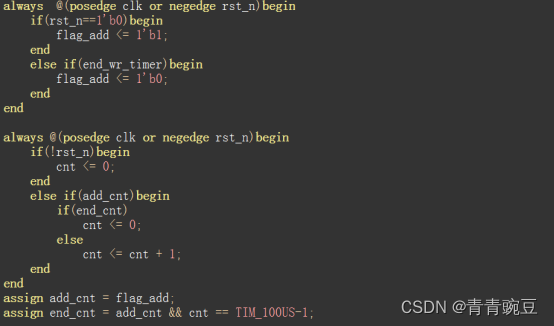

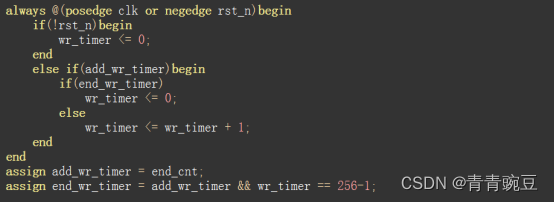

对于两组需要用户对齐的四个信号,用读写地址操作的app_cmd、app_addr、app_en、app_rdy画图说明,同样地对写数据操作的app_wdf_data、app_wdf_rdy、app_wdf_wren、app_wdf_end也适用,这里显然需要用计数器去计数app_rdy,同时根据该计数器的值实现app_addr读写地址的逐次加8操作,考虑关键性的两点设计要求,即四个操作信号相对齐和读写地址数据相对应,所以简单明了地这里用组合逻辑来实现操作信号对齐,用计数器不规则计数来实现地址数据对应。

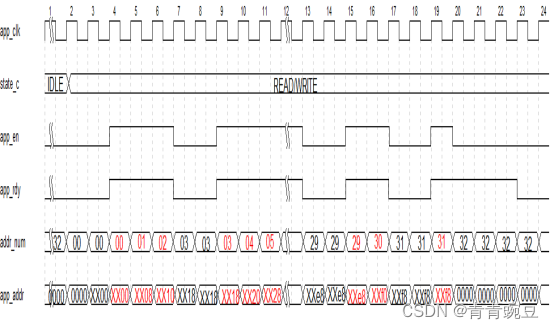

如图2所示是MIG IP核读写地址操作的时序示意图,这里用一次性连续读写32个突发长度的地址空间举例,大家可以清楚地看到因为用了组合逻辑,相比时序逻辑不会产生一个时钟周期的延迟,在图中笔者也把读写地址有效的数据都用了红色标记,用计数器不规则计数即计数到32,等待读写数据也计数到32,再去进行状态机跳转和计数器清零操作,整个逻辑设计清爽明朗,没有生搬硬凑的地方。

图2 MIG IP核读写地址操作的时序示意图

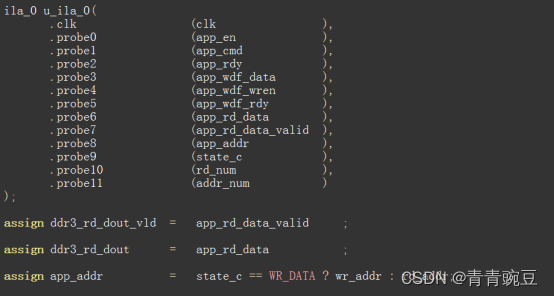

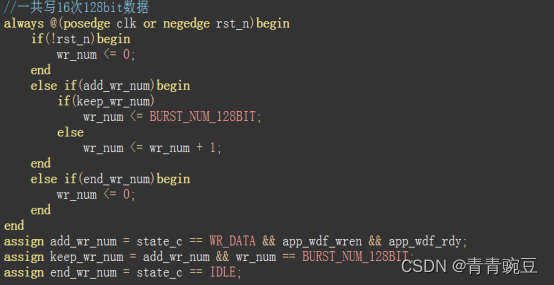

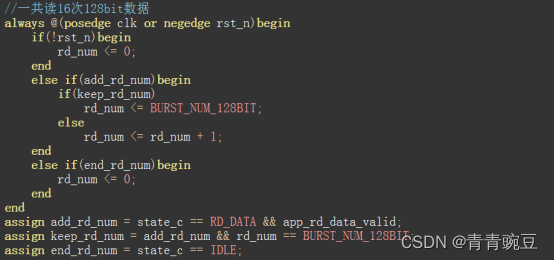

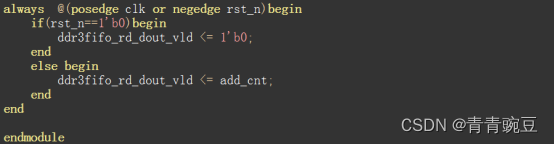

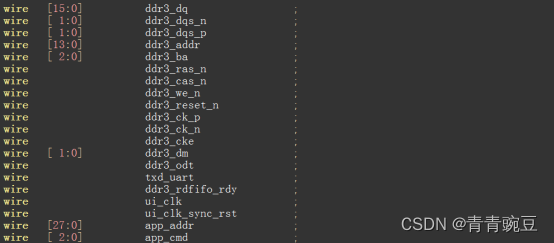

如图3所示是DDR3驱动模块ddr3_driver的代码设计供朋友们参考,因为用了组合逻辑去产生app_cmd、app_en、app_wdf_wren、app_wdf_end、app_addr、app_wdf_data等MIG IP核重要的输入信号,所以这里就很容易实现一组信号对齐;因为用了计数器不规则计数即读写地址和读写数据两个计数器都等待对方计数完成后再同时清零,所以这里也就很容易实现地址和数据的顺序对应,本模块也已经成功应用在批量转产的项目当中。

图3 DDR3驱动模块的代码设计

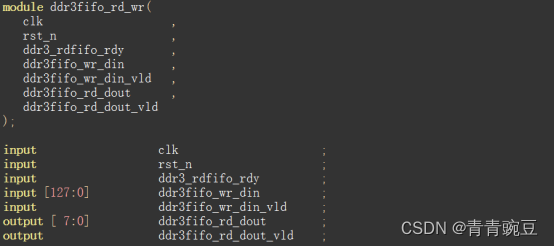

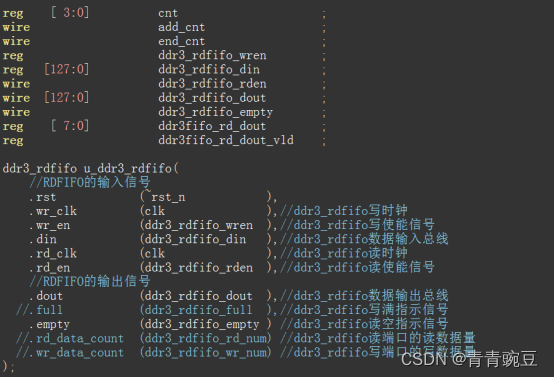

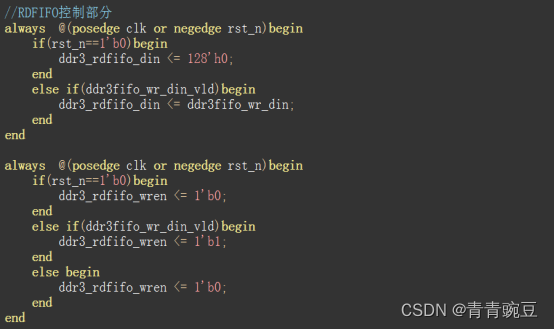

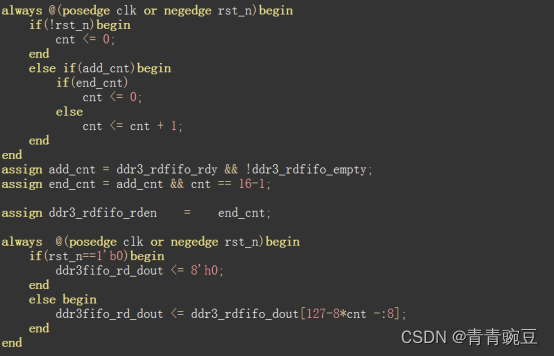

设计完DDR3驱动模块后,还需要把从DDR3内存颗粒里读取的数据写入一个FIFO,再通过读取FIFO将数据打印到串口助手上显示,当然后期的例程中笔者会把读写DDR3的两个FIFO和MIG IP核都放到DDR3的控制模块中,方便朋友们项目中的二次开发,如表2所示是该模块的信号列表,如图4-29所示是DDR3读取数据FIFO缓存模块的代码设计,在这个模块中也实现了数据拼接功能,因为上游模块中从MIG IP核读取的数据位宽是128bit,而下游串口助手需要一个个字节8bit打印,其实这些在“FPGA基础知识”专栏中已经详细说明了,忘记的同学再回过头复习下即可。

| 信号列表 |

||

| 信号名 |

I/O |

位宽 |

| clk |

I |

1 |

| rst_n |

I |

1 |

| ddr3_rdfifo_rdy |

I |

1 |

| ddr3fifo_wr_din |

I |

128 |

| ddr3fifo_wr_din_vld |

I |

1 |

| ddr3fifo_rd_dout |

O |

8 |

| ddr3fifo_rd_dout_vld |

O |

1 |

表2 ddr3fifo_rd_wr模块信号列表

图4 DDR3读取数据FIFO缓存模块的代码设计

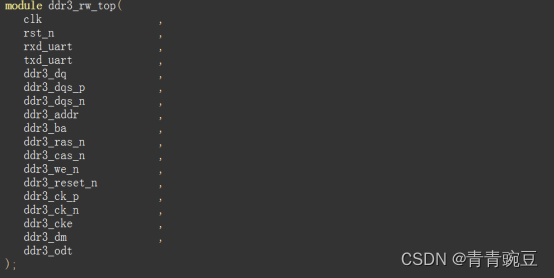

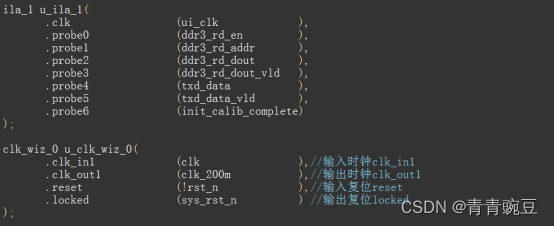

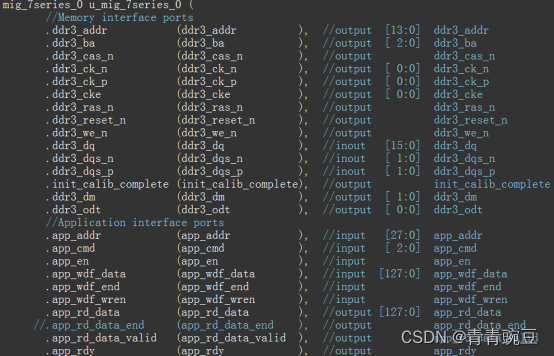

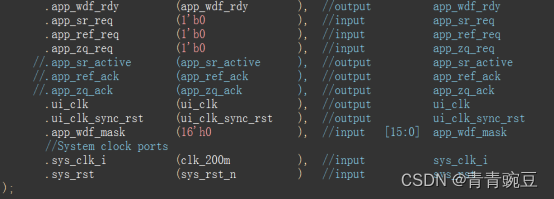

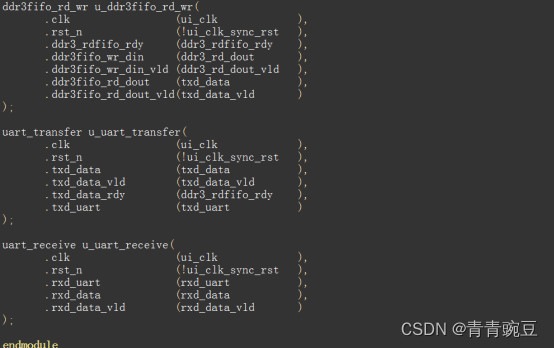

如图5所示串口读取DDR3内存颗粒顶层文件的例化,其中有三个地方需要注意:1.MIG IP核配置时候选择了输出ui_clk用户时钟,这个时钟是100Mhz的,在串口收发模块中使用了该时钟所以同样9600的波特率,需要调整一下收发计数器的计数周期;2. MIG IP核需要200Mhz时钟作为输入时钟,这里用了PLL IP核倍频输入;3.MIG IP核会产生init_calib_complete输出信号,因为DDR3上电后内部也需要初始化操作,所以当该信号为高时,才可以对DDR3内存颗粒进行读写操作。

图5 串口读取DDR3内存颗粒顶层文件的例化

智能推荐

c# 调用c++ lib静态库_c#调用lib-程序员宅基地

文章浏览阅读2w次,点赞7次,收藏51次。四个步骤1.创建C++ Win32项目动态库dll 2.在Win32项目动态库中添加 外部依赖项 lib头文件和lib库3.导出C接口4.c#调用c++动态库开始你的表演...①创建一个空白的解决方案,在解决方案中添加 Visual C++ , Win32 项目空白解决方案的创建:添加Visual C++ , Win32 项目这......_c#调用lib

deepin/ubuntu安装苹方字体-程序员宅基地

文章浏览阅读4.6k次。苹方字体是苹果系统上的黑体,挺好看的。注重颜值的网站都会使用,例如知乎:font-family: -apple-system, BlinkMacSystemFont, Helvetica Neue, PingFang SC, Microsoft YaHei, Source Han Sans SC, Noto Sans CJK SC, W..._ubuntu pingfang

html表单常见操作汇总_html表单的处理程序有那些-程序员宅基地

文章浏览阅读159次。表单表单概述表单标签表单域按钮控件demo表单标签表单标签基本语法结构<form action="处理数据程序的url地址“ method=”get|post“ name="表单名称”></form><!--action,当提交表单时,向何处发送表单中的数据,地址可以是相对地址也可以是绝对地址--><!--method将表单中的数据传送给服务器处理,get方式直接显示在url地址中,数据可以被缓存,且长度有限制;而post方式数据隐藏传输,_html表单的处理程序有那些

PHP设置谷歌验证器(Google Authenticator)实现操作二步验证_php otp 验证器-程序员宅基地

文章浏览阅读1.2k次。使用说明:开启Google的登陆二步验证(即Google Authenticator服务)后用户登陆时需要输入额外由手机客户端生成的一次性密码。实现Google Authenticator功能需要服务器端和客户端的支持。服务器端负责密钥的生成、验证一次性密码是否正确。客户端记录密钥后生成一次性密码。下载谷歌验证类库文件放到项目合适位置(我这边放在项目Vender下面)https://github.com/PHPGangsta/GoogleAuthenticatorPHP代码示例://引入谷_php otp 验证器

【Python】matplotlib.plot画图横坐标混乱及间隔处理_matplotlib更改横轴间距-程序员宅基地

文章浏览阅读4.3k次,点赞5次,收藏11次。matplotlib.plot画图横坐标混乱及间隔处理_matplotlib更改横轴间距

docker — 容器存储_docker 保存容器-程序员宅基地

文章浏览阅读2.2k次。①Storage driver 处理各镜像层及容器层的处理细节,实现了多层数据的堆叠,为用户 提供了多层数据合并后的统一视图②所有 Storage driver 都使用可堆叠图像层和写时复制(CoW)策略③docker info 命令可查看当系统上的 storage driver主要用于测试目的,不建议用于生成环境。_docker 保存容器

随便推点

网络拓扑结构_网络拓扑csdn-程序员宅基地

文章浏览阅读834次,点赞27次,收藏13次。网络拓扑结构是指计算机网络中各组件(如计算机、服务器、打印机、路由器、交换机等设备)及其连接线路在物理布局或逻辑构型上的排列形式。这种布局不仅描述了设备间的实际物理连接方式,也决定了数据在网络中流动的路径和方式。不同的网络拓扑结构影响着网络的性能、可靠性、可扩展性及管理维护的难易程度。_网络拓扑csdn

JS重写Date函数,兼容IOS系统_date.prototype 将所有 ios-程序员宅基地

文章浏览阅读1.8k次,点赞5次,收藏8次。IOS系统Date的坑要创建一个指定时间的new Date对象时,通常的做法是:new Date("2020-09-21 11:11:00")这行代码在 PC 端和安卓端都是正常的,而在 iOS 端则会提示 Invalid Date 无效日期。在IOS年月日中间的横岗许换成斜杠,也就是new Date("2020/09/21 11:11:00")通常为了兼容IOS的这个坑,需要做一些额外的特殊处理,笔者在开发的时候经常会忘了兼容IOS系统。所以就想试着重写Date函数,一劳永逸,避免每次ne_date.prototype 将所有 ios

如何将EXCEL表导入plsql数据库中-程序员宅基地

文章浏览阅读5.3k次。方法一:用PLSQL Developer工具。 1 在PLSQL Developer的sql window里输入select * from test for update; 2 按F8执行 3 打开锁, 再按一下加号. 鼠标点到第一列的列头,使全列成选中状态,然后粘贴,最后commit提交即可。(前提..._excel导入pl/sql

Git常用命令速查手册-程序员宅基地

文章浏览阅读83次。Git常用命令速查手册1、初始化仓库git init2、将文件添加到仓库git add 文件名 # 将工作区的某个文件添加到暂存区 git add -u # 添加所有被tracked文件中被修改或删除的文件信息到暂存区,不处理untracked的文件git add -A # 添加所有被tracked文件中被修改或删除的文件信息到暂存区,包括untracked的文件...

分享119个ASP.NET源码总有一个是你想要的_千博二手车源码v2023 build 1120-程序员宅基地

文章浏览阅读202次。分享119个ASP.NET源码总有一个是你想要的_千博二手车源码v2023 build 1120

【C++缺省函数】 空类默认产生的6个类成员函数_空类默认产生哪些类成员函数-程序员宅基地

文章浏览阅读1.8k次。版权声明:转载请注明出处 http://blog.csdn.net/irean_lau。目录(?)[+]1、缺省构造函数。2、缺省拷贝构造函数。3、 缺省析构函数。4、缺省赋值运算符。5、缺省取址运算符。6、 缺省取址运算符 const。[cpp] view plain copy_空类默认产生哪些类成员函数