【基础知识】~ FIFO-程序员宅基地

技术标签: fpga开发 IC设计/验证、FPGA

本章目录:

1. 了解FIFO

1.1 定义

FIFO(First In First Out),即先进先出队列。FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构。触发导向传输结构的FIFO是由寄存器阵列构成的,零导向传输结构的FIFO是由具有读和写地址指针的双口RAM构成。

FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。它与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定的地址。

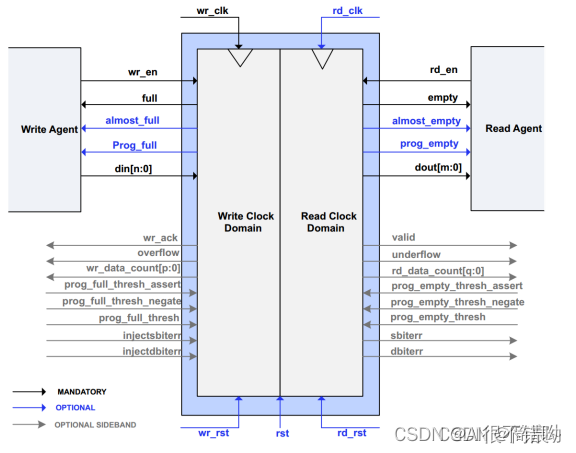

根据 FIFO 工作的时钟域,可以将 FIFO 分为同步 FIFO 和异步 FIFO。同步 FIFO 是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。异步 FIFO 是指读写时钟不一致,读写时钟是互相独立的。 Xilinx 的 FIFO IP 核可以被配置为同步 FIFO 或异步 FIFO,其信号框图如下图所示。从图中可以了解到,当被配置为同步 FIFO 时,只使用 wr_clk,所有的输入输出信号都同步于 wr_clk 信号。而当被配置为异步 FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟 wr_clk,所有与读相关的信号都是同步于读时钟 rd_clk。

1.2 FIFO有什么用处?

- 跨时钟域

- 在将数据发送到芯片外之前将其缓冲(例如,发送到DRAM或SRAM)

- 缓冲数据以供软件在以后查看

- 存储数据以备后用

1.3 FIFO的参数有哪些?

宽度:一次读写操作的数据位

深度:可以存储的 N 位数据的数目(宽度为 N)

满标志: full。FIFO 已满时,由 FIFO 的状态电路送出的信号,阻止 FIFO 写操作

空标志: empty。FIFO 已空时,由 FIFO 的状态电路送出的信号,阻止 FIFO 读操作

读时钟:读操作所遵循的时钟

写时钟:写操作所遵循的时钟

2. 同步FIFO

2.1 原理

典型同步FIFO由三部分组成:FIFO写控制逻辑、FIFO读控制逻辑、FIFO存储实体。

FIFO写控制逻辑主要功能:产生FIFO写地址、写有效信号,同时产生FIFO写满、写错等状态信号;

FIFO读控制逻辑主要功能:产生FIFO读地址、读有效信号,同时产生FIFO读空、读错等状态信号。

FIFO读写过程的地址控制如下图所示:

当FIFO初始化(复位)时,fifo_write_addr与fifo_read_addr同指到0x0,此时FIFO处于空状态;

当FIFO进行写操作时,fifo_write_addr递增(增加到FIFO DEPTH时回绕),与fifo_read_addr错开,此时FIFO处于非空状态;

当FIFO进行读操作时,fifo_read_addr递增。

FIFO空满状态产生:

为产生FIFO空满标志,引入Count 计数器,用于指示FIFO内部存储数据个数;

当只有写操作时,Count加1;只有读操作时,Count减1;其它情况下,保持不变;

Count为0时,说明FIFO为空,fifo_empty置位;

Count等于FIFO_DEPTH时,说明FIFO已满,fifo_full置位。

2.2 代码

参照博客

3. 异步FIFO

3.1 原理

异步FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wr_en)和写数据(wr_data)、与读时钟同步的读有效(rd_en)和读数据(rd_data)。为了实现正确的读写和避免FIFO的上溢或下溢,通常还应该给出与读时钟和写时钟同步的FIFO的空标志(empty)和满标志(full)以禁止读写操作。

写地址产生模块还根据读地址和写地址关系产生FIFO的满标志。当wren有效时,若写地址+2=读地址时,full为1;当wren无效时,若写地址+ 1=读地址时,full为1。读地址产生模块还根据读地址和写地址的差产生FIFO的空标志。当rden有效时,若写地址-1=读地址时,empty为 1;当rden无效时,若写地址=读地址时,empty为1。按照以上方式产生标志信号是为了提前一个时钟周期产生对应的标志信号。

由于空标志和满标志控制了FIFO的操作,因此标志错误会引起操作的错误。如上所述,标志的产生是通过对读写地址的比较产生的,当读写时钟完全异步时,对读写地址进行比较时,可能得出错误的结果。例如,在读地址变化过程中,由于读地址的各位变化并不同步,计算读写地址的差值,可能产生错误的差值,导致产生错误的满标志信号。若将未满标志置为满标志时,可能降低了应用的性能,降低写数据速率;而将满置标志置为未满时,执行一次写操作,则可能产生溢出错误,这对于实际应用来说是绝对应该避免的。空标志信号的产生也可能产生类似的错误。

3.2 最小深度计算

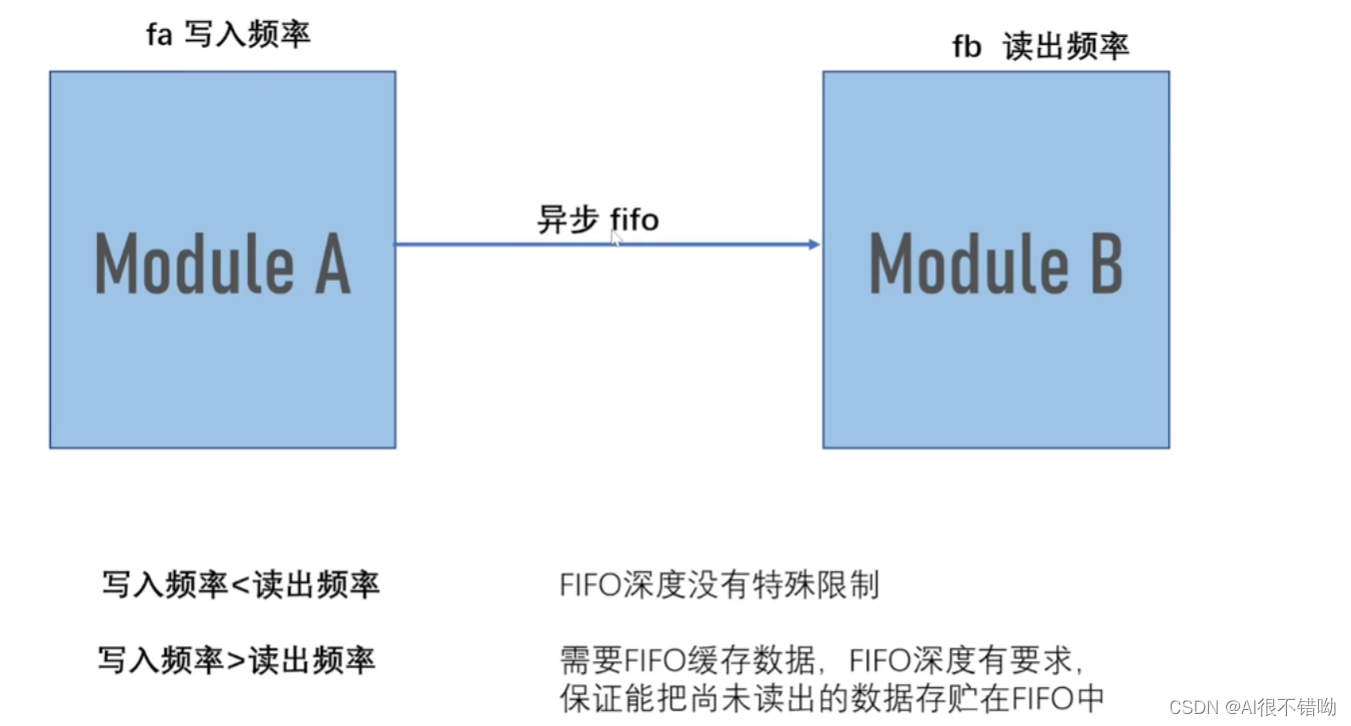

对于异步FIFO而言,无非就是写入频率大于或者小于读出频率呗!然而,对于写入频率 小于 读出频率,意味着写的慢,读的快,会怎样?那肯定是对你的FIFO深度没有要求了呀!你没了我就不读了呗。重要的是看另一种情况:写入大于读出,那就需要FIFO进行储存,既然储存,那肯定得有深度要求!

3.2.1 需要用到FIFO最小深度的情况

大概有以下四种情况:(以上图为例)

- fa>fb并且没有空闲(IDLE)周期;

- fa>fb并且有空闲(IDLE)周期;

- fa<fb并且有空闲(IDLE)周期;

- fa<fb并且随机读写;

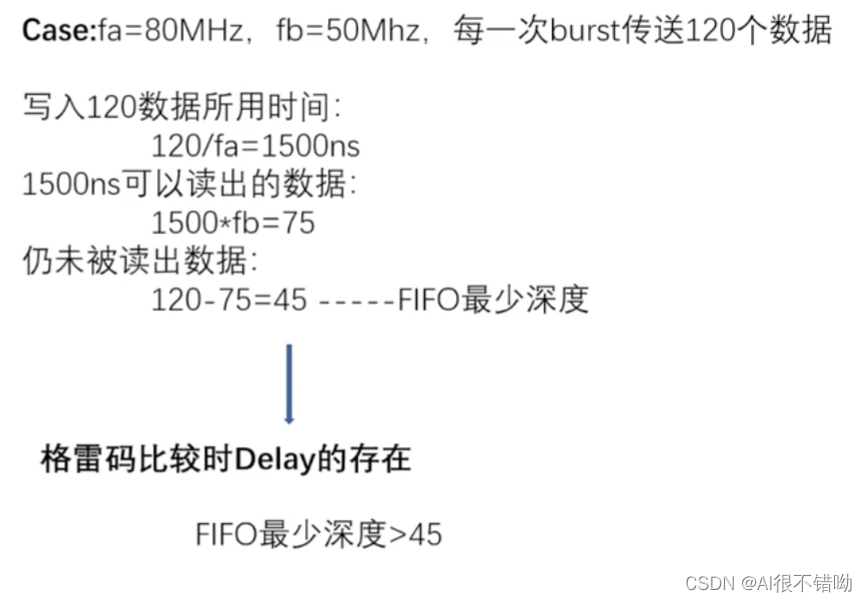

3.2.2 fa>fb并且没有空闲(IDLE)周期

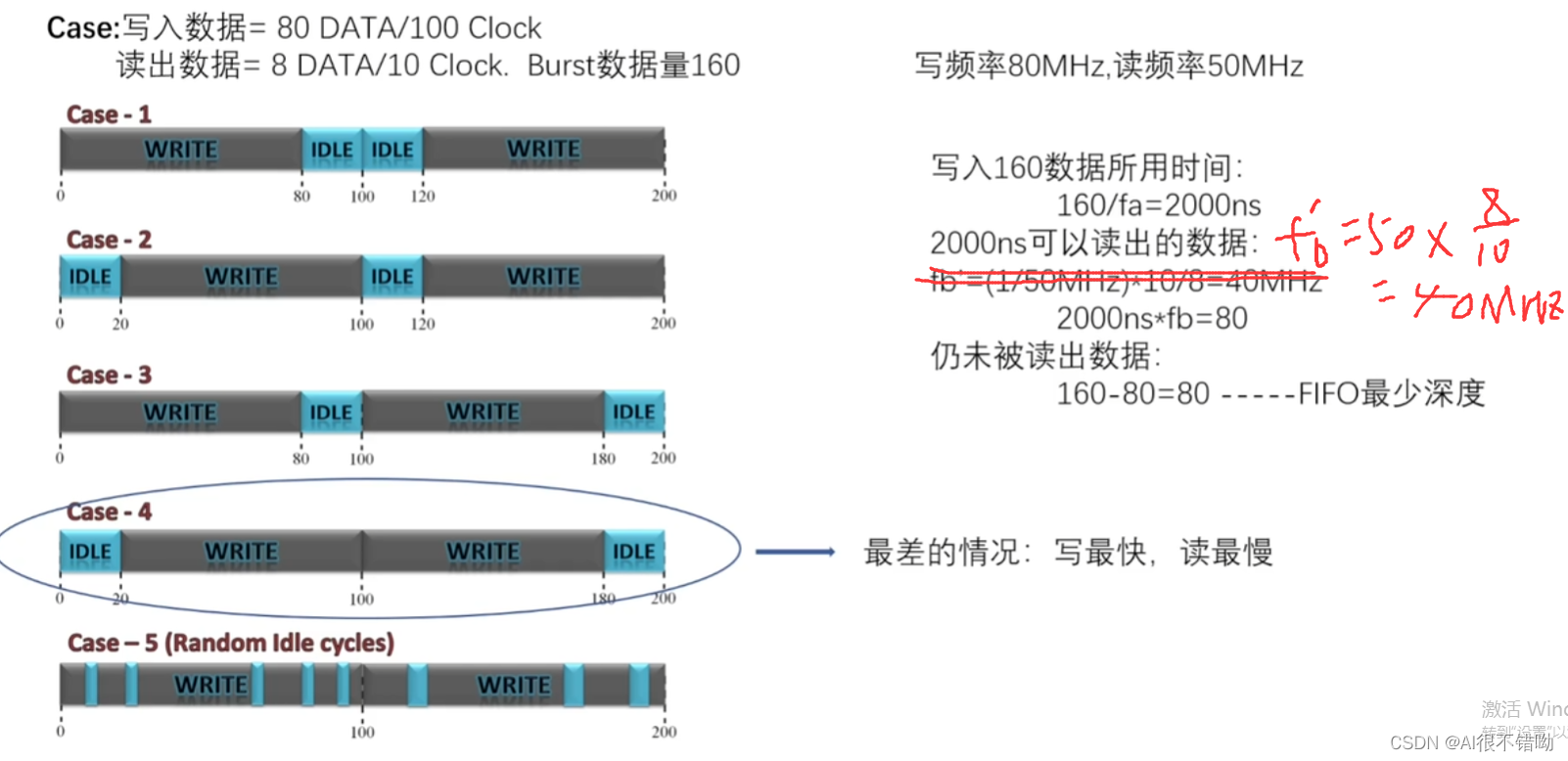

上边这种情况,通过一个例子可以看出来,此时需要FIFO深度。

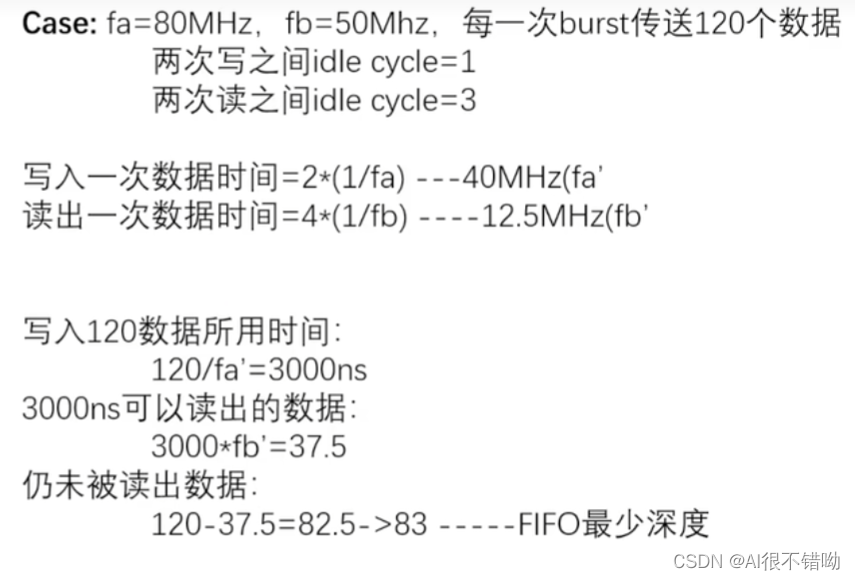

3.2.3 fa>fb并且有空闲(IDLE)周期

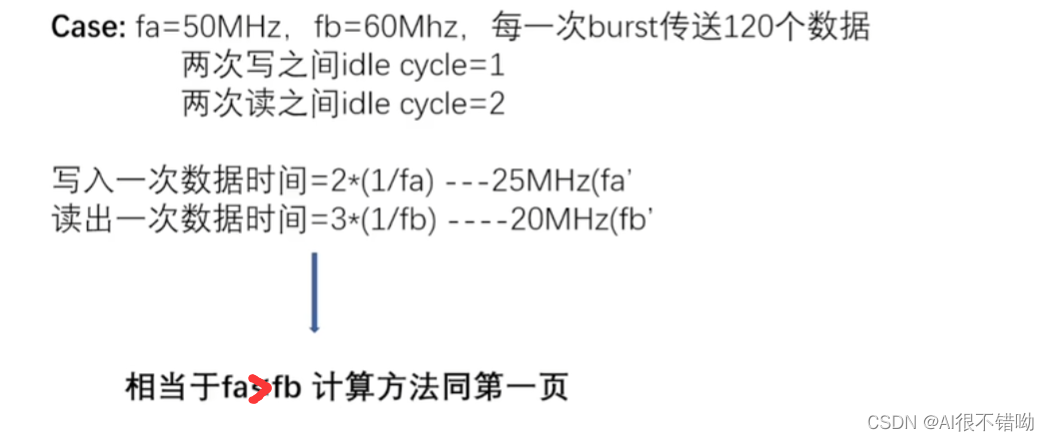

3.2.4 fa<fb并且有空闲(IDLE)周期

3.2.5 fa<fb并且随机读写

通过理解这个例子,我们就可以知道为什么会有下边总结的这些公式了===>

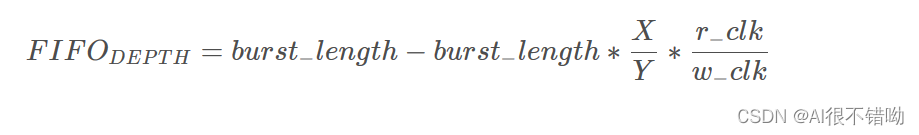

3.2.6 总结最后一种情况的公式

写时钟频率w_clk

读时钟频率 r_clk,

写时钟周期里,每B个时钟周期会有A个数据写入FIFO

读时钟周期里,每Y个时钟周期会有X个数据读出FIFO

举例说明:

假设 FIFO 的写时钟为 100MHZ,读时钟为 80MHZ。在 FIFO 输入侧,每 100 个时钟,写入80 个数据;FIFO 读入测,每个时钟读取一个数据。设计合理的 FIFO 深度,使 FIFO 不会溢出:考虑背靠背(20个clk不发数据+80clk发数据+80clk发数据+20个clk不发数据的200个clk)代入公式可计算FIFO的深度:160-1601(80/100)=32.

3.3 代码实现

参考博客

4. 小试牛刀

基础知识学完之后,那就小试牛刀!

VL22 同步FIFO

代码如下:

`timescale 1ns/1ns

/**********************************RAM************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/**********************************SFIFO************************************/

module sfifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input clk ,

input rst_n ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output reg wfull ,

output reg rempty ,

output wire [WIDTH-1:0] rdata

);

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 如何操作

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

waddr <= 1'b0;

end

else begin

if(winc && !wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

//读地址 如何操作

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

raddr <= 1'b0;

end

else begin

if(rinc && !rempty) begin

raddr <= raddr + 1'b1;

end

else begin

raddr <= raddr;

end

end

end

//空满判断

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

wfull <= 1'b0;

rempty <= 1'b0;

end

else begin

wfull <= (waddr == {

~raddr[ADDR_WIDTH], raddr[ADDR_WIDTH-1:0]});

rempty <= (raddr == waddr);

end

end

// 实例化

dual_port_RAM #(.DEPTH(DEPTH),

.WIDTH(WIDTH)) dual_port_RAM_0 (.wclk(clk),

.wenc(winc),

.waddr(waddr[ADDR_WIDTH-1:0]),

.wdata(wdata),

.rclk(clk),

.renc(rinc),

.raddr(raddr[ADDR_WIDTH-1:0]),

.rdata(rdata));

endmodule

VL21 异步FIFO

代码如下:

`timescale 1ns/1ns

/***************************************RAM*****************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/***************************************AFIFO*****************************************/

module asyn_fifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input wclk ,

input rclk ,

input wrstn ,

input rrstn ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output wire wfull ,

output wire rempty ,

output wire [WIDTH-1:0] rdata

);

// 本地参数

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 操作

always @ (posedge wclk or negedge wrstn) begin

if(!wrstn) begin

waddr <= 'b0;

end

else begin

if(winc && !wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

// 读地址 操作

always @ (posedge rclk or negedge rrstn) begin

if(!rrstn) begin

raddr <= 'b0;

end

else begin`timescale 1ns/1ns

/***************************************RAM*****************************************/

module dual_port_RAM #(parameter DEPTH = 16,

parameter WIDTH = 8)(

input wclk

,input wenc

,input [$clog2(DEPTH)-1:0] waddr //深度对2取对数,得到地址的位宽。

,input [WIDTH-1:0] wdata //数据写入

,input rclk

,input renc

,input [$clog2(DEPTH)-1:0] raddr //深度对2取对数,得到地址的位宽。

,output reg [WIDTH-1:0] rdata //数据输出

);

reg [WIDTH-1:0] RAM_MEM [0:DEPTH-1];

always @(posedge wclk) begin

if(wenc)

RAM_MEM[waddr] <= wdata;

end

always @(posedge rclk) begin

if(renc)

rdata <= RAM_MEM[raddr];

end

endmodule

/***************************************AFIFO*****************************************/

module asyn_fifo#(

parameter WIDTH = 8,

parameter DEPTH = 16

)(

input wclk ,

input rclk ,

input wrstn ,

input rrstn ,

input winc ,

input rinc ,

input [WIDTH-1:0] wdata ,

output wire wfull ,

output wire rempty ,

output wire [WIDTH-1:0] rdata

);

// 本地参数

localparam ADDR_WIDTH = $clog2(DEPTH);

reg [ADDR_WIDTH:0] waddr;

reg [ADDR_WIDTH:0] raddr;

// 写地址 操作

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

waddr <= 'b0;

end

else begin

if(winc && ~wfull) begin

waddr <= waddr + 1'b1;

end

else begin

waddr <= waddr;

end

end

end

// 读地址 操作

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

raddr <= 'b0;

end

else begin

if(rinc && ~rempty) begin

raddr <= raddr + 1'b1;

end

else begin

raddr <= raddr;

end

end

end

// 二进制 转 格雷码

wire [ADDR_WIDTH:0] waddr_gray;

wire [ADDR_WIDTH:0] raddr_gray;

assign waddr_gray = waddr ^ (waddr>>1);

assign raddr_gray = raddr ^ (raddr>>1);

// 因为上边转码的时候是 组合逻辑赋值,为了避免出现亚稳态,这里打一拍

reg [ADDR_WIDTH:0] waddr_gray_reg;

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

waddr_gray_reg <= 'd0;

end

else begin

waddr_gray_reg <= waddr_gray;

end

end

//因为上边转码的时候是 组合逻辑赋值,为了避免出现亚稳态,这里打一拍

reg [ADDR_WIDTH:0] raddr_gray_reg;

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

raddr_gray_reg <= 'd0;

end

else begin

raddr_gray_reg <= raddr_gray;

end

end

// 读时钟域 同步到 写时钟域 ===> 跨时钟域,打两拍

reg [ADDR_WIDTH:0] addr_r2w_temp;

reg [ADDR_WIDTH:0] addr_r2w;

always @ (posedge wclk or negedge wrstn) begin

if(~wrstn) begin

addr_r2w_temp <= 'd0;

addr_r2w <= 'd0;

end

else begin

addr_r2w_temp <= raddr_gray_reg;

addr_r2w <= addr_r2w_temp;

end

end

// 写时钟域 同步到 读时钟域 ===> 跨时钟域,打两拍

reg [ADDR_WIDTH:0] addr_w2r_temp;

reg [ADDR_WIDTH:0] addr_w2r;

always @ (posedge rclk or negedge rrstn) begin

if(~rrstn) begin

addr_w2r_temp <= 'd0;

addr_w2r <= 'd0;

end

else begin

addr_w2r_temp <= waddr_gray_reg;

addr_w2r <= addr_w2r_temp;

end

end

// 空满判断

assign wfull = (waddr_gray_reg == {

~addr_r2w[ADDR_WIDTH:ADDR_WIDTH-1], addr_r2w[ADDR_WIDTH-2:0]});

assign rempty = (raddr_gray_reg == addr_w2r);

dual_port_RAM #(.DEPTH(DEPTH),

.WIDTH(WIDTH)) dual_port_RAM_0 (.wclk(wclk),

.wenc(winc && ~wfull),

.waddr(waddr[ADDR_WIDTH-1:0]),

.wdata(wdata),

.rclk(rclk),

.renc(rinc && ~rempty),

.raddr(raddr[ADDR_WIDTH-1:0]),

.rdata(rdata));

endmodule

这里遇到一个问题,反复查看代码,怎么也找不出来,哭了!!!

最后一查,实例化RAM的时候,有个线连错了,最后通过,奥里给!!!

==========================================================================================

参考文献

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得收藏+评论!!!

智能推荐

使用nginx解决浏览器跨域问题_nginx不停的xhr-程序员宅基地

文章浏览阅读1k次。通过使用ajax方法跨域请求是浏览器所不允许的,浏览器出于安全考虑是禁止的。警告信息如下:不过jQuery对跨域问题也有解决方案,使用jsonp的方式解决,方法如下:$.ajax({ async:false, url: 'http://www.mysite.com/demo.do', // 跨域URL ty..._nginx不停的xhr

在 Oracle 中配置 extproc 以访问 ST_Geometry-程序员宅基地

文章浏览阅读2k次。关于在 Oracle 中配置 extproc 以访问 ST_Geometry,也就是我们所说的 使用空间SQL 的方法,官方文档链接如下。http://desktop.arcgis.com/zh-cn/arcmap/latest/manage-data/gdbs-in-oracle/configure-oracle-extproc.htm其实简单总结一下,主要就分为以下几个步骤。..._extproc

Linux C++ gbk转为utf-8_linux c++ gbk->utf8-程序员宅基地

文章浏览阅读1.5w次。linux下没有上面的两个函数,需要使用函数 mbstowcs和wcstombsmbstowcs将多字节编码转换为宽字节编码wcstombs将宽字节编码转换为多字节编码这两个函数,转换过程中受到系统编码类型的影响,需要通过设置来设定转换前和转换后的编码类型。通过函数setlocale进行系统编码的设置。linux下输入命名locale -a查看系统支持的编码_linux c++ gbk->utf8

IMP-00009: 导出文件异常结束-程序员宅基地

文章浏览阅读750次。今天准备从生产库向测试库进行数据导入,结果在imp导入的时候遇到“ IMP-00009:导出文件异常结束” 错误,google一下,发现可能有如下原因导致imp的数据太大,没有写buffer和commit两个数据库字符集不同从低版本exp的dmp文件,向高版本imp导出的dmp文件出错传输dmp文件时,文件损坏解决办法:imp时指定..._imp-00009导出文件异常结束

python程序员需要深入掌握的技能_Python用数据说明程序员需要掌握的技能-程序员宅基地

文章浏览阅读143次。当下是一个大数据的时代,各个行业都离不开数据的支持。因此,网络爬虫就应运而生。网络爬虫当下最为火热的是Python,Python开发爬虫相对简单,而且功能库相当完善,力压众多开发语言。本次教程我们爬取前程无忧的招聘信息来分析Python程序员需要掌握那些编程技术。首先在谷歌浏览器打开前程无忧的首页,按F12打开浏览器的开发者工具。浏览器开发者工具是用于捕捉网站的请求信息,通过分析请求信息可以了解请..._初级python程序员能力要求

Spring @Service生成bean名称的规则(当类的名字是以两个或以上的大写字母开头的话,bean的名字会与类名保持一致)_@service beanname-程序员宅基地

文章浏览阅读7.6k次,点赞2次,收藏6次。@Service标注的bean,类名:ABDemoService查看源码后发现,原来是经过一个特殊处理:当类的名字是以两个或以上的大写字母开头的话,bean的名字会与类名保持一致public class AnnotationBeanNameGenerator implements BeanNameGenerator { private static final String C..._@service beanname

随便推点

二叉树的各种创建方法_二叉树的建立-程序员宅基地

文章浏览阅读6.9w次,点赞73次,收藏463次。1.前序创建#include<stdio.h>#include<string.h>#include<stdlib.h>#include<malloc.h>#include<iostream>#include<stack>#include<queue>using namespace std;typed_二叉树的建立

解决asp.net导出excel时中文文件名乱码_asp.net utf8 导出中文字符乱码-程序员宅基地

文章浏览阅读7.1k次。在Asp.net上使用Excel导出功能,如果文件名出现中文,便会以乱码视之。 解决方法: fileName = HttpUtility.UrlEncode(fileName, System.Text.Encoding.UTF8);_asp.net utf8 导出中文字符乱码

笔记-编译原理-实验一-词法分析器设计_对pl/0作以下修改扩充。增加单词-程序员宅基地

文章浏览阅读2.1k次,点赞4次,收藏23次。第一次实验 词法分析实验报告设计思想词法分析的主要任务是根据文法的词汇表以及对应约定的编码进行一定的识别,找出文件中所有的合法的单词,并给出一定的信息作为最后的结果,用于后续语法分析程序的使用;本实验针对 PL/0 语言 的文法、词汇表编写一个词法分析程序,对于每个单词根据词汇表输出: (单词种类, 单词的值) 二元对。词汇表:种别编码单词符号助记符0beginb..._对pl/0作以下修改扩充。增加单词

android adb shell 权限,android adb shell权限被拒绝-程序员宅基地

文章浏览阅读773次。我在使用adb.exe时遇到了麻烦.我想使用与bash相同的adb.exe shell提示符,所以我决定更改默认的bash二进制文件(当然二进制文件是交叉编译的,一切都很完美)更改bash二进制文件遵循以下顺序> adb remount> adb push bash / system / bin /> adb shell> cd / system / bin> chm..._adb shell mv 权限

投影仪-相机标定_相机-投影仪标定-程序员宅基地

文章浏览阅读6.8k次,点赞12次,收藏125次。1. 单目相机标定引言相机标定已经研究多年,标定的算法可以分为基于摄影测量的标定和自标定。其中,应用最为广泛的还是张正友标定法。这是一种简单灵活、高鲁棒性、低成本的相机标定算法。仅需要一台相机和一块平面标定板构建相机标定系统,在标定过程中,相机拍摄多个角度下(至少两个角度,推荐10~20个角度)的标定板图像(相机和标定板都可以移动),即可对相机的内外参数进行标定。下面介绍张氏标定法(以下也这么称呼)的原理。原理相机模型和单应矩阵相机标定,就是对相机的内外参数进行计算的过程,从而得到物体到图像的投影_相机-投影仪标定

Wayland架构、渲染、硬件支持-程序员宅基地

文章浏览阅读2.2k次。文章目录Wayland 架构Wayland 渲染Wayland的 硬件支持简 述: 翻译一篇关于和 wayland 有关的技术文章, 其英文标题为Wayland Architecture .Wayland 架构若是想要更好的理解 Wayland 架构及其与 X (X11 or X Window System) 结构;一种很好的方法是将事件从输入设备就开始跟踪, 查看期间所有的屏幕上出现的变化。这就是我们现在对 X 的理解。 内核是从一个输入设备中获取一个事件,并通过 evdev 输入_wayland