【FPGA】串口通信UART_uart串口通信在发送模块和接收模块加fifo-程序员宅基地

文章目录

一、UART串口通信

一、基本概念

串口是串行接口(serial port)的简称,也称为串行通信接口或COM接口。

串口通信是指采用串行通信协议(serial communication)在一条信号线上将数据一个比特一个比特地逐位进行传输的通信模式。

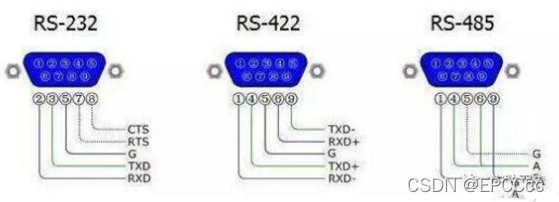

串口按电气标准及协议来划分,包括RS-232-C、RS-422、RS485等。

二、串口数据

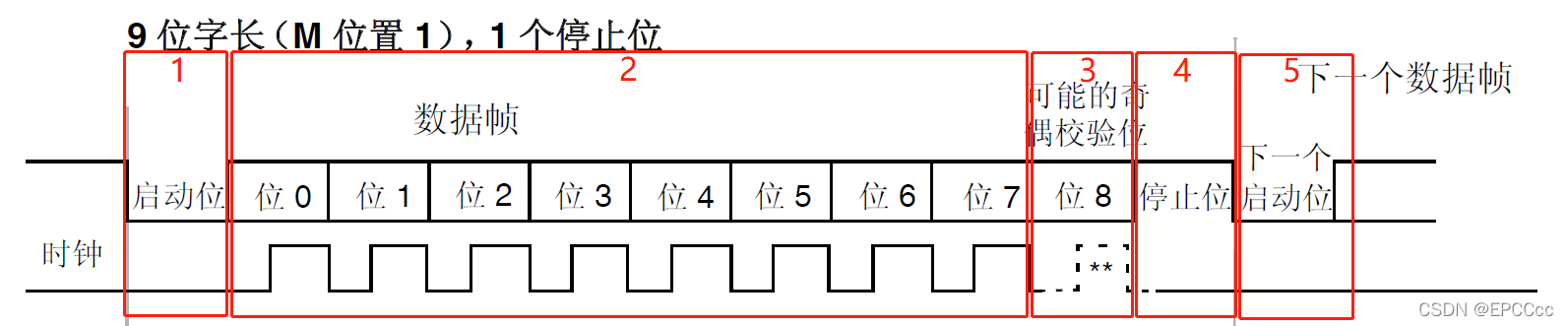

- 起始位:0

- 数据位:可以是6/7/8位数据

- 奇偶校验位(可有可无):奇偶校验就是相对于数据里的1来说,如果是奇校验,有奇数个1就是在奇偶校验位是0,否则奇偶校验位是1,如果是偶校验,有奇数个1就是在奇偶校验位是1,否则奇偶校验位是0,总的来说,奇校验就是看数据位里的加上奇偶校验位(一共9位)是否是奇数,偶校验反之。

- 结束位:1

三、了解波特率

波特率表示每秒钟传送的码元符号的个数,是衡量数据传送速率的指标。

我们常常使用的是RS-232-C,RS-232-C标准规定的数据传输速率为50、75、100、150、300、600、1200、2400、4800、9600、19200、38400波特。

二、串口UART思路设计

其实串口算是一个较简单的协议了,不需要有状态机,只需要有2个计数器就可以搞定,1个是波特率计数器,用来何时收发数据,1个是bit计数,顾名思义记串口的数据bit的,串口分为2个模块,1个是接收模块,1个是发送模块

- 接收模块

在波特率中间稳定的时候去采集数据,第一位为起始位,是0,所以检测到下降沿,给一个标志就可以采集数据位了,最后串并转换。 - 发送模块

从上位机发来的数据,然后最后串并转换的时候在头部加上起始位,在尾部加上结束位即可。

三 、代码部分

这部分我自己写的,如果有问题,请及时通知我。

代码注解比较详细吧。

一、串口接收模块

// 串口接收模块

module uart_rx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input din,// 串口接收模块接收到主机来的1bit的数据

output [7:0] dout,// 串口接收模块串并转换的数据发送

output dout_vld

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 对输入的1bit数据打拍

// 因为开始位是0,,停止位是1

reg din_r0;

reg din_r1;

// 检测到下降沿开始输入接收

wire din_nedge;

// 检测到下降沿的标志

reg din_nedge_flag;

// 寄存串并转换的接收到的数据9位开始位+停止位+数据8位

reg [9:0] rx_data;

reg rx_data_vld;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = din_nedge_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 同步打拍

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_r0 <= 0;

din_r1 <= 0;

end

else begin

din_r0 <= din;

din_r1 <= din_r0;

end

end

// 下降沿检测

assign din_nedge = ~din_r0 & din_r1;

// 下降沿检测标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_nedge_flag <= 0;

end

else if(din_nedge)begin

din_nedge_flag <= 1'b1;

end

else if(end_cnt_bit)begin

din_nedge_flag <= 1'b0;

end

end

// 在波特率中间取稳定的值

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data <= 0;

end

else if(add_cnt_baud && cnt_baud == (baud >> 1) - 1)begin

rx_data[cnt_bit] <= din;

end

end

assign dout = rx_data[8:1];

// 数据有效

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld <= 0;

end

else if(end_cnt_bit)begin

rx_data_vld <= 1;

end

else begin

rx_data_vld <= 1'b0;

end

end

assign dout_vld = rx_data_vld;

endmodule

二、串口发送模块

module uart_tx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input [7:0] din,// 串并转换的数据

input din_vld,// 串并转换的数据有效

output dout,// 发送模块发送的1bit数据

output busy // 发送模块忙标志

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 寄存发送模块接收的数据有效

reg rx_data_vld_flag;

// 寄存要发送的数据

reg [9:0] tx_data;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = rx_data_vld_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 数据有效的标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld_flag <= 0;

end

else if(din_vld)begin

rx_data_vld_flag <= 1'b1;

end

else if(end_cnt_bit)begin

rx_data_vld_flag <= 1'b0;

end

end

// 数据有效添加开始位和停止位

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

tx_data <= 0;

end

else if(din_vld)begin

tx_data <= {1'b1,din,1'b0};

end

end

// 数据有效标志1bit数据发送,之后都发高位,不能发低位

assign dout = rx_data_vld_flag?tx_data[cnt_bit]:1'b1;

// 这个busy有待商榷

assign busy = rx_data_vld_flag;

endmodule

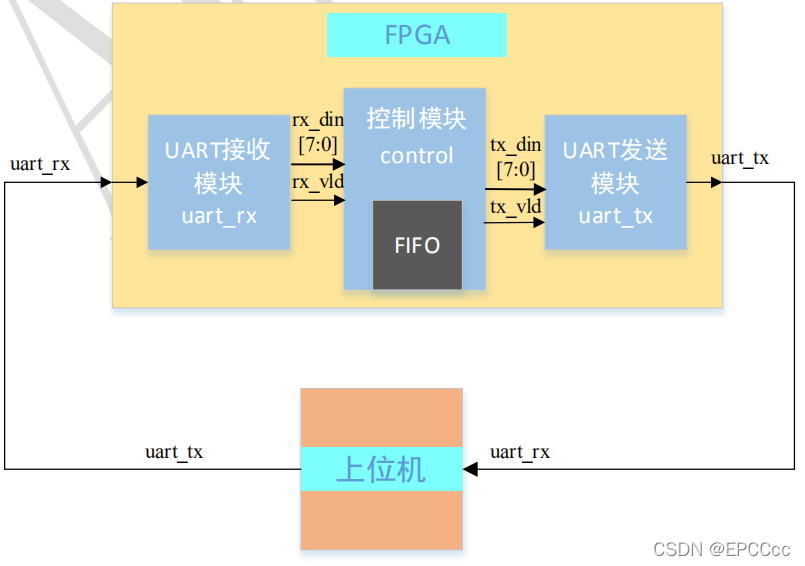

四、串口回环实验

任务要求

FPGA 与上位机通过串口通信,完成数据环回;

波特率可调,即可以选择 115200、57600、38400 等;

使用 FIFO 作为数据缓存单元

系统框图

难的不是串口接收发送模块,难的是串口控制的fifo,对于fifo的使用我还不太熟悉,fifo的读写请求和数据要一致,还有fifo的前显模式和正常模式。

串口控制模块

// 串口控制模块

module uart_ctrl(

input clk,

input rst_n,

input [7:0] din,// 接收模块8位数据

input din_vld,// 接收模块8位数据的

input busy,

output [7:0] dout,

output dout_vld

);

wire rdreq;

wire wrreq;

wire empty;

wire full ;

wire [7:0] q_out;

wire [4:0] usedw;

// 用fifo缓存数据,来控制读写

fifo fifo_inst (

.aclr ( ~rst_n ),

.clock ( clk ),

.data ( din ),

.rdreq ( rdreq ),

.wrreq ( wrreq ),

.empty ( empty ),

.full ( full ),

.q ( q_out ),

.usedw ( usedw )

);

// 写使能,写进fifo

assign wrreq = ~full && din_vld;

// 读使能,从fifo读出来

assign rdreq = ~empty && ~busy && (usedw == 2);

assign dout = q_out;

assign dout_vld = rdreq;

endmodule

顶层

module top(

input clk,

input rst_n,

input uart_rx,

output uart_tx

);

wire [7:0] rx_data;

wire rx_data_vld;

wire busy;

wire [7:0] tx_data;

wire tx_data_vld;

// 串口接收模块

uart_rx u_uart_rx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input */.din (uart_rx ),// 串口接收模块接收到主机来的1bit的数据

/* output [7:0] */.dout (rx_data ),// 串口接收模块串并转换的数据发送

/* output */.dout_vld (rx_data_vld)

);

// 串口控制模块

uart_ctrl u_uart_ctrl(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input [7:0] */.din (rx_data ),// 接收模块8位数据

/* input */.din_vld (rx_data_vld ),// 接收模块8位数据的

/* input */.busy (busy ),

/* output [7:0] */.dout (tx_data ),

/* output */.dout_vld (tx_data_vld)

);

// 串口发送模块

uart_tx u_uart_tx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input [7:0] */.din (tx_data ),// 串并转换的数据

/* input */.din_vld (tx_data_vld ),// 串并转换的数据有效

/* output */.dout (uart_tx ),// 发送模块发送的1bit数据

/* output */.busy (busy ) // 发送模块忙标志

);

endmodule

串口接收发送模块同上

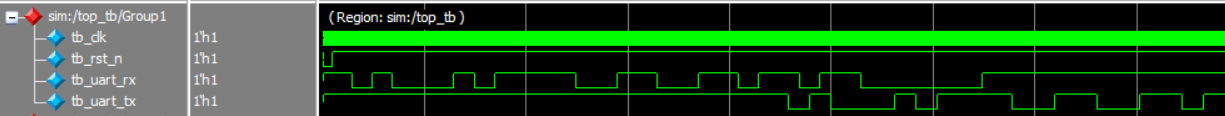

五、仿真验证

fifo就是队列,先进先出,我这里设了数据量深度为2个数据出现数据

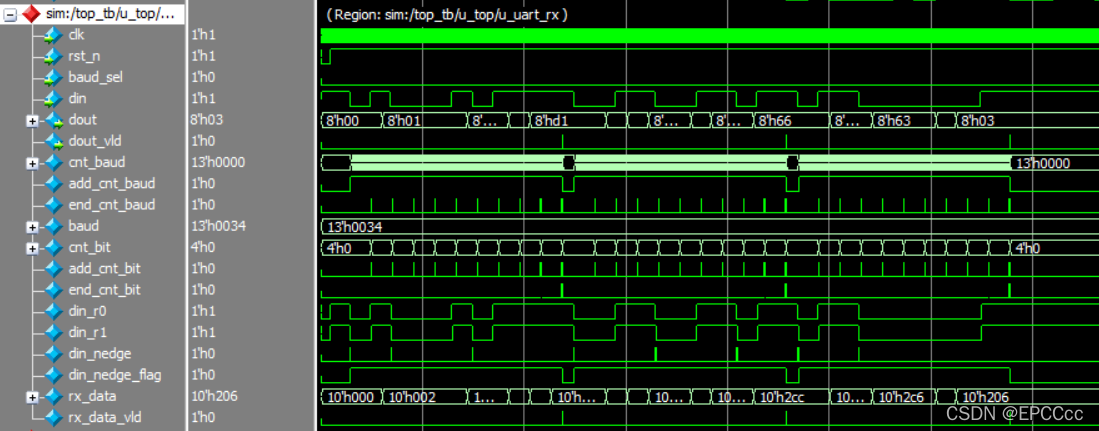

顶层仿真

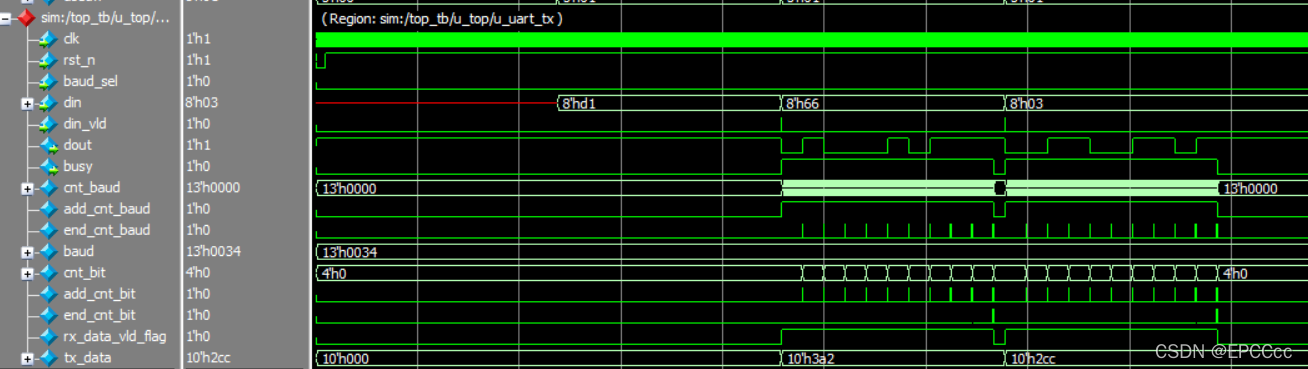

串口发送模块仿真

串口发送模块仿真

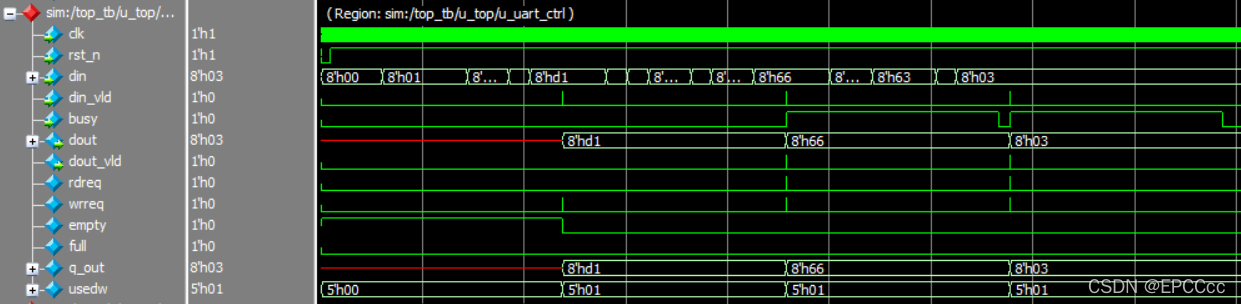

串口控制模块仿真

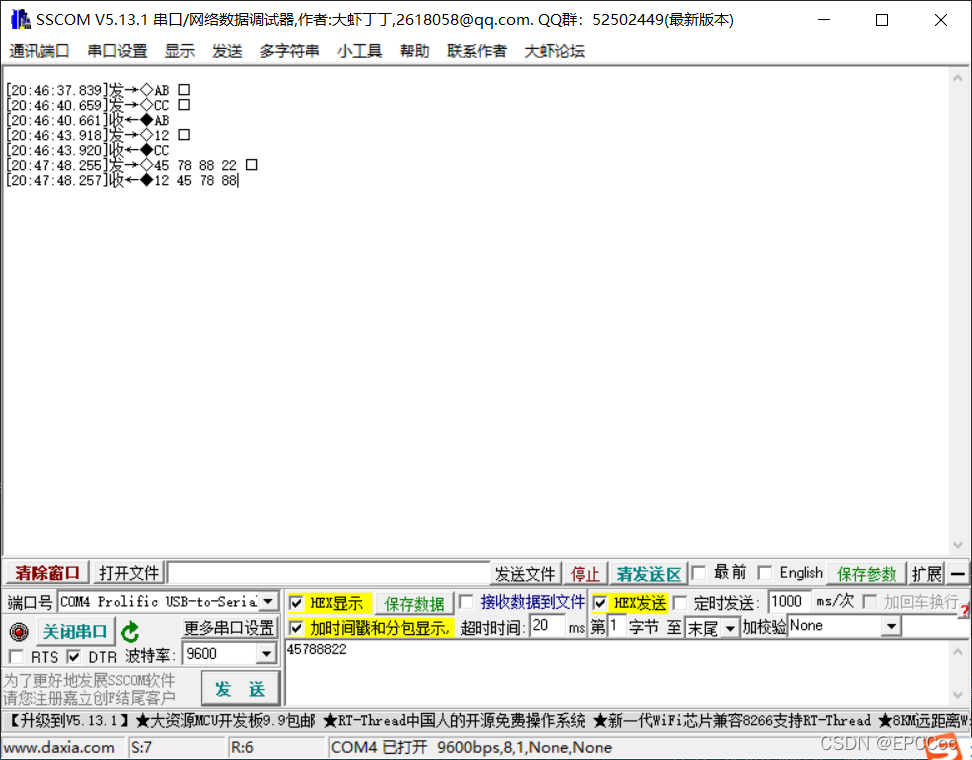

六、上板验证

七、总结

串口通信算是最最最基础的通信协议了,虽然我也当时写不出来,但是后来仔细研究,串口不难,难的是fifo。

以后再写一篇关于fifo的使用。

智能推荐

Docker 快速上手学习入门教程_docker菜鸟教程-程序员宅基地

文章浏览阅读2.5w次,点赞6次,收藏50次。官方解释是,docker 容器是机器上的沙盒进程,它与主机上的所有其他进程隔离。所以容器只是操作系统中被隔离开来的一个进程,所谓的容器化,其实也只是对操作系统进行欺骗的一种语法糖。_docker菜鸟教程

电脑技巧:Windows系统原版纯净软件必备的两个网站_msdn我告诉你-程序员宅基地

文章浏览阅读5.7k次,点赞3次,收藏14次。该如何避免的,今天小编给大家推荐两个下载Windows系统官方软件的资源网站,可以杜绝软件捆绑等行为。该站提供了丰富的Windows官方技术资源,比较重要的有MSDN技术资源文档库、官方工具和资源、应用程序、开发人员工具(Visual Studio 、SQLServer等等)、系统镜像、设计人员工具等。总的来说,这两个都是非常优秀的Windows系统镜像资源站,提供了丰富的Windows系统镜像资源,并且保证了资源的纯净和安全性,有需要的朋友可以去了解一下。这个非常实用的资源网站的创建者是国内的一个网友。_msdn我告诉你

vue2封装对话框el-dialog组件_<el-dialog 封装成组件 vue2-程序员宅基地

文章浏览阅读1.2k次。vue2封装对话框el-dialog组件_

MFC 文本框换行_c++ mfc同一框内输入二行怎么换行-程序员宅基地

文章浏览阅读4.7k次,点赞5次,收藏6次。MFC 文本框换行 标签: it mfc 文本框1.将Multiline属性设置为True2.换行是使用"\r\n" (宽字符串为L"\r\n")3.如果需要编辑并且按Enter键换行,还要将 Want Return 设置为 True4.如果需要垂直滚动条的话将Vertical Scroll属性设置为True,需要水平滚动条的话将Horizontal Scroll属性设_c++ mfc同一框内输入二行怎么换行

redis-desktop-manager无法连接redis-server的解决方法_redis-server doesn't support auth command or ismis-程序员宅基地

文章浏览阅读832次。检查Linux是否是否开启所需端口,默认为6379,若未打开,将其开启:以root用户执行iptables -I INPUT -p tcp --dport 6379 -j ACCEPT如果还是未能解决,修改redis.conf,修改主机地址:bind 192.168.85.**;然后使用该配置文件,重新启动Redis服务./redis-server redis.conf..._redis-server doesn't support auth command or ismisconfigured. try

实验四 数据选择器及其应用-程序员宅基地

文章浏览阅读4.9k次。济大数电实验报告_数据选择器及其应用

随便推点

灰色预测模型matlab_MATLAB实战|基于灰色预测河南省社会消费品零售总额预测-程序员宅基地

文章浏览阅读236次。1研究内容消费在生产中占据十分重要的地位,是生产的最终目的和动力,是保持省内经济稳定快速发展的核心要素。预测河南省社会消费品零售总额,是进行宏观经济调控和消费体制改变创新的基础,是河南省内人民对美好的全面和谐社会的追求的要求,保持河南省经济稳定和可持续发展具有重要意义。本文建立灰色预测模型,利用MATLAB软件,预测出2019年~2023年河南省社会消费品零售总额预测值分别为21881...._灰色预测模型用什么软件

log4qt-程序员宅基地

文章浏览阅读1.2k次。12.4-在Qt中使用Log4Qt输出Log文件,看这一篇就足够了一、为啥要使用第三方Log库,而不用平台自带的Log库二、Log4j系列库的功能介绍与基本概念三、Log4Qt库的基本介绍四、将Log4qt组装成为一个单独模块五、使用配置文件的方式配置Log4Qt六、使用代码的方式配置Log4Qt七、在Qt工程中引入Log4Qt库模块的方法八、获取示例中的源代码一、为啥要使用第三方Log库,而不用平台自带的Log库首先要说明的是,在平时开发和调试中开发平台自带的“打印输出”已经足够了。但_log4qt

100种思维模型之全局观思维模型-67_计算机中对于全局观的-程序员宅基地

文章浏览阅读786次。全局观思维模型,一个教我们由点到线,由线到面,再由面到体,不断的放大格局去思考问题的思维模型。_计算机中对于全局观的

线程间控制之CountDownLatch和CyclicBarrier使用介绍_countdownluach于cyclicbarrier的用法-程序员宅基地

文章浏览阅读330次。一、CountDownLatch介绍CountDownLatch采用减法计算;是一个同步辅助工具类和CyclicBarrier类功能类似,允许一个或多个线程等待,直到在其他线程中执行的一组操作完成。二、CountDownLatch俩种应用场景: 场景一:所有线程在等待开始信号(startSignal.await()),主流程发出开始信号通知,既执行startSignal.countDown()方法后;所有线程才开始执行;每个线程执行完发出做完信号,既执行do..._countdownluach于cyclicbarrier的用法

自动化监控系统Prometheus&Grafana_-自动化监控系统prometheus&grafana实战-程序员宅基地

文章浏览阅读508次。Prometheus 算是一个全能型选手,原生支持容器监控,当然监控传统应用也不是吃干饭的,所以就是容器和非容器他都支持,所有的监控系统都具备这个流程,_-自动化监控系统prometheus&grafana实战

React 组件封装之 Search 搜索_react search-程序员宅基地

文章浏览阅读4.7k次。输入关键字,可以通过键盘的搜索按钮完成搜索功能。_react search