Openpiton RISC-V处理器学习笔记(3 移植至ZCU102 FPGA并仿真)_xilinx zcu102-程序员宅基地

技术标签: fpga开发 risc-v Powered by 金山文档 linux

注:无需移植跳转至生成比特流步骤即可。

一、IP移植

工程所用IP不涉及PS端arm内核,均在PL端,皆可移植至ZCU102。在vivado新建工程中设置好导出xci文件拷贝至对应文件夹(新增zcu102文件夹)即可,脚本运行时会自动添加对应ip

所使用PL端IP为:

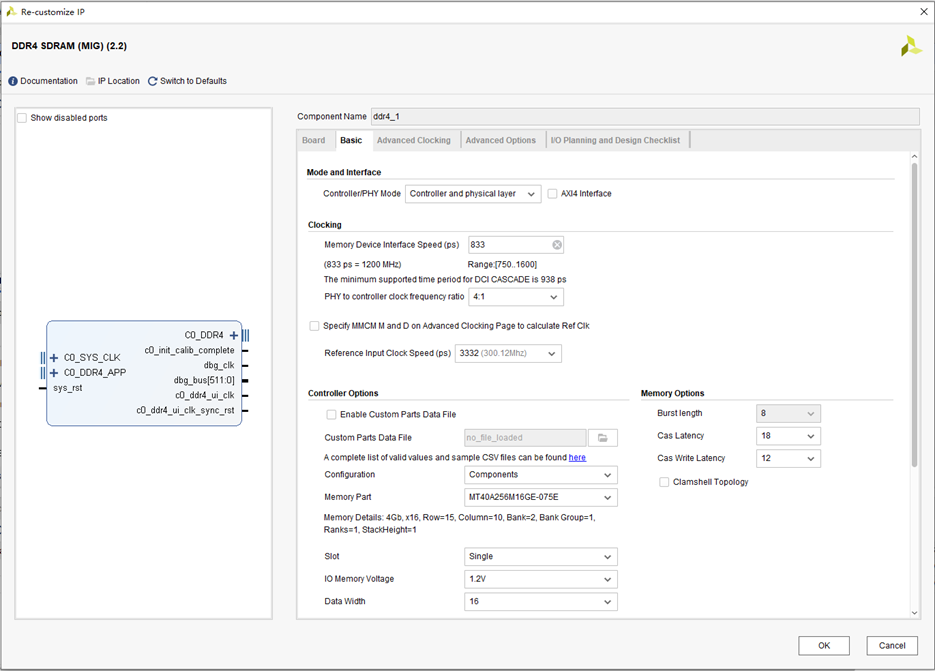

DDR4控制器(拷贝位置piton/design/chipset/mc/xilinx/zcu102/ip_cores/ddr4_0)

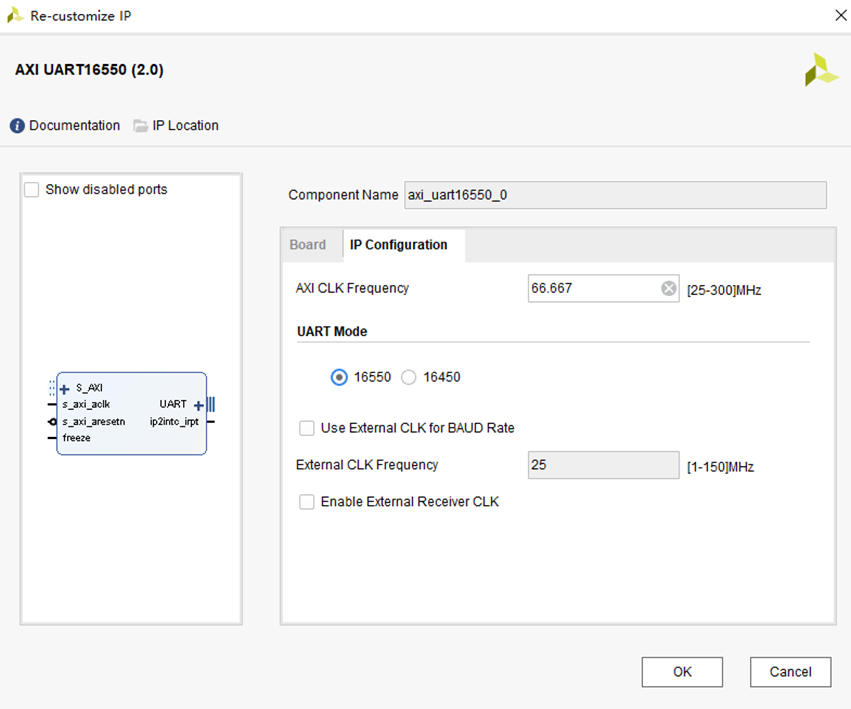

UART16550串口(拷贝位置/piton/design/chipset/io_ctrl/xilinx/zcu102/ip_cores/uart_16550

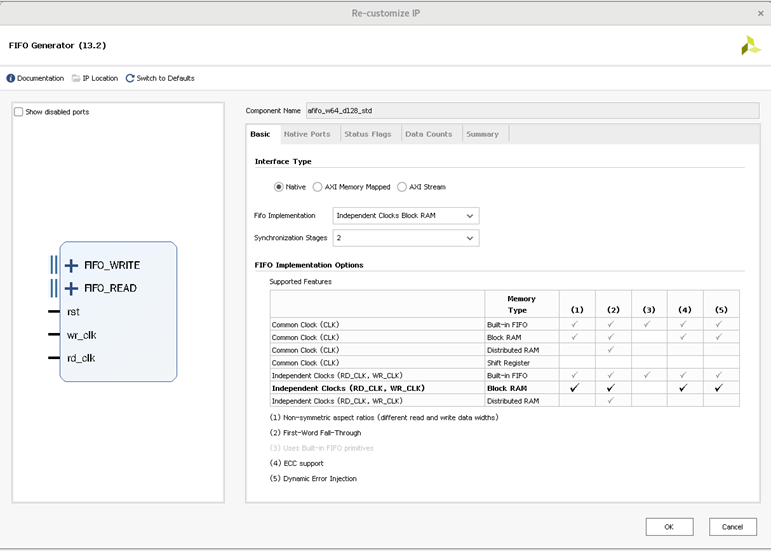

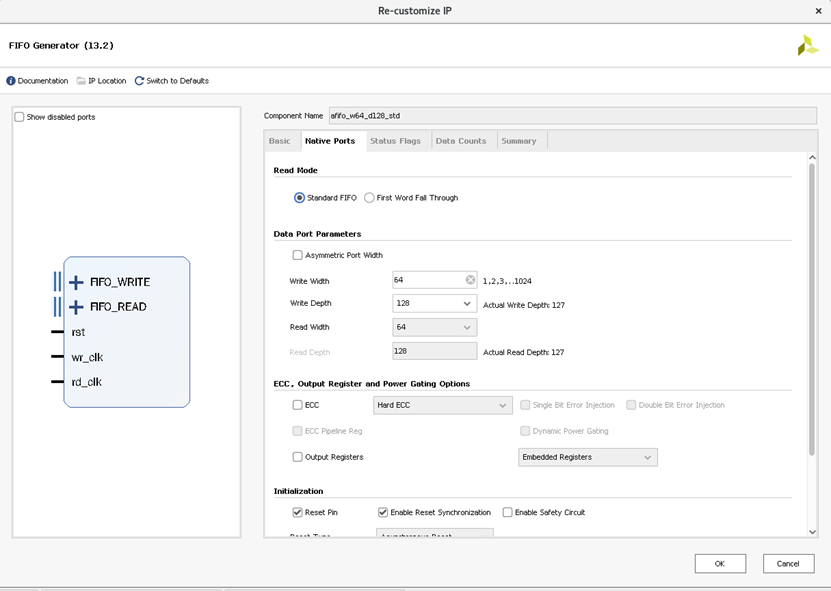

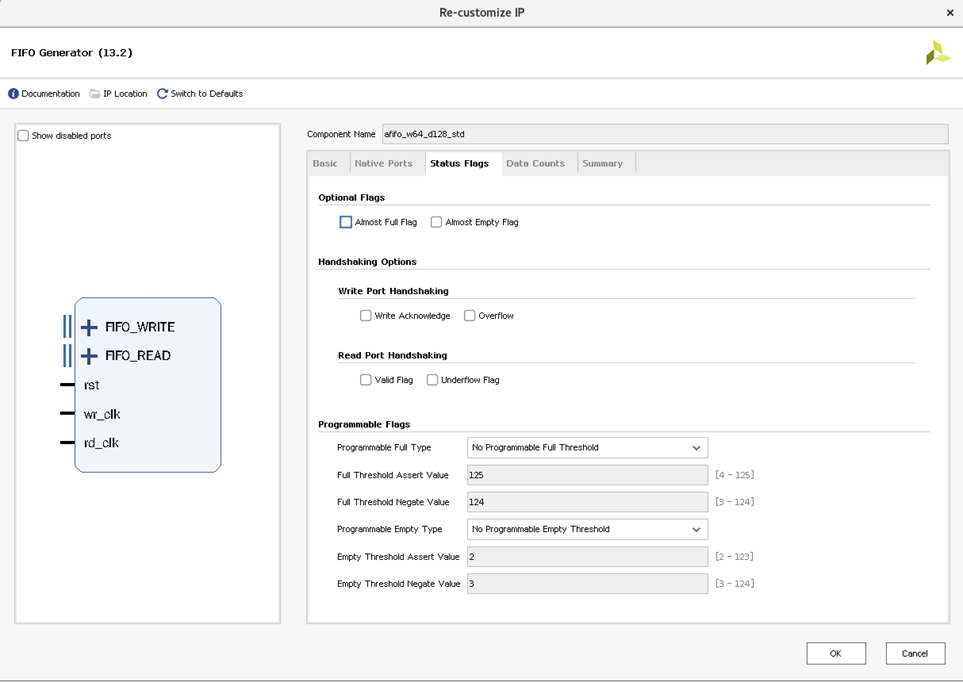

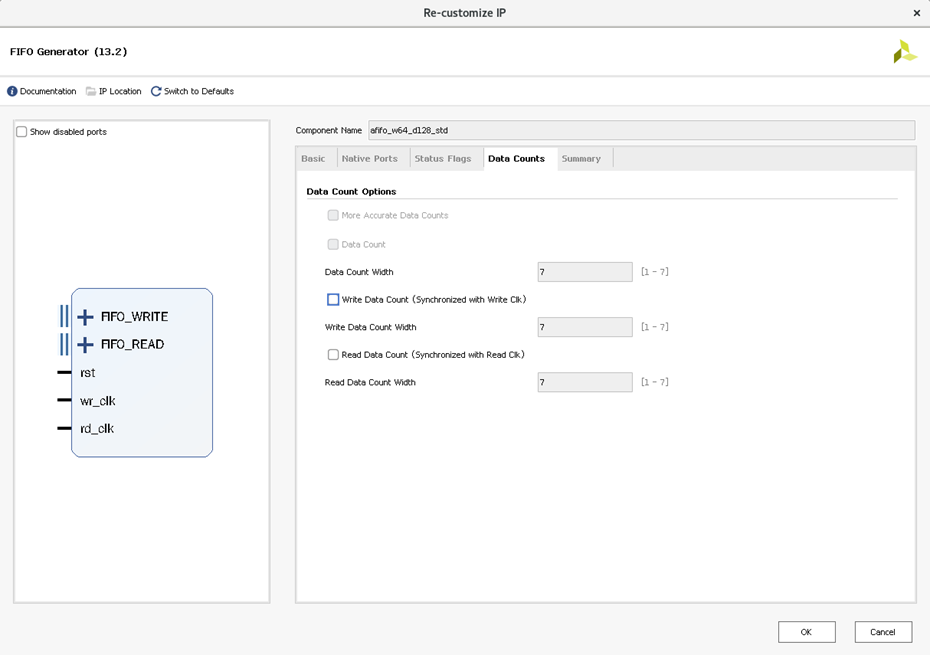

afifo_w64_d128(拷贝位置piton/design/chipset/Xilinx/zcu102/ip_cores/afifo_w64_d128_std)

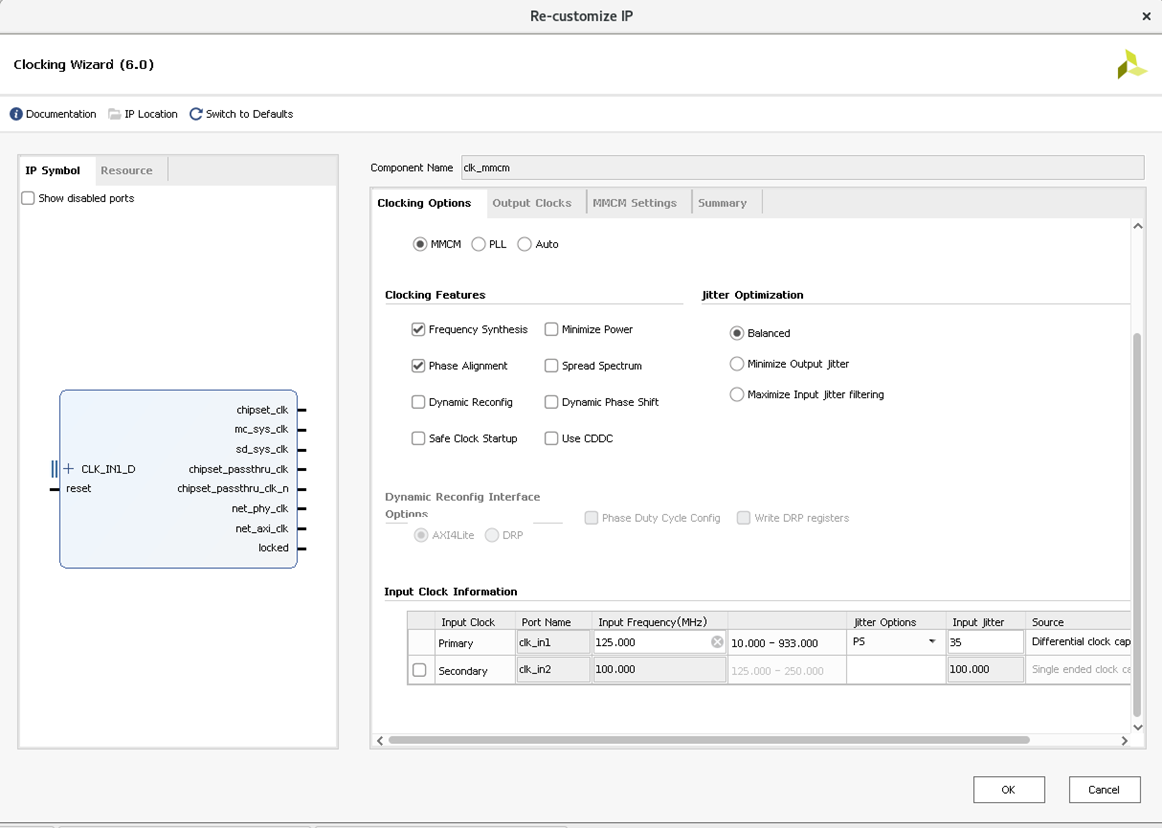

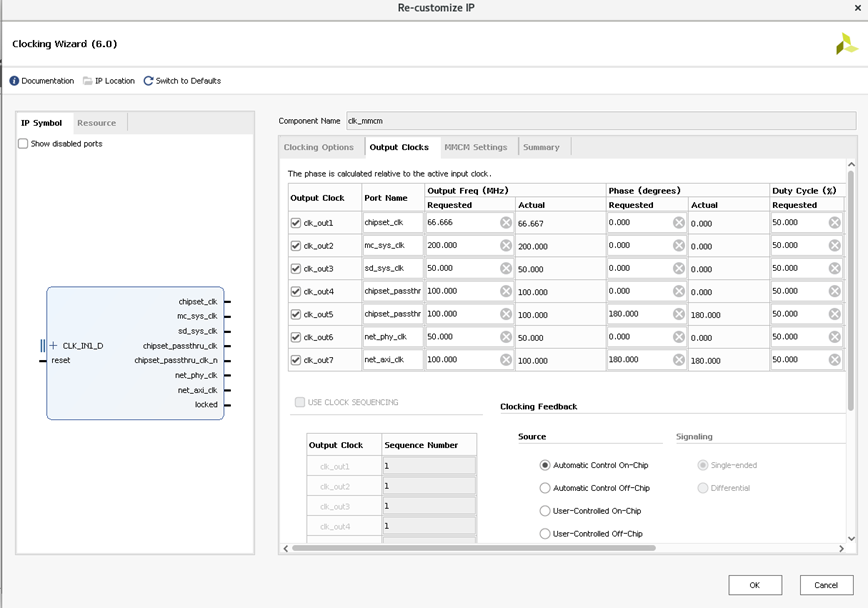

clk_mmcm时钟分频(拷贝位置/piton/design/chipset/xilinx/zcu102/ip_cores/clk_mmcm)

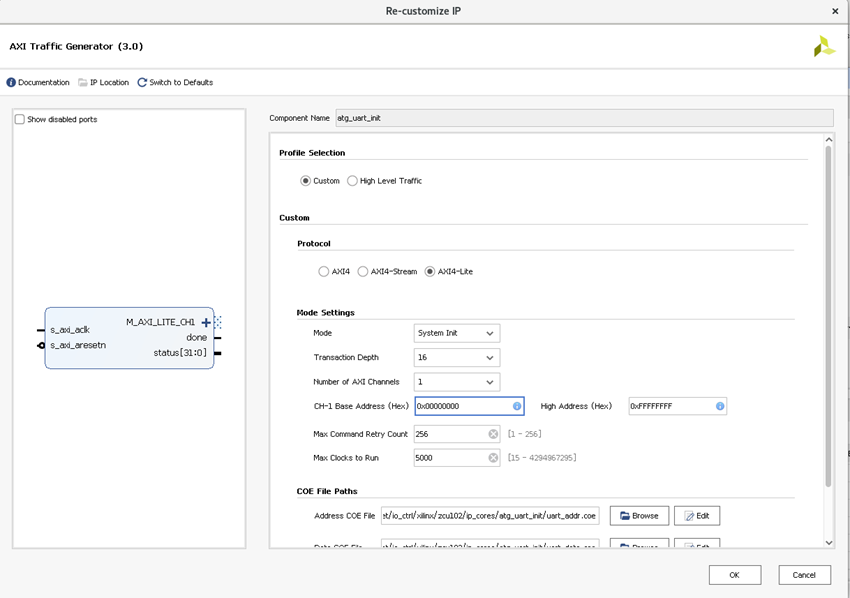

atg_uart_init串口初始化(拷贝位置piton/design/chipset/io_ctrl/xilinx/zcu102/ip_cores/atg_uart_init)

二、板卡特性宏定义修改

ZCU102不提供PL端SD卡访问,在宏定义和约束中去掉;ZCU102 PL端DDR支持数据宽度为16位,需要修改DDR4 IP和对应约束,Genesys2开发板使用的是DDR3,ZCU102需要在piton/design/include/piton_system.h文件中修改DDR相关宏定义配置。

由于ZCU102复位是高有效,需要在piton_system.vh中设置对应宏变量[`definePITON_FPGA_RST_ACT_HIGH]

自117行开始修改如下

`ifdef VC707_BOARD

`define PITON_CHIPSET_DIFF_CLK

`elsif VCU118_BOARD

`define PITON_CHIPSET_DIFF_CLK

`elsif XUPP3R_BOARD

`define PITON_CHIPSET_DIFF_CLK

`elsif GENESYS2_BOARD

`define PITON_CHIPSET_DIFF_CLK

`elsif ZCU102_BOARD

`define PITON_CHIPSET_DIFF_CLK

`elsif PITON_BOARD

`define PITON_CHIPSET_DIFF_CLK

`define PITON_CHIPSET_DIFF_CLK_POLARITY_CAPS

`define PITON_FPGA_AFIFO_NO_SRST

`endif

// Nexys4ddr and NexysVideo has single ended clock input

// Reset is active high on VC707 and VCU118 and ZCU102

`ifdef VC707_BOARD

`define PITON_FPGA_RST_ACT_HIGH

`elsif VCU118_BOARD

`define PITON_FPGA_RST_ACT_HIGH

`elsif ZCU102_BOARD

`define PITON_FPGA_RST_ACT_HIGH

`endif

`ifdef XUPP3R_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`elsif ZCU102_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`elsif F1_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`define PITONSYS_AXI4_MEM

`endif

`ifdef XUPP3R_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`elsif ZCU102_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`elsif F1_BOARD

`undef PITON_FPGA_SD_BOOT

`undef PITONSYS_SPI

`define PITONSYS_AXI4_MEM

`endif

// If PITON_FPGA_SD_BOOT is set we should always include SPI

`ifdef PITON_FPGA_SD_BOOT

`define PITONSYS_SPI

`endif // endif PITON_FPGA_SD_BOOT

// If PITONSYS_UART_BOOT is set, we should always include a UART

`ifdef PITONSYS_UART_BOOT

`define PITONSYS_UART

`endif // endif PITONSYS_UART_BOOT

`ifdef VCU118_BOARD

`define PITONSYS_DDR4

`elsif XUPP3R_BOARD

`define PITONSYS_DDR4

`elsif ZCU102_BOARD

`define PITONSYS_DDR4

`endif三、内存信息宏定义修改

新增ZCU102开发板型号,宏定义中新增对应配置信息。

注:ZCU102拥有两块DDR,提供给PS端的为64位,提供给PL端的为16位。

Piton/design/chipset/include/mc_define.h

ZCU102_BOARD

`define BOARD_MEM_SIZE_MB 512

`define WORDS_PER_BURST 8

`define WORD_SIZE 8 // in bytes134,217,728

`define MIG_APP_ADDR_WIDTH 28

`define MIG_APP_CMD_WIDTH 3

`define MIG_APP_DATA_WIDTH 128

`define MIG_APP_MASK_WIDTH 16

`define DDR3_DQ_WIDTH 16

`define DDR3_DQS_WIDTH 2

`define DDR3_ADDR_WIDTH 17

`define DDR3_BA_WIDTH 2

`define DDR3_DM_WIDTH 2

`define DDR3_CK_WIDTH 1

`define DDR3_CKE_WIDTH 1

`define DDR3_CS_WIDTH 1

`define DDR3_ODT_WIDTH 1

四、嵌入式程序修改

(位于文件夹piton/verif/diag/c/riscv/ariane内),工程例程基于Genesys2开发板设计,程序为32位,涉及内存写入的程序需要修改至ZCU102内存支持的64位(非必要,但软硬件要对应,硬件32位软件也要32位)。

五、外设列表修改

新增piton/design/xilinx/zcu102/devices_ariane.xml和devices.xml文件(该文件为处理器访存的地址信息,可复制同文件夹的其他开发板的文件进行修改)

将新增外设添加至列表中时,特别是<stream_accessible/>,缺少这一行可仿真,但上板时无法在ZCU102上访问该外设!

修改内存信息

<port>

<name>mem</name>

<base>0x80000000</base>

<!-- 512MB -->

<length>0x20000000</length>

</port>六、修改文件列表

新增Veriloig或System Verilog文件时,修改piton/tools/src/proto/common/rtl_setup.tcl和piton/design/chip/tile/ariane/Flist.ariane两个文件即可,仿真和上板都需要修改。

七、运行脚本修改

运行综合的脚本为piton/tools/src/proto/protosyn,2.5

运行嵌入式程序的脚本为piton/tools/src/proto/pitonstream,1.0

由于综合脚本和嵌入式程序脚本版本不同,且使用同一个文件piton/tools/src/proto/dbg.py,内置的print函数形式需要手动切换。【综合时用print(msg_print, file=fstream),烧程序时用print>> fstream, msg_print】

def print_debug(msg, fstream=sys.stderr):

if DEBUG:

msg_print = clr.CYAN + "[DEBUG] " + getFuncLine() + clr.RST_CLR + ": " + msg

# print(msg_print, file=fstream)

print >> fstream, msg_printz

else:

pass

def print_info(msg, fstream=sys.stderr):

msg_print = clr.BLUE + "[INFO] " + getFuncLine() + clr.RST_CLR + ": " + msg

# print(msg_print, file=fstream)

print >> fstream, msg_print

def print_warning(msg, fstream=sys.stderr):

msg_print = clr.YELLOW + "[WARN] " + getFuncLine() + clr.RST_CLR + ": " + msg

# print(msg_print, file=fstream)

print >> fstream, msg_print

def print_error(msg, fstream=sys.stderr):

msg_print = clr.RED + "[ERROR] " + getFuncLine() + clr.RST_CLR + ": " + msg

# print(msg_print, file=fstream)

print >> fstream, msg_print在这两个文件新增ZCU102,此外在protosyn,2.5中指定ZCU102不使用SD卡模块,不定义PITON_FPGA_SD_BOOT宏定义

# do not use SD controller if BRAM is used for boot or a test or if board doesn't have sd

if (options.test_name != None) or (options.board in {"piton_board", 'xupp3r', "f1","zcu102"}):

pass

else: # default option

defines.append("PITON_FPGA_SD_BOOT")此外,由于新版vivado自带Python环境,需要在脚本中移除Python环境的相关设置。

参考https://github.com/PrincetonUniversity/openpiton/issues/50

在文件piton/tools/src/proto/common/setup.tcl第131和132行之间添加以下设置

unset ::env(PYTHONPATH)

unset ::env(PYTHONHOME)八、板卡信息修改

在piton/tools/src/proto新增zcu102文件夹,新建board.tcl文件,内含ZCU102配置信息

set BOARD_PART ""

set FPGA_PART"xczu9eg-ffvb1156-2-e"

set VIVADO_FLOW_PERF_OPT 0

set BOARD_DEFAULT_VERILOG_MACROS"ZCU102_BOARD"

九、约束文件修改

位置:piton/design/xilinx/zcu102/constraints.xdc

#系统时钟

set_property IOSTANDARD LVDS_25 [get_ports chipset_clk_osc_n]

set_property PACKAGE_PIN G21 [get_ports chipset_clk_osc_p]

set_property PACKAGE_PIN F21 [get_ports chipset_clk_osc_n]

set_property IOSTANDARD LVDS_25 [get_ports chipset_clk_osc_p]

#内存时钟

set_property IOSTANDARD DIFF_SSTL12 [get_ports mc_clk_n]

set_property PACKAGE_PIN AL8 [get_ports mc_clk_p]

set_property PACKAGE_PIN AL7 [get_ports mc_clk_n]

set_property IOSTANDARD DIFF_SSTL12 [get_ports mc_clk_p]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets chipset/clk_mmcm/inst/clkin1_ibufds/O]

#笔者未进行JTAG调试,不确定tck、td_i、td_o、tms、trst是否正常工作,若需要使用可自行绑定特定IO口

#JTAG时钟

create_clock -period 100.000 -name tck_i -waveform {0.000 50.000} [get_ports tck_i]

#系统复位

set_property PACKAGE_PIN AM13 [get_ports sys_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

#串口

set_property PACKAGE_PIN E13 [get_ports uart_rx]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rx]

set_property PACKAGE_PIN F13 [get_ports uart_tx]

set_property IOSTANDARD LVCMOS33 [get_ports uart_tx]

set_property PACKAGE_PIN D12 [get_ports uart_cts]

set_property IOSTANDARD LVCMOS33 [get_ports uart_cts]

set_property PACKAGE_PIN E12 [get_ports uart_rts]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rts]

#JTAG接口

set_property PACKAGE_PIN D20 [get_ports tck_i]

set_property IOSTANDARD LVCMOS33 [get_ports tck_i]

set_property PACKAGE_PIN E20 [get_ports td_i]

set_property IOSTANDARD LVCMOS33 [get_ports td_i]

set_property PACKAGE_PIN D22 [get_ports td_o]

set_property IOSTANDARD LVCMOS33 [get_ports td_o]

set_property PACKAGE_PIN E22 [get_ports tms_i]

set_property IOSTANDARD LVCMOS33 [get_ports tms_i]

set_property PACKAGE_PIN F20 [get_ports trst_ni]

set_property IOSTANDARD LVCMOS33 [get_ports trst_ni]

## Add some additional constraints for JTAG signals, set to 10MHz to be on the safe side

set_input_delay -clock tck_i -clock_fall 5.000 [get_ports td_i]

set_input_delay -clock tck_i -clock_fall 5.000 [get_ports tms_i]

set_output_delay -clock tck_i 5.000 [get_ports td_o]

set_false_path -from [get_ports trst_ni]

# accept sub-optimal placement

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets tck_i_IBUF_inst/O]

# constrain clock domain crossing

set_max_delay -datapath_only -from [get_clocks -include_generated_clocks chipset_clk_clk_mmcm] -to [get_clocks tck_i] 15.000

set_max_delay -datapath_only -from [get_clocks tck_i] -to [get_clocks -include_generated_clocks chipset_clk_clk_mmcm] 15.000

#LED和Switch

set_property PACKAGE_PIN AG14 [get_ports {leds[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[0]}]

set_property PACKAGE_PIN AF13 [get_ports {leds[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[1]}]

set_property PACKAGE_PIN AE13 [get_ports {leds[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[2]}]

set_property PACKAGE_PIN AJ14 [get_ports {leds[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[3]}]

set_property PACKAGE_PIN AJ15 [get_ports {leds[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[4]}]

set_property PACKAGE_PIN AH13 [get_ports {leds[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[5]}]

set_property PACKAGE_PIN AH14 [get_ports {leds[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[6]}]

set_property PACKAGE_PIN AL12 [get_ports {leds[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {leds[7]}]

set_property PACKAGE_PIN AK13 [get_ports {sw[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

set_property PACKAGE_PIN AL13 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property PACKAGE_PIN AP12 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property PACKAGE_PIN AN12 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property PACKAGE_PIN AN13 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property PACKAGE_PIN AM14 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property PACKAGE_PIN AP14 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property PACKAGE_PIN AN14 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

# False paths

set_false_path -to [get_cells -hierarchical *afifo_ui_rst_r*]

set_false_path -to [get_cells -hierarchical *ui_clk_sync_rst_r*]

set_false_path -to [get_cells -hierarchical *ui_clk_syn_rst_delayed*]

set_false_path -to [get_cells -hierarchical *init_calib_complete_f*]

set_false_path -to [get_cells -hierarchical *chipset_rst_n*]

#DDR

set_property PACKAGE_PIN AH9 [get_ports ddr_reset_n]

set_property IOSTANDARD LVCMOS18 [get_ports ddr_reset_n]

set_property PACKAGE_PIN AK2 [get_ports {ddr_dq[8]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[8]}]

set_property PACKAGE_PIN AK3 [get_ports {ddr_dq[9]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[9]}]

set_property PACKAGE_PIN AL1 [get_ports {ddr_dq[10]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[10]}]

set_property PACKAGE_PIN AK1 [get_ports {ddr_dq[11]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[11]}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {ddr_dqs_n[1]}]

set_property PACKAGE_PIN AL3 [get_ports {ddr_dqs_p[1]}]

set_property PACKAGE_PIN AL2 [get_ports {ddr_dqs_n[1]}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {ddr_dqs_p[1]}]

set_property PACKAGE_PIN AN1 [get_ports {ddr_dq[12]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[12]}]

set_property PACKAGE_PIN AM1 [get_ports {ddr_dq[13]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[13]}]

set_property PACKAGE_PIN AP3 [get_ports {ddr_dq[14]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[14]}]

set_property PACKAGE_PIN AN3 [get_ports {ddr_dq[15]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[15]}]

set_property PACKAGE_PIN AP2 [get_ports {ddr_cs_n[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_cs_n[0]}]

set_property PACKAGE_PIN AN2 [get_ports {ddr_dm[1]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dm[1]}]

# set_property PACKAGE_PIN AP1 [get_ports "DDR4_PAR"] ;# Bank 64 VCCO - VCC1V2 - IO_T3U_N12_64

# set_property IOSTANDARD SSTL12_DCI [get_ports "DDR4_PAR"] ;# Bank 64 VCCO - VCC1V2 - IO_T3U_N12_64

set_property PACKAGE_PIN AM3 [get_ports {ddr_cke[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_cke[0]}]

set_property PACKAGE_PIN AK4 [get_ports {ddr_dq[0]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[0]}]

set_property PACKAGE_PIN AK5 [get_ports {ddr_dq[1]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[1]}]

set_property PACKAGE_PIN AN4 [get_ports {ddr_dq[2]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[2]}]

set_property PACKAGE_PIN AM4 [get_ports {ddr_dq[3]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[3]}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {ddr_dqs_n[0]}]

set_property PACKAGE_PIN AN6 [get_ports {ddr_dqs_p[0]}]

set_property PACKAGE_PIN AP6 [get_ports {ddr_dqs_n[0]}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {ddr_dqs_p[0]}]

set_property PACKAGE_PIN AP4 [get_ports {ddr_dq[4]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[4]}]

set_property PACKAGE_PIN AP5 [get_ports {ddr_dq[5]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[5]}]

set_property PACKAGE_PIN AM5 [get_ports {ddr_dq[6]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[6]}]

set_property PACKAGE_PIN AM6 [get_ports {ddr_dq[7]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dq[7]}]

set_property PACKAGE_PIN AL5 [get_ports {ddr_addr[15]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[15]}]

set_property PACKAGE_PIN AL6 [get_ports {ddr_dm[0]}]

set_property IOSTANDARD POD12_DCI [get_ports {ddr_dm[0]}]

set_property PACKAGE_PIN AK7 [get_ports {ddr_bg[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_bg[0]}]

set_property PACKAGE_PIN AK8 [get_ports ddr_act_n]

set_property IOSTANDARD SSTL12_DCI [get_ports ddr_act_n]

set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ddr_ck_n[0]}]

set_property PACKAGE_PIN AN7 [get_ports {ddr_ck_p[0]}]

set_property PACKAGE_PIN AP7 [get_ports {ddr_ck_n[0]}]

set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ddr_ck_p[0]}]

set_property PACKAGE_PIN AK9 [get_ports {ddr_odt[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_odt[0]}]

set_property PACKAGE_PIN AJ9 [get_ports {ddr_addr[16]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[16]}]

set_property PACKAGE_PIN AM8 [get_ports {ddr_addr[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[0]}]

set_property PACKAGE_PIN AM9 [get_ports {ddr_addr[1]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[1]}]

set_property PACKAGE_PIN AP8 [get_ports {ddr_addr[2]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[2]}]

set_property PACKAGE_PIN AN8 [get_ports {ddr_addr[3]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[3]}]

set_property PACKAGE_PIN AJ7 [get_ports {ddr_addr[14]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[14]}]

# set_property PACKAGE_PIN AN11 [get_ports "VRP_64"] ;# Bank 64 VCCO - VCC1V2 - IO_T0U_N12_VRP_64

#set_property IOSTANDARD [get_ports "VRP_64"] ;# Bank 64 VCCO - VCC1V2 - IO_T0U_N12_VRP_64

set_property PACKAGE_PIN AK10 [get_ports {ddr_addr[4]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[4]}]

set_property PACKAGE_PIN AJ10 [get_ports {ddr_addr[5]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[5]}]

set_property PACKAGE_PIN AP9 [get_ports {ddr_addr[6]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[6]}]

set_property PACKAGE_PIN AN9 [get_ports {ddr_addr[7]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[7]}]

set_property PACKAGE_PIN AP10 [get_ports {ddr_addr[8]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[8]}]

set_property PACKAGE_PIN AP11 [get_ports {ddr_addr[9]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[9]}]

set_property PACKAGE_PIN AM10 [get_ports {ddr_addr[10]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[10]}]

set_property PACKAGE_PIN AL10 [get_ports {ddr_addr[11]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[11]}]

set_property PACKAGE_PIN AM11 [get_ports {ddr_addr[12]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[12]}]

set_property PACKAGE_PIN AL11 [get_ports {ddr_addr[13]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_addr[13]}]

set_property PACKAGE_PIN AK12 [get_ports {ddr_ba[0]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_ba[0]}]

set_property PACKAGE_PIN AJ12 [get_ports {ddr_ba[1]}]

set_property IOSTANDARD SSTL12_DCI [get_ports {ddr_ba[1]}]十、生成比特流

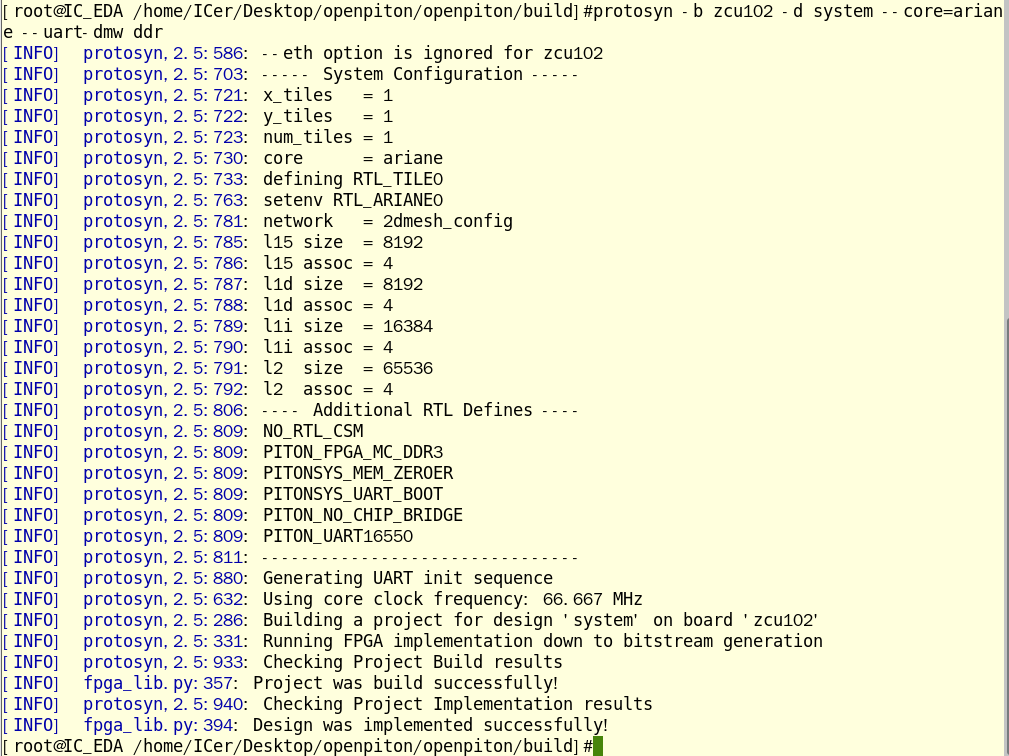

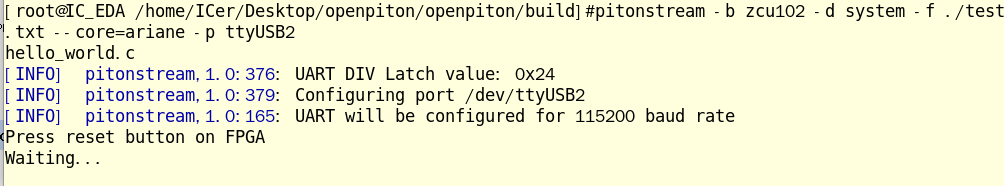

在openpiton文件夹下打开终端输入指令

su

source piton/ariane_setup.sh

cd build

protosyn -b zcu102 -d system --core=ariane --uart-dmw ddr

#注:如果没修改piton/tools/src/proto/dbg.py的print函数会报错,修改文件即可

#错误:TypeError: unsupported operand type(s) for >>: 'builtin_function_or_method' and '_io.TextIOWrapper'. Did you mean "print(<message>, file=<output_stream>)"?运行如果出错,打开vivado,打开build文件夹下对应板卡工程文件查看vivado报错信息即可。

运行结果:

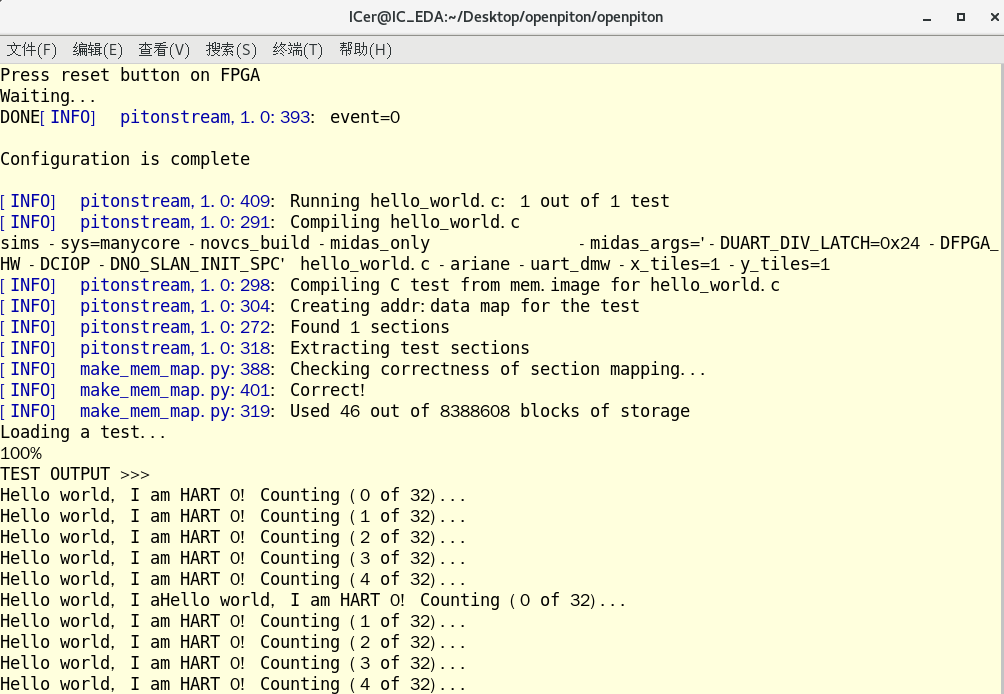

十一、运行嵌入式程序

生成比特流后,打开vivado,进行正常的烧写比特流流程open hardware manager→open target→program devices→program

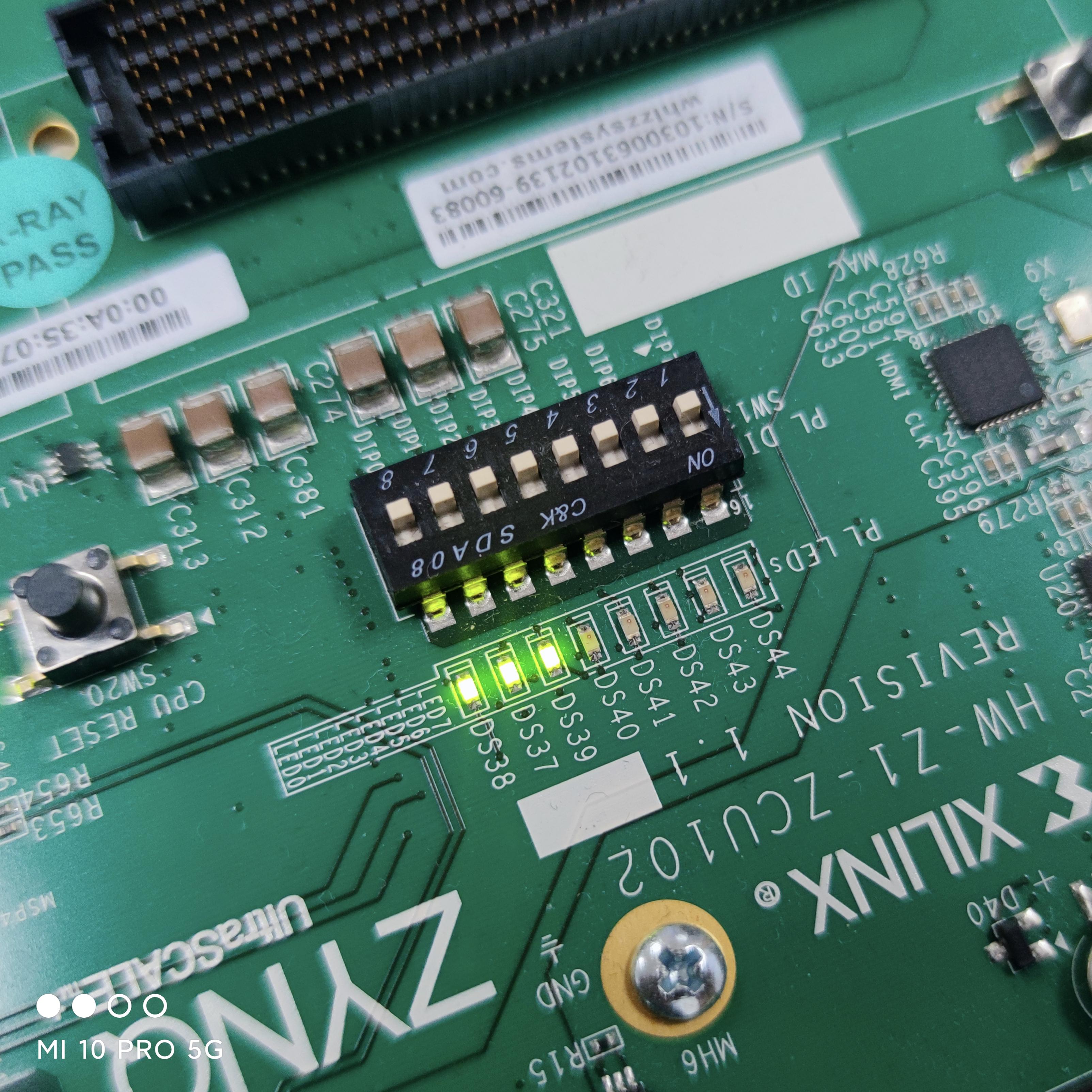

烧写成功后板卡LED灯如图所示:

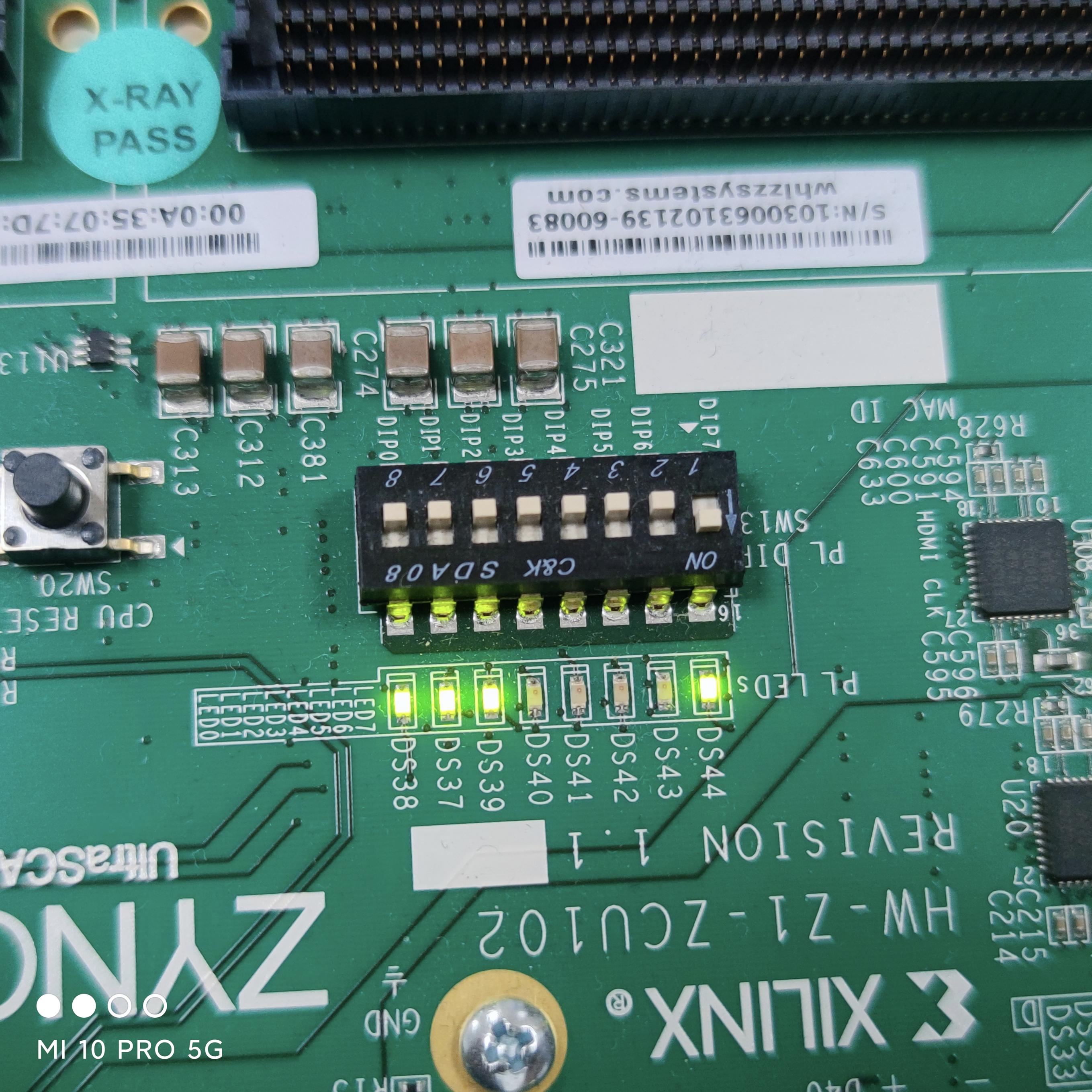

运行嵌入程序前需要将switch 7开关打开才能使用pitonstream脚本烧写程序:

在build文件夹下新建txt文本文件,定义需要仿真的程序(仿真文件默认在openpiton/openpiton/piton/verif/diag/c/riscv/ariane文件夹下):

保存后使用脚本即可烧写嵌入式程序:

在openpiton文件夹下打开终端输入指令

su

source piton/ariane_setup.sh

cd build

pitonstream -b zcu102 -d system -f ./test.txt --core=ariane -p ttyUSB2

#ttyUSB指串口转USB端口,ZCU102有4个串口,ttyUSB2指第二个,一般情况这里是第2个,如果无法仿真切换别的端口试试运行后,脚本会检测开发板的reset信号

按下板卡的reset信号,脚本运行嵌入式程序

智能推荐

oracle 12c 集群安装后的检查_12c查看crs状态-程序员宅基地

文章浏览阅读1.6k次。安装配置gi、安装数据库软件、dbca建库见下:http://blog.csdn.net/kadwf123/article/details/784299611、检查集群节点及状态:[root@rac2 ~]# olsnodes -srac1 Activerac2 Activerac3 Activerac4 Active[root@rac2 ~]_12c查看crs状态

解决jupyter notebook无法找到虚拟环境的问题_jupyter没有pytorch环境-程序员宅基地

文章浏览阅读1.3w次,点赞45次,收藏99次。我个人用的是anaconda3的一个python集成环境,自带jupyter notebook,但在我打开jupyter notebook界面后,却找不到对应的虚拟环境,原来是jupyter notebook只是通用于下载anaconda时自带的环境,其他环境要想使用必须手动下载一些库:1.首先进入到自己创建的虚拟环境(pytorch是虚拟环境的名字)activate pytorch2.在该环境下下载这个库conda install ipykernelconda install nb__jupyter没有pytorch环境

国内安装scoop的保姆教程_scoop-cn-程序员宅基地

文章浏览阅读5.2k次,点赞19次,收藏28次。选择scoop纯属意外,也是无奈,因为电脑用户被锁了管理员权限,所有exe安装程序都无法安装,只可以用绿色软件,最后被我发现scoop,省去了到处下载XXX绿色版的烦恼,当然scoop里需要管理员权限的软件也跟我无缘了(譬如everything)。推荐添加dorado这个bucket镜像,里面很多中文软件,但是部分国外的软件下载地址在github,可能无法下载。以上两个是官方bucket的国内镜像,所有软件建议优先从这里下载。上面可以看到很多bucket以及软件数。如果官网登陆不了可以试一下以下方式。_scoop-cn

Element ui colorpicker在Vue中的使用_vue el-color-picker-程序员宅基地

文章浏览阅读4.5k次,点赞2次,收藏3次。首先要有一个color-picker组件 <el-color-picker v-model="headcolor"></el-color-picker>在data里面data() { return {headcolor: ’ #278add ’ //这里可以选择一个默认的颜色} }然后在你想要改变颜色的地方用v-bind绑定就好了,例如:这里的:sty..._vue el-color-picker

迅为iTOP-4412精英版之烧写内核移植后的镜像_exynos 4412 刷机-程序员宅基地

文章浏览阅读640次。基于芯片日益增长的问题,所以内核开发者们引入了新的方法,就是在内核中只保留函数,而数据则不包含,由用户(应用程序员)自己把数据按照规定的格式编写,并放在约定的地方,为了不占用过多的内存,还要求数据以根精简的方式编写。boot启动时,传参给内核,告诉内核设备树文件和kernel的位置,内核启动时根据地址去找到设备树文件,再利用专用的编译器去反编译dtb文件,将dtb还原成数据结构,以供驱动的函数去调用。firmware是三星的一个固件的设备信息,因为找不到固件,所以内核启动不成功。_exynos 4412 刷机

Linux系统配置jdk_linux配置jdk-程序员宅基地

文章浏览阅读2w次,点赞24次,收藏42次。Linux系统配置jdkLinux学习教程,Linux入门教程(超详细)_linux配置jdk

随便推点

matlab(4):特殊符号的输入_matlab微米怎么输入-程序员宅基地

文章浏览阅读3.3k次,点赞5次,收藏19次。xlabel('\delta');ylabel('AUC');具体符号的对照表参照下图:_matlab微米怎么输入

C语言程序设计-文件(打开与关闭、顺序、二进制读写)-程序员宅基地

文章浏览阅读119次。顺序读写指的是按照文件中数据的顺序进行读取或写入。对于文本文件,可以使用fgets、fputs、fscanf、fprintf等函数进行顺序读写。在C语言中,对文件的操作通常涉及文件的打开、读写以及关闭。文件的打开使用fopen函数,而关闭则使用fclose函数。在C语言中,可以使用fread和fwrite函数进行二进制读写。 Biaoge 于2024-03-09 23:51发布 阅读量:7 ️文章类型:【 C语言程序设计 】在C语言中,用于打开文件的函数是____,用于关闭文件的函数是____。

Touchdesigner自学笔记之三_touchdesigner怎么让一个模型跟着鼠标移动-程序员宅基地

文章浏览阅读3.4k次,点赞2次,收藏13次。跟随鼠标移动的粒子以grid(SOP)为partical(SOP)的资源模板,调整后连接【Geo组合+point spirit(MAT)】,在连接【feedback组合】适当调整。影响粒子动态的节点【metaball(SOP)+force(SOP)】添加mouse in(CHOP)鼠标位置到metaball的坐标,实现鼠标影响。..._touchdesigner怎么让一个模型跟着鼠标移动

【附源码】基于java的校园停车场管理系统的设计与实现61m0e9计算机毕设SSM_基于java技术的停车场管理系统实现与设计-程序员宅基地

文章浏览阅读178次。项目运行环境配置:Jdk1.8 + Tomcat7.0 + Mysql + HBuilderX(Webstorm也行)+ Eclispe(IntelliJ IDEA,Eclispe,MyEclispe,Sts都支持)。项目技术:Springboot + mybatis + Maven +mysql5.7或8.0+html+css+js等等组成,B/S模式 + Maven管理等等。环境需要1.运行环境:最好是java jdk 1.8,我们在这个平台上运行的。其他版本理论上也可以。_基于java技术的停车场管理系统实现与设计

Android系统播放器MediaPlayer源码分析_android多媒体播放源码分析 时序图-程序员宅基地

文章浏览阅读3.5k次。前言对于MediaPlayer播放器的源码分析内容相对来说比较多,会从Java-&amp;gt;Jni-&amp;gt;C/C++慢慢分析,后面会慢慢更新。另外,博客只作为自己学习记录的一种方式,对于其他的不过多的评论。MediaPlayerDemopublic class MainActivity extends AppCompatActivity implements SurfaceHolder.Cal..._android多媒体播放源码分析 时序图

java 数据结构与算法 ——快速排序法-程序员宅基地

文章浏览阅读2.4k次,点赞41次,收藏13次。java 数据结构与算法 ——快速排序法_快速排序法