数电基础:时序逻辑电路的时序分析_数字电路路径最小路径延时是什么-程序员宅基地

技术标签: 静态时序分析 组合逻辑延迟 建立时间与保持时间 STA时序分析 Verilog 最高时钟频率

目录

(1) 对于未引入时钟偏斜时,保持时间与建立时间均不为例必要条件:

(3)引入时钟偏斜也可能会导致保持时间违例,进而输出亚稳态的情况(Tskew21>0)

(4)Tskew21 <0时,即clk2先于clk1到达其时钟端,保持时间就比较容易满足了,但对满足建立时间就有所要求了。

1.组合逻辑延迟

布线延迟与门延迟

数字逻辑电路中,任何输出信号到输入信号之间都有一定的线路延迟,把这种线路延迟叫做布线延迟。当数字逻辑电路经过门电路时,同样会造成一定的延迟,我们把这个延迟叫做门延迟。

2.时钟输出延迟Tco

clock to out的时间,即从时钟触发到数据输出的时间。这是针对触发器器件而言,是触发器的固有参数,不同厂家或不同批次的器件 该参数有差异。

3.同步系统中时钟频率

Tsu : 触发器建立时间

Th : 触发器保持时间

T : 电路的工作周期

Tco : 时钟输出延迟

Tskew : 时钟偏斜(clock skew),又称为时钟偏移,是指时钟信号到达数字电路各部分所用时间差异。

Tcomb: 组合逻辑的延迟。

时钟偏移Skew = 0

为由浅入深,假设 Skew = 0,即说明时钟到达所有器件的时间相同,没有差异,那么图中时钟上升沿1到时钟上升沿2之间刚好相隔一个工作周期T。下面介绍几种情况下的同步时序电路模型的时序图,图中标注了说明。

3.1 建立时间与保持时间都满足

下图为同步时序电路模型时序图1(Tskew=0,建立时间和保持时间都满足):

核心知识点:

(1) Tco+Tcomb将导致数据会延迟到达下一个触发器,要想数据到达下一个触发器时满足建立时间的要求,则必要条件为:

T-(Tco+Tcomb)>Tsu,即有T>Tco+Tcomb+Tsu。因此一个电路搭建好后,会有一个最小的工作周期Tmin=Tco+Tcomb或者最大的工作频率1/Tmin。

(2) 一般电路的工作时钟不是其所能跑的最高频率,那么其实际工作周期要大于其支持的最小工作周期,这个差值就是建立时间的裕量Ts_slack。反映在计算公式上即为:Ts_slack=T-Tmin=T-(Tco+Tcomb)。会不会出现T-(Tco+Tcomb)<Tsu呢?这不就是建立时间违例的情况吗?怎么解决呢?看下面分析。

(3) Tco+Tcomb将会导致数据延迟到达下一个触发器,而下一个触发器不仅仅要求数据提前到达保持稳定一段时间,还要求数据被打入后保持一段时间稳定。假设数据源变化速率很慢,慢于时钟速率问题不大因为相邻周期触发器采样的是同一个值送往下一个寄存器,但同步系统中,数据一般跟随时钟同步跳转,即一个cycle会跳变一次,即数据保持一个时钟周期T的稳定状态。如此,本级寄存器在当前时钟采样的数据经过Tco+Tcomb延迟后到达下一级触发器,那么数据在下级触发器在下次时钟上升沿被打入后仍然会保持Tco+Tcomb时间。下级触发器要想满足保持时间,其必要条件为:Tco+Tcomb>Th .

(4)一般Tco+Tcomb不可能刚好等于Th的,因此当Tco+Tcomb大于Th,那么Th-slack =Tco+Tcomb-Th。会不会出现Tco+Tcomb小于Th呢?这不就是保持时间违例的情况吗,遇到这种情况怎么办呢?下面也有介绍。

综上:要想时序收敛,就是建立保持时间不违例,二者缺一不可。

3.2 建立/保持时间不满足

(1) Tcomb太大导致建立时间不满足

下图为同步时序电路模型时序图2(Tskew =0,组合逻辑延迟太大,导致建立时间不能满足):

解决1:可通过降频(增大周期)以满足建立时间

下图为同步时序电路模型时序图3(Tskew = 0,增加时钟周期以满足建立时间):

解决2:优化组合逻辑

解决3:切割组合逻辑

详见:如何提高电路工作频率

(2) 器件的固有保持时间增大(老化)使得保持时间违例

解决:当不满足保持时间时,通过增大组合逻辑延迟Tcomb来是保持时间满足

当 Tskew不等于0

之前为了简单介绍知识点 ,未引入时钟偏移Tskew,但时间电路中是存在时间偏移的,分析时候不可忽视。

4. 时钟偏斜及其影响

4.1时钟偏斜的物理意义

时钟偏移指定了同时发生的两个时钟信号经过时钟驱动器或布线后到达时间上的差异。

4.2 时钟偏斜对时序的影响

下图给出了未引入和引入时钟偏斜(clock skew)后的同步时序电路图对比模型:

(1) 对于未引入时钟偏斜时,保持时间与建立时间均不为例必要条件:

保持时间不违例:Tco+Tcomb > Th;

建立时间不违例:T>Tco+Tcomb+Tsu。

因此不会产生输出亚稳态现象。也可推出 (T-Tco-Tsu) > Tcomb > (Th-Tco) ,即对组合逻辑延迟的要求。

【注意】:这里面只有时钟周期T和组合逻辑延迟Tcomb可变。

(2)引入时钟偏斜后的时序图如下(Tskew21>0)

图12中,由于引入了Tskew21(>0),导致FF2的时钟段clk2的时序相对于FF1的clk1延后了Tskew,但上图的情况属于并未导致保持时间违例,因此未发生输出亚稳态现象。

仔细分析就可以看出,相对于未引入时钟偏斜时的保持时间裕量(Th-slack = Tco+Tcomb-Th)。此情况中FF2的保持时间裕量变成了Th-slack = Tco+Tcomb-Th-Tskew21,减少了Tskew21。(原因就clk2滞后Tskew21,导致保持时间的起点和终点相对于数据延后了)。

1.保持时间不违例:Tco+Tcomb-Tskew21>Th

即依旧有Th-slack=Tco+Tcomb-Th-Tskew21>0,即Tco+Tcomb-Tskew21>Th ;

2.建立时间不违例:T+Tskew21>Tco+Tcomb+Tsu

只要未引入时钟偏移的时候(Tskew21 == 0)的时候,就满足建立时间要求 T>Tco + Tcomb +Tsu,那么引入Tskew后,时钟 Clk2相对于数据滞后,更能够满足建立时间了。甚至之前尚不满足建立时间要求即T < Tco + Tcomb + Tsu情况下,在引入 Tskew后,就有T+Tskew > Tco +Tcomb + Tsu满足了建立时间。

(3)引入时钟偏斜也可能会导致保持时间违例,进而输出亚稳态的情况(Tskew21>0)

1.保持时间违例:Tco+Tcomb-Tskew21<Th

当引入的 Tskew21不够大时,没有超过保持时间裕量问题不大,但如果Tskew21太大,Tskew21>Tco+Tcomb-Th=Th-slack(未引入偏移时的裕量),就不再满足保持时间的要求,也会导致输出亚稳态。如下图所示;

2.建立时间必然不违例

如情况(2)种描述,只要在未引入时钟偏移的情况下满足建立时间,那么只要Tskew21>0就会必定不违例。并且建立时间的裕量: Ts_slack =Tskew+ (T - Tco -Tcomb -Tsu)增加了Tskew。(情况(2)的建立时间也是如此,在此补充一下)

(4)Tskew21 <0时,即clk2先于clk1到达其时钟端,保持时间就比较容易满足了,但对满足建立时间就有所要求了。

1.保持时间必然不违例

因为在未引入偏移时候就有Tco+Tcomb > Th,只要Tskew21<0,则Tco+Tcomb-Tskew21 >Th必然满足。

2. 建立时间不违例:T+Tskew21 > Tco+Tcomb+Tsu

需要注意的是此时的Tskew21 < 0,因此 T > Tco+Tcomb+Tsu-Tskew21,此时最小时钟周期Tmin=Tco+Tcomb+Tsu-Tskew21 变大了,支持的最大时钟频率减小了。

(5)同理,当Tskew21<0 并且T+Tskew21 < Tco+Tcomb+Tsu , 此时建立时间就违例了,就会产生输出亚稳态现象了。

4.3实例介绍

Ex1:

通常我们可以假设逻辑门的延时为1+0.1k,其中k为逻辑门的输入端个数。比如对于非门,只有一个输入端,那么其延时为1+1*0.1=1.1ns。现有触发器的时序参数为:Tsu=0.6ns, Th=0.4ns, 0.8ns ≤ Tco ≤ 1.0 ns , 需要计算下面电路的最小时钟周期:

答: Tclkmin =Tco-max+Tcomb-max+Tsu=1.0+1.1+0.6=2.7ns。所以该电路最高可跑时钟频率为fmax=1/Tclkmin![]() =370.37Mhz。

=370.37Mhz。

Ex2: 4位计数器电路如下图所示:

电路中有很多电路中有很多路径可以使触发器开始(Enable)或结束(Disable),其中最长的路径开始于触发器Q0结束语Q3。电路中这种最长的路径称为关键路径。如上图中红色路线,包括触发器Q0的时钟信号输出至Q的延时Tco,3个与门,1个异或门以及建立时间Tsu,所以有:

Tclkmin = Tco+3* Tand+Txor+Tsu=1.0+3*1.2+1.2+0.6=6.4ns

fmax = 1/Tclkmin =156.25Mhz

电路的最短路径是每个触发器经过一个异或门到它自身,每条这样的路径的最小延时为Tco+Txor=0.8+1.2=2.0ns>Th=0.4ns, 所以电路中不存在时间违背。

Ex3:在上述Ex2中,是假定时钟clk是同时到达4个触发器的,即时钟clk不存在clock skew、现在我们仍然假设时钟信号clk同时到达Q0、Q1、Q2,但是到达Q3存在一个延时。这种时钟信号到达触发器的时间偏离称为时钟偏斜(clock skew)。关键路径为Q0到Q3,然而Q3的时钟偏斜具有减小延迟的作用。原因在于数据加载到触发器之前就额外的时间,将时钟偏斜skew=1.5ns计算在内,从Q0到Q3的路径上时延为: Tco+3*Tand+Txor+Tsu-Tskew=6.4-1.5=4.9ns(之前的时延为6.4ns)。此时从Q0到Q2的线路径成为关键路径:Tclkmin =Tco+2*Tand+Txor+Tsu=1.0+2*1.2+1.2+0.6=5.2ns,

fmax =1/Tclkmin =192.31Mhz。这种情况下,时钟偏斜会提高时钟频率,但如果时钟偏斜是负的,则会降低时钟频率。

由于时钟偏斜的存在,数据加载到Q3会被延迟,对于所有开始于Q0,Q1,Q2而结束于Q3的路径,加载的延时会提高触发器维持时间的要求(Th+Tskew),其中最短的路径是从Q2到Q3,延迟为Tco + Tand + Txor = 0.8+ 1.2+1.2=3.2ns > Th+Tskew=1.9ns,所以不存在时间违背。

对于时钟偏斜值Tskew >= 2.8ns情况,可以看出存在时间违背,此时不论时钟频率多少,该电路都不可能可靠的工作。

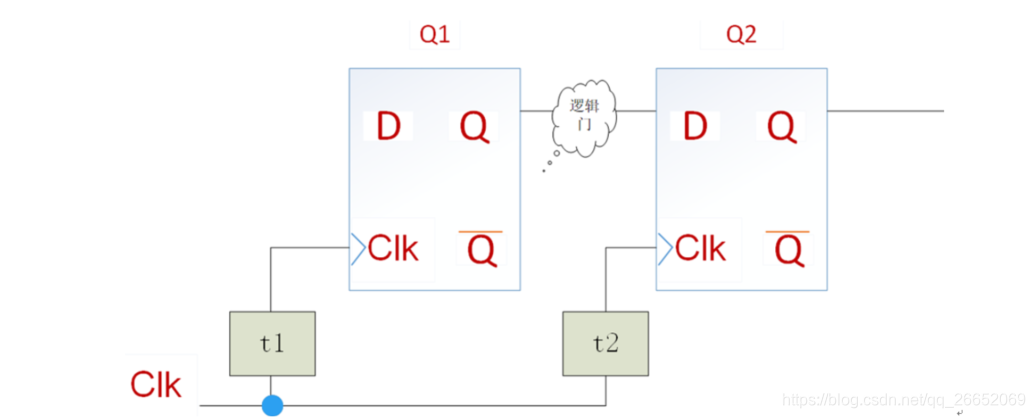

我们再看下面这个例子,在这个电路中有一条路径开始于触发器Q1, 经过一些逻辑门网络,在触发器Q2的D端结束。由图可知,时钟信号到达触发器前存在不同的延迟。假设触发器Q1和Q2的时钟信号延迟分别为t1和t2,这两个触发器之间的时间偏斜可定义为Tskew= t2-t1,假设电路中通过逻辑门路径的最长延迟为TL,则这两个触发器的最小时钟周期为Tclk-min=Tco+TL+Tsu-Tskew, 因此如果t2-t1>0,则时钟频率会提升,否则时钟偏斜会降低频率。

为了计算触发器Q2是否存在时间违背,需要确定触发器的最短路径。如果电路中通过逻辑门的最小延迟为Tl,且Tl+Tco<Th+Tskew, 将会产生时间违背。如果t2-t1>0,维持时间的限制将更难以满足,而如果t2-t1<0,则较易满足。

智能推荐

Kotlin 解压缩_kotlin 对上传的压缩包进行分析-程序员宅基地

文章浏览阅读638次。fun unZip(zipFile: String, context: Context) { var outputStream: OutputStream? = null var inputStream: InputStream? = null try { val zf = ZipFile(zipFile) val entries = zf.entries() while (en..._kotlin 对上传的压缩包进行分析

64K方法数限制解决办法_java函数大于64k编译失败-程序员宅基地

文章浏览阅读1.9k次。随着业务逻辑越来越多,业务模块也越来越大,不可避免会遇到64K方法数的限制。最直观的表现就是编译报错:较早版本的编译系统中,错误内容如下:Conversion to Dalvik format failed:Unable to execute dex: method ID not in [0, 0xffff]: 65536较新版本的编译系统中,错误内容如下:trouble writing outp_java函数大于64k编译失败

案例分享——低压电力线载波通信模组(借助电源线实现远距离数据传输、宽压输入、波特率范围广、应用场景多样化)_电力载波模块csdn-程序员宅基地

文章浏览阅读2k次,点赞7次,收藏10次。物联网领域,有很多数据通信场景,因为原设备整体系统结构、运行环境等方面的限制,需求在不增加通信数据线缆的情况下实现数据的远程传输,因为特殊应用场景下考虑到环境的限制,还不能使用常规的无线通信手段,所以借助电源线缆进行传输的电力线载波技术应运而生,本次博文给大家分享的就是博主完全自主研发的低压电力线载波通信模组。_电力载波模块csdn

密码学基础_密码体制的五个要素-程序员宅基地

文章浏览阅读7.4k次。密码学基本概念 密码学(Cryptology)是结合数学、计算机科学、电子与通信等学科于一体的交叉学科,研究信息系统安全的科学。起源于保密通信技术。具体来讲,研究信息系统安全保密和认证的一门科学。 密码编码学,通过变换消息(对信息编码)使其保密的科学和艺术 密码分析学,在未知密钥的情况下从密文推_密码体制的五个要素

python支持中文路径_基于python 处理中文路径的终极解决方法-程序员宅基地

文章浏览阅读1.9k次。1 、据说python3就没有这个问题了2 、u'字符串' 代表是unicode格式的数据,路径最好写成这个格式,别直接跟字符串'字符串'这类数据相加,相加之后type就是str,这样就会存在解码失误的问题。别直接跟字符串'字符串'这类数据相加别直接跟字符串'字符串'这类数据相加别直接跟字符串'字符串'这类数据相加unicode类型别直接跟字符串'字符串'这类数据相加说四遍3 、有些读取的方式偏偏..._python 路径 中文

阿里云 B 站直播首秀,用 Serverless 搭个游戏机?-程序员宅基地

文章浏览阅读107次。最近,阿云 B 站没声音,是在憋大招!8月5日周四 19:00 是阿里云的直播首秀,给大家请来了 Forrester 评分世界第一的 Serverless 团队产品经理江昱,给大家在线...._阿里云直播b站

随便推点

AS 3.1.3连续依赖多个Module,导致访问不到Module中的类_为什么as在一个包下建了多个module,缺无法打开了-程序员宅基地

文章浏览阅读1.1k次。我好苦啊,半夜还在打代码。还出bug,狗日的。问题是这样的:我在新建的项目里,建了两个Module: fiora-ec和fiora-core。项目的依赖顺序是这样的,App依赖fiora-ec,fiora-ec又依赖于fiora-core,因为这种依赖关系,所有可以在app和fiora-ec中删除一些不必要的引入,比如这个玩意儿:com.android.support:appcompat-v7:..._为什么as在一个包下建了多个module,缺无法打开了

Magento 常用插件二-程序员宅基地

文章浏览阅读1.4k次。1. SMTP 插件 URL:http://www.magentocommerce.com/magento-connect/TurboSMTP/extension/4415/aschroder_turbosmtp KEY:magento-community/Aschroder_TurboSmtp 2. Email Template Adapter..._magento extension pour ricardo.ch

【连载】【FPGA黑金开发板】Verilog HDL那些事儿--低级建模的资源(六)-程序员宅基地

文章浏览阅读161次。声明:本文为原创作品,版权归akuei2及黑金动力社区共同所有,如需转载,请注明出处http://www.cnblogs.com/kingst/ 2.5 低级建模的资源 低级建模有讲求资源的分配,目的是使用“图形”来提高建模的解读性。 图上是低级建模最基本的建模框图,估计大家在实验一和实验二已经眼熟过。功能模块(低级功能模块)是一个水平的长方形,而控制模块(低级控制模块)是矩形。组..._cyclone ep2c8q208c黑金开发板

R语言实用案例分析-1_r语言案例分析-程序员宅基地

文章浏览阅读2.2w次,点赞10次,收藏63次。在日常生活和实际应用当中,我们经常会用到统计方面的知识,比如求最大值,求平均值等等。R语言是一门统计学语言,他可以方便的完成统计相关的计算,下面我们就来看一个相关案例。1. 背景最近西安交大大数据专业二班,开设了Java和大数据技术课程,班级人数共100人。2. 需求通过R语言完成该100位同学学号的生成,同时使用R语言模拟生成Java和大数据技术成绩,成绩满分为100,需要满足正_r语言案例分析

Java知识体系总结(2024版),这一次带你搞懂Spring代理创建过程-程序员宅基地

文章浏览阅读639次,点赞11次,收藏26次。虽然我个人也经常自嘲,十年之后要去成为外卖专员,但实际上依靠自身的努力,是能够减少三十五岁之后的焦虑的,毕竟好的架构师并不多。架构师,是我们大部分技术人的职业目标,一名好的架构师来源于机遇(公司)、个人努力(吃得苦、肯钻研)、天分(真的热爱)的三者协作的结果,实践+机遇+努力才能助你成为优秀的架构师。如果你也想成为一名好的架构师,那或许这份Java成长笔记你需要阅读阅读,希望能够对你的职业发展有所帮助。一个人可以走的很快,但一群人才能走的更远。

车辆动力学及在Unity、UE4中的实现_unity 车辆动力学模型-程序员宅基地

文章浏览阅读3.9k次,点赞9次,收藏53次。受力分析直线行驶时的车轮受力如下:水平方向上,所受合力为:F=Ft+Fw+FfF=F_t+F_w+F_fF=Ft+Fw+Ff其中,FtF_tFt为牵引力,FwF_wFw为空气阻力,FfF_fFf为滚动阻力,下面我们将逐个介绍。驱动力先来说扭矩,扭矩是使物体发生旋转的一个特殊力矩,等于力和力臂的乘积,单位为N∙mN∙mN∙m:设驱动轴的扭矩为TtT_tTt,车轮半径为rrr,那么牵引力:Ft=Tt⁄rF_t=T_t⁄rFt=Tt⁄r如何求得驱动轴扭矩TtT_tTt呢?_unity 车辆动力学模型