FPGA驱动DAC芯片输出(以TLV5618为例)_fpga 双电压输出-程序员宅基地

一、任务

使用FPGA芯片控制DAC采集芯片,输出指定的电压值。

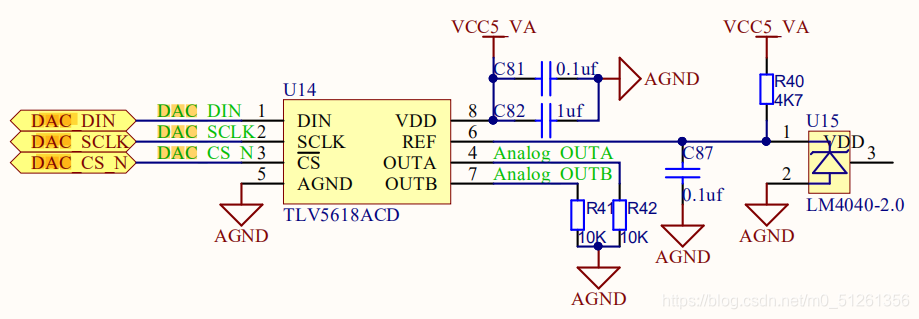

二、硬件部分

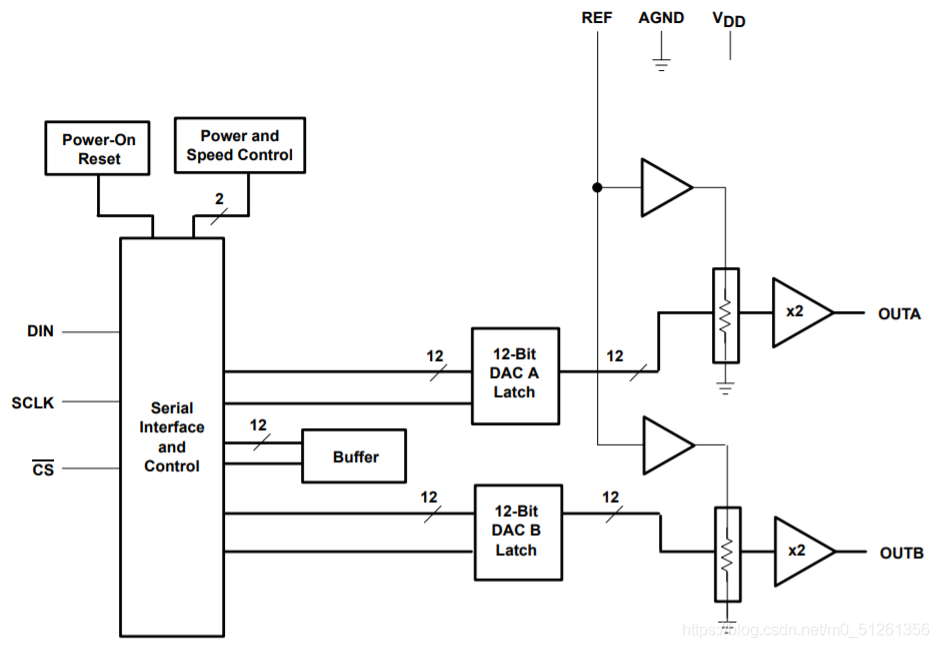

为了将FPGA输出的数字电压转换成模拟电压,我们使用到了数模转换芯片(简称DAC)TLV5618。进行设计前,我们先到网上检索并查看了该芯片的数据手册。

1.芯片功能图

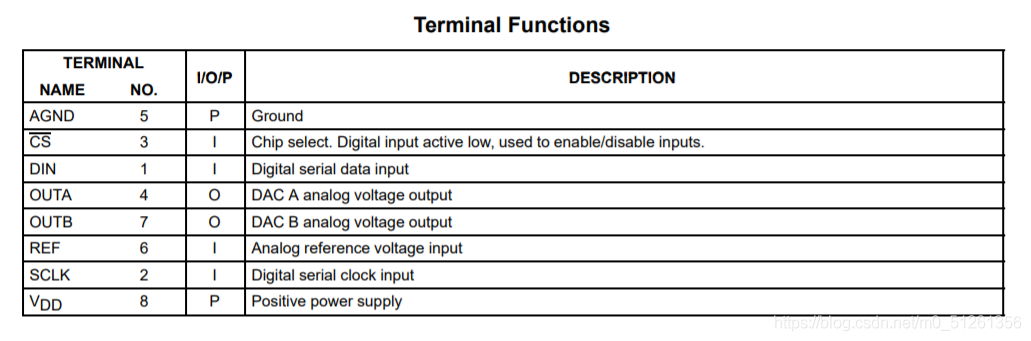

2.端口功能表

从功能图和功能表中我们可以看出,TLV5618有四个输入端口:

片选信号CS、数据串行输入端口DIN、模拟参考电压REF、数字时钟SCLK。

两个输出端分别为OUTA和OUTB,均为对应的模拟电压输出端。

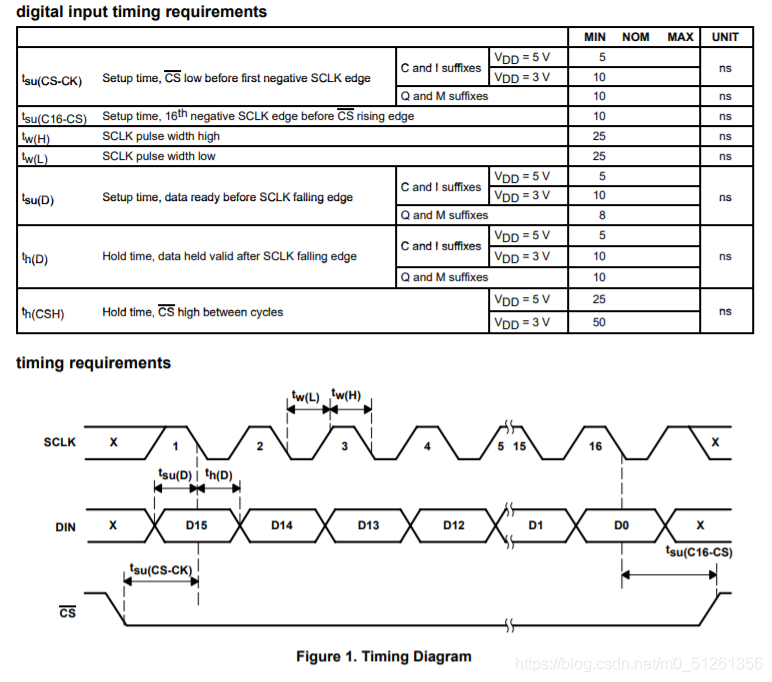

3.时序图

从时序图中我们可以看到使用该芯片时要注意这几个参数:

tw(L):低电平最小宽度,25ns。

tw(H):高电平最小宽度,25ns。

tsu(D):数据最短建立时间。

th(D):数据最短保持时间。

tsu(CS-CK):片选信号下降沿到第一个时钟下降沿最短时间。

th(CSH):片选信号最短拉高时间。

在我们写FPGA代码时,需要根据严格按照时序图来。

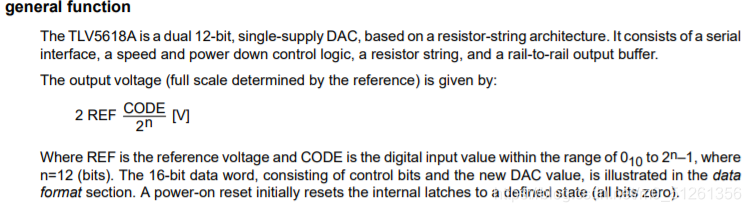

4.输出电压计算

由手册给出的公式知,输出电压与输入的编码值成正比,同时还要乘以一个系数REF,这个系数从芯片的REF引脚输入。我们打开并查看开发板的原理图:

从图中知,我们用到了芯片LM4040-2.0给DAC供电,这个芯片工作时输出电压为4.028V(即精度为12位),故参数REF为4.028。

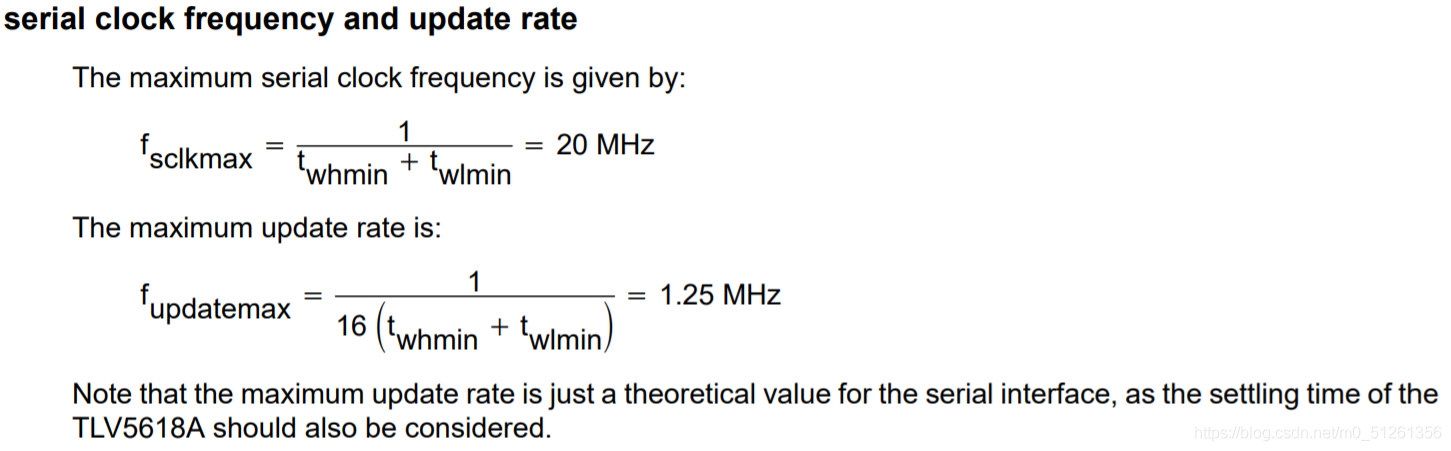

5.时钟频率与刷新率计算

我们查阅手册后知道,使用该芯片时,时钟最大频率为20MHz,刷新率为时钟频率的1/16。而开发板提供的原始时钟为50MHz,因此可以采用四分频后得到12.5MHz的时钟频率。

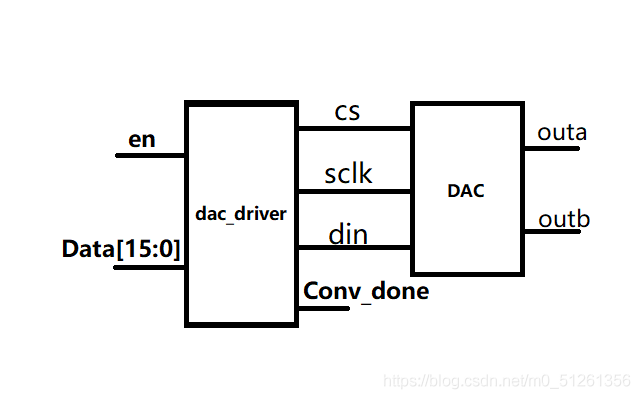

三、设计方案

我们考虑用FPGA设计一个DAC驱动,通过CS、sclk、din三根信号线与DAC芯片连接,设计输入端口Data[15:0]。同时为了便于与其他模块共同协作,我们加上了使能端口en和转换完成标志位Conv_done,这是FPGA设计时必须考虑的一点,对于复杂的驱动模块,这两个信号是不可或缺的。

四、软件部分

这里直接上代码部分,注释里面有解读。

// 驱动部分

module tlv5618(

Clk,

Rst_n,

DAC_DATA, //并行数据输入端

Start, //开始标志位

Set_Done, //完成标志位

DAC_CS_N, //片选

DAC_DIN, //串行数据送给ADC芯片

DAC_SCLK, //工作时钟SCLK

DAC_State //工作状态

);

parameter fCLK = 50; //时钟参数

parameter DIV_PARAM = 2; //分频参数

input Clk;

input Rst_n;

input [15:0] DAC_DATA;

input Start;

output reg Set_Done;

output reg DAC_CS_N;

output reg DAC_DIN;

output reg DAC_SCLK;

output DAC_State;

assign DAC_State = DAC_CS_N; //工作状态标志与片选信号相同

reg [15:0] r_DAC_DATA;

reg [3:0] DIV_CNT; //分频计数器

reg SCLK2X; //2倍SCLK的采样时钟

reg [5:0] 智能推荐

Java Web开发_异步处理以及前端中Vue框架的简单使用(Day3)_后端异步前端怎么处理-程序员宅基地

文章浏览阅读304次。此博客主要记录在学习黑马程序员2023版JavaWeb开发课程的一些笔记,方便总结以及复习。_后端异步前端怎么处理

python数据类型01_python[80., 20., 1000, 200]-程序员宅基地

文章浏览阅读1w次。文章目录数值类型整型(int)long(长整型)浮点数复数不同进制表示数值类型转换数据类型信息获取math 模块、cmath 模块python数学函数abs(x)ceil()cmp()exp()fabs()floor()log()log10()max()min()modf()pow()round()sqrt()python随机数函数choice()randrange()random()seed()..._python[80., 20., 1000, 200]

机器视觉halcon轮廓线处理关键算子-常州龙熙机器视觉培训班_halcon中的轮廓线 导数-程序员宅基地

文章浏览阅读876次,点赞23次,收藏21次。halcon 轮廓线处理 关键算子_halcon中的轮廓线 导数

自动驾驶人机交互HMI产品技术方案_自动驾驶hmi用什么开发-程序员宅基地

文章浏览阅读544次。HMI产品是L4车辆的人机交互程序,为高速运营、港口单车、测试路测等提供状态可视化、任务交互、自动驾驶行车控制、编队控制功能。_自动驾驶hmi用什么开发

Matlab画散点图并拟合(使用cftool函数拟合)_matlab散点图拟合函数-程序员宅基地

文章浏览阅读4w次,点赞13次,收藏120次。Matlab根据坐标点进行绘制散点图并拟合成图像可以使用cftool函数,下面以二维数据拟合进行举例:(1)首先输入数据点x=[0.20,2,4.01,5.99,8.08,9.98,11.96,14.00,15.99,18.00,19.98,21.98,23.99,25.97,28.01,30.00,32.04,33.99,35.98,37.99,39.99,42.00,43.99,45...._matlab散点图拟合函数

Java 命令行运行参数大全_命令行运行java参数-程序员宅基地

文章浏览阅读6.8k次。javac 用法:javac 其中,可能的选项包括: -g 生成所有调试信息 -g:none 不生成任何调试信息 -g:{lines,vars,source} _命令行运行java参数

随便推点

阿里云mysql空间不足_阿里云MySQL 实例空间使用率过高的原因和解决方法-程序员宅基地

文章浏览阅读419次。用户在使用 MySQL 实例时,会遇到空间使用告警甚至超过实例限额被锁定的情况。在 RDS 控制台的实例基本信息中,即会出现如下信息:本文将介绍造成空间使用率过高的常见原因及其相应的解决方法。对于MySQL 5.6版本的实例,升级实例规格和存储空间后即可解锁实例,关于如何升级实例配置,请参见变更配置。•常见原因造成 MySQL 实例空间使用率过高,主要有如下四种原因:Binlog 文件占用高。数据..._阿里云m2实例数超过限制99999

JQuery信息提示框插件 jquery.toast.js 的使用-程序员宅基地

文章浏览阅读1.1w次,点赞5次,收藏13次。1.下载https://github.com/kamranahmedse/jquery-toast-plugin在线预览地址2.导入在页面中引入jquery.toast.css文件,jquery和jquery.toast.js文件。<link type="text/css" rel="stylesheet" href="css/jquery.toast.css">..._jquery.toast.js

vue2+vue3——1~35-程序员宅基地

文章浏览阅读271次。vue2+vue3

电脑远程控制软件哪个好用?(4款远程控制软件推荐)_安企神控制软件-程序员宅基地

文章浏览阅读940次,点赞12次,收藏19次。本文介绍了四款远程控制电脑的软件,这四款远程控制电脑软件操作方法都很简单,大家可以根据自己的需要选择合适的软件即可。在另一台电脑的Chrome浏览器中登录同一个谷歌账号,打开谷歌远程桌面选择要控制的电脑,再输入PIN码即可远程控制电脑。是一款好用的电脑远程控制软件,用户可以通过网络远程连接到其他计算机,轻松实现远程监控、远程技术支持。在两台电脑上都登录QQ账号,主控端电脑打开要控制的好友聊天窗口,单击右上角的更多按钮。,在管理者的电脑上安装管理端,在员工的电脑上安装员工端,安装好后会自动进行连接和上线。_安企神控制软件

80 Gbps 的 USB4 2.0 要来了!_usb4+2.0-程序员宅基地

文章浏览阅读1w次,点赞10次,收藏7次。整理 | 郑丽媛出品 | CSDN(ID:CSDNnews)两年前,英特尔在公布新一代 Thunderbolt 4(以下简称雷电 4)接口标准时曾说:“不是所有 USB4 都能和雷电 4 平起平坐。”如今看来,这句话的顺序可能要颠倒一下了:本月初,USB 推广组官宣了 USB4 v2.0,其可通过 USB Type-C 提供高达 80 Gbps(相当于 10GB/s)的数据传输速率——不仅是 U..._usb4+2.0

【jdk8 jdk17 jdk21 在线中文文档】-程序员宅基地

文章浏览阅读123次。jdk8中文文档jdk17在线文档jdk21在线文档