跨时钟域信号如何处理(一、单bit信号)_跨时钟域信号如何处理(一) luoai_2666-程序员宅基地

背景

一颗芯片上会有许多不同的信号工作在不同的时钟频率下。比如SOC芯片中的CPU通常会工作在一个频率上,总线信号(比如DRAM BUS)会工作在另一个时钟频率下,而普通的信号又会工作在另外的时钟频率下。这3个不同时钟(频率)下工作的信号往往需要相互沟通和传递信号。

不同时钟域下的信号传递就涉及到跨时钟域信号处理,因为相互之间的频率、相位不一样,如果不做处理或者处理不当,如下图所示的时钟域CLK_A的数据信号A可能无法满足时钟域CLK_B的setup/hold时间,可能导致:

1.数据丢失,无法采到预期中的信号;

2.亚稳态的产生。

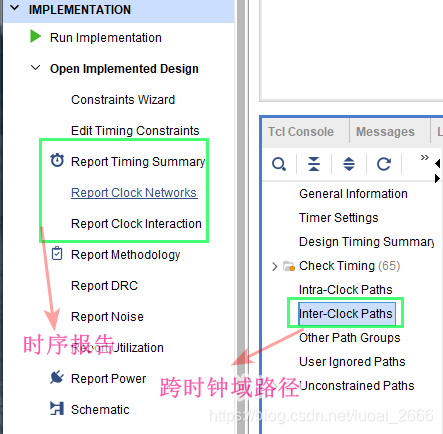

各大FPGA厂家的FPGA编译工具(这是习惯性叫法)在逻辑综合以及实现之后都会出一个时序报告,里面就有跨时钟域的报告,在里面你可以看到你有哪些信号进行了跨时钟域。如下图为Vivado工具的报告位置:

对于这些跨时钟域的情况,一般我们要在逻辑设计的时候就解决,之后的时序约束中设置为false path,即让综合工具不要机关算尽般去布局布线让时序满足要求(这会拖慢编译时间,当然时序也不会成功),设置为false path或者时钟组之后,工具默认不对其进行时序分析(因为设计中已经解决了跨时钟域的问题,这也就是为什么输跨时钟域问题是设计解决的,而不是约束解决的)。

两级DFF同步器

参考资料

https://mp.weixin.qq.com/s/ld466c-zJQWev_Py3HE2Ew

http://blog.sina.com.cn/s/blog_679686370102wn5f.html

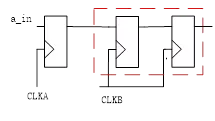

场景:慢时钟域到快时钟域

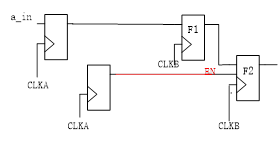

从时钟域A(CLKA)传过来的信号a_in, 直接用时钟域B CLKB采用很容易产生亚稳态,用两级DFF 敲过后再使用就可以把亚稳态概率降到一个合理的值。

很多人可能会问,为什么是两级DFF呢?一级或者三级DFF行不行呢?这里有一个平均失效间隔时间MTBF(Mean Time Between Failure)的考虑。MTBF时间越长,出现亚稳态的概率就越小,但是也不能完全避免亚稳态。注意采样时钟频率越高,MTBF可能会迅速减小。

有文献给出的数据:对于一个采样频率为200Mhz的系统,如果不做同步MTBF是2.5us,一级DFF同步的MTBF大概是23年,两级DFF同步的大约MTBF大概是640年,MTBF越长出错的概率越小。所以一级看上去不太稳,二级差不多够用了,至于三级可能会影响到系统的性能,而且增加面积,所以看上去没什么必要。

module sync_method_1( signal_in_clk1, signal_out_clk2, CLK2);

input signal_in_clk1; //时钟域CLK1里的信号

output reg signal_out_clk2; //时钟域CLK2里的信号

input CLK2; //时钟CLK2

reg signal_r1;

always @(posede CLK2)begin

signal_r1 <= signal_in_clk1;

signal_out_clk2 <= signal_out1;

end

endmodule

注意事项:

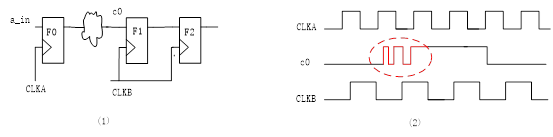

错误1 :时钟域A的组合逻辑信号直接敲两级DFF同步到时钟域B

如下图(1)所示虽然时钟域A的逻辑信号c0 传输到时钟域B的时候,也用了两级DFF 同步器,但我们知道组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺如图(2),而我们又无法预先知道CLKB 的上升沿何时会到来,CLKB 采样到的信号就无法预知,这显然不是我们想要的结果。

因此,要想CLKB 能采到稳定的信号,时钟域A的信号必须是在CLKA打一拍,在一个时钟周期内是稳定的信号,如图(3)所示:

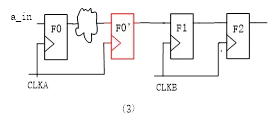

错误2 : Clock-gating enable 信号没有经过异步处理

(暂时没遇到;这en信号不也是一个跨时钟域信号么?直接打两拍处理行不行?)

在下图中a_in 信号经过CLKA的DFF敲过,再送到两级DFF 同步器处理,完全没毛病。但是F2的使能信号EN是从时钟域A来的,当EN信号变化的时候,由于时钟域不一样,无法保证使能之后的CLKB信号采样数据时满足setup/hold time 要求,这时F2输出信号也就变得无法预测了。

两级同步器处理单比特信号虽然比较简单,但还是要注意它的使用方法,不要犯上面的错误哦。

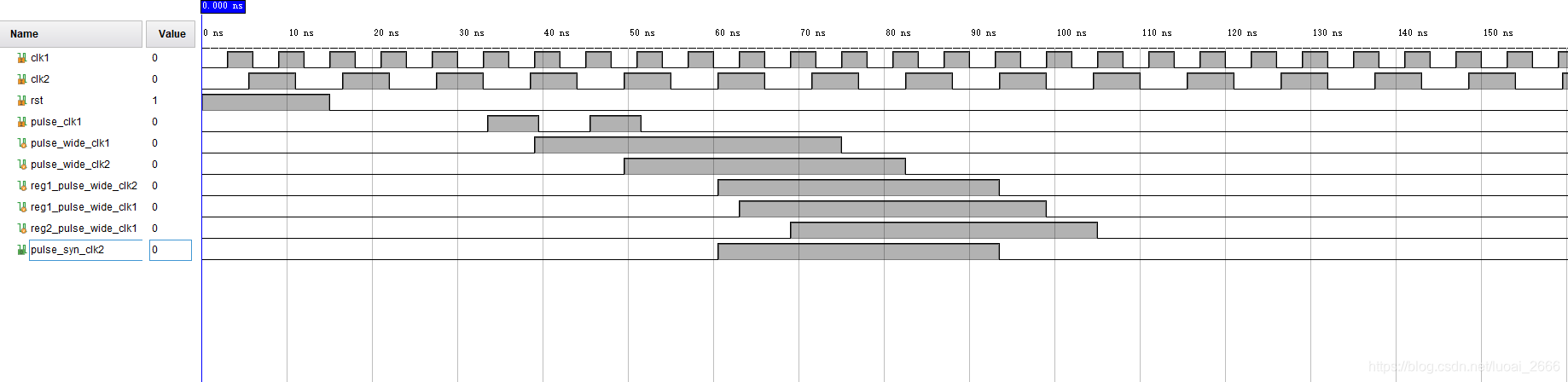

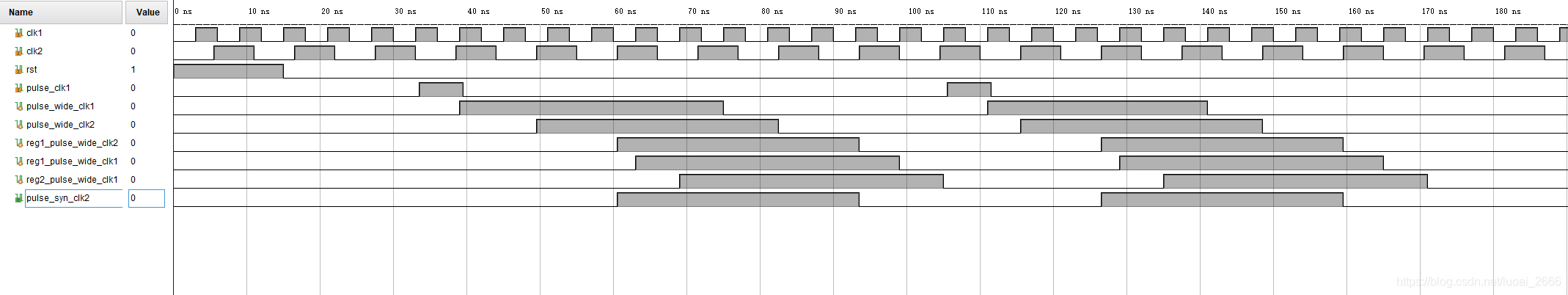

脉冲展宽同步

参考:https://mp.weixin.qq.com/s/mS3JMVDjEu3cvg-oSleeUw

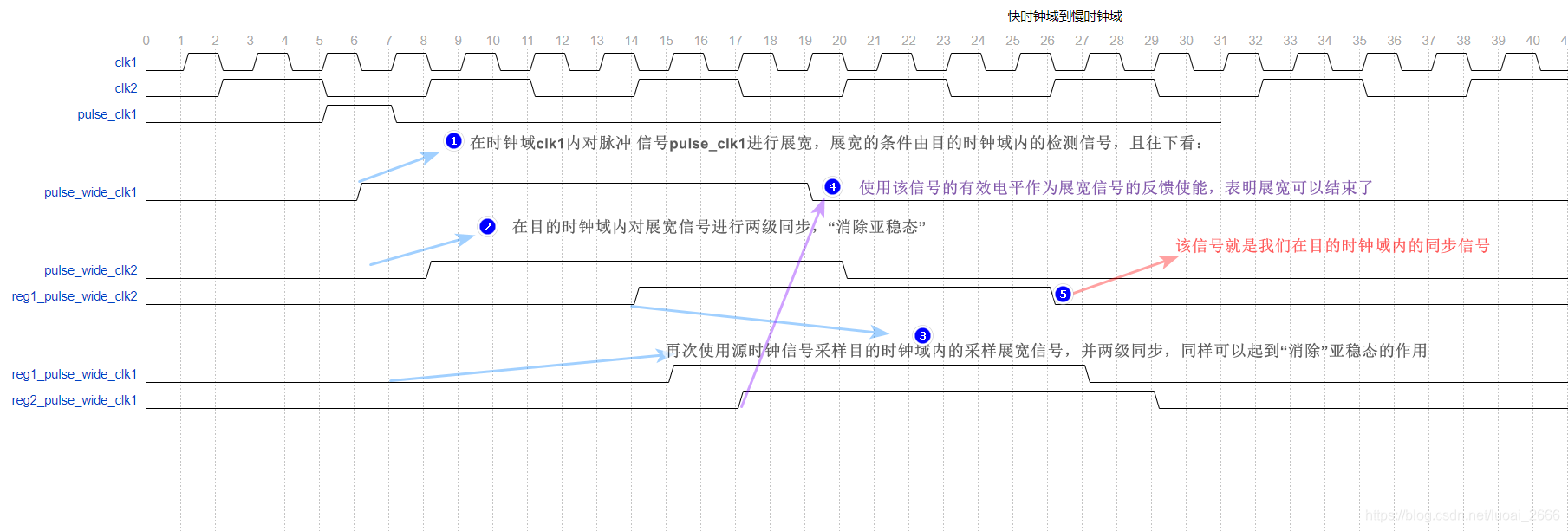

场景:快速时钟域同步到慢速时钟域

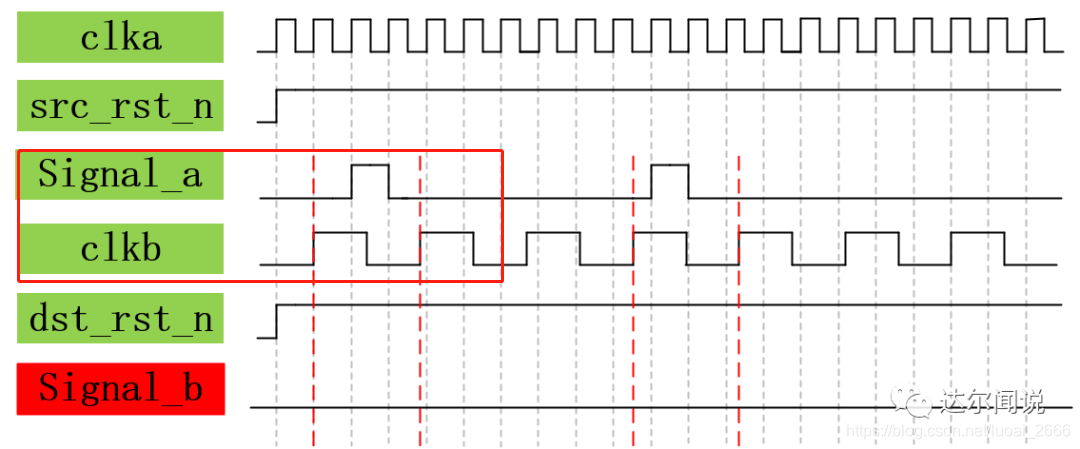

为什么不能直接“打两拍”:慢速时钟域的时钟clkb根本就采集不到快速时钟域clka下的Signal_a脉冲信号,会漏掉数据。

思路:

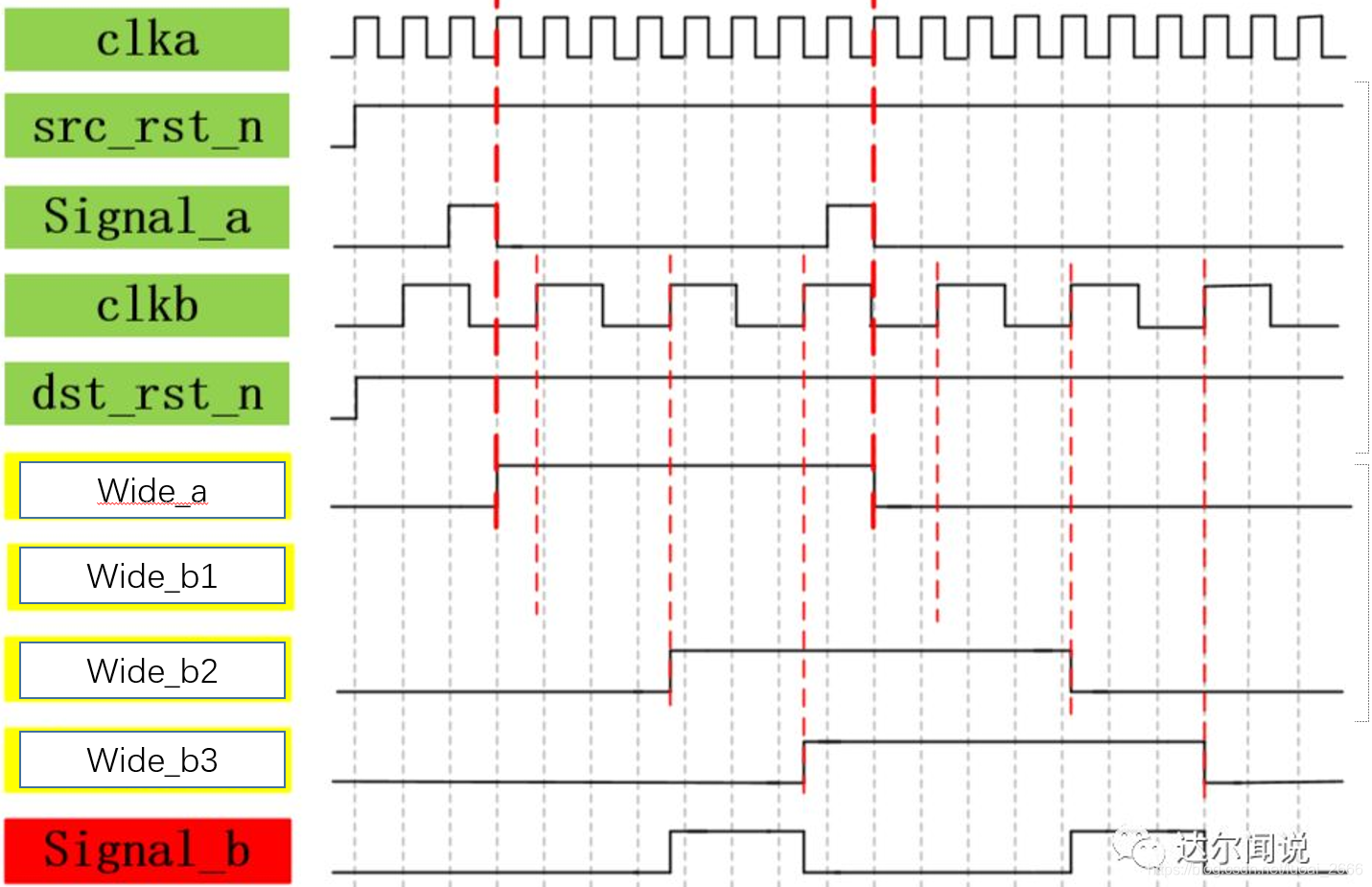

- 让signal_a展宽:每当快速时钟域clka检测到Signal_a脉冲信号为高时,让src_state信号取反,使得Signal_a的第一个脉冲变为src_state信号的上升沿,Signal_a的第二个脉变为wide_a信号的下降沿。

这样就使快速时钟域clka的脉冲信号Signal_a展宽之后在慢速时钟域clkb中能够被采集到 - wide_a打两拍同步到慢速时钟域clkb

- 将wide_b2再转换为脉冲信号:双边沿检测。wide_b1信号可能是不稳定的,而wide_b2信号是稳定的,所以需要将wide_b2信号再打一拍,产生wide_b3信号,再边沿检测,这就是为什么看到一共打了三拍的原因。

这里用组合逻辑实现边沿检测,如果用时序逻辑会延时一拍。

always@(posedge clka) begin

if(signal_a) wide_a <= ~wide_a;

end

always@(posedge clkb) begin

wide_b1 <= wide_a;

wide_b2 <= wide_b1;

wide_b3 <= wide_b2;

end

assign signal_b = wide_b2 ^ wide_b3;

问题:输入脉冲的间隔至少是两个同步器时钟(clkb)周期才行,否则wide_a不够两个clkb周期,wide_b只能维持一个时钟,最终signal_b区分不开signal_a的两个脉冲

需要用握手信号的方法来进一步改进

握手协议

握手信号法

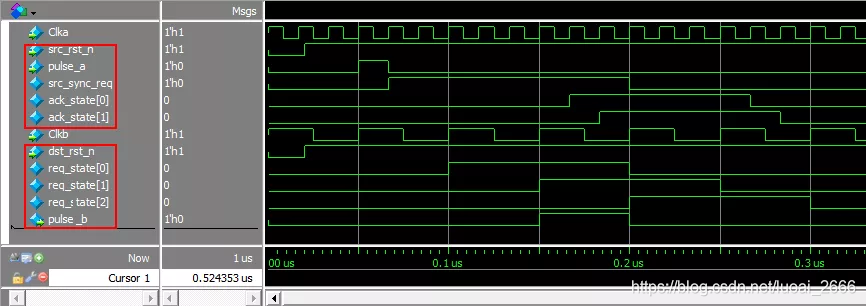

场景:快速时钟域同步到慢速时钟域

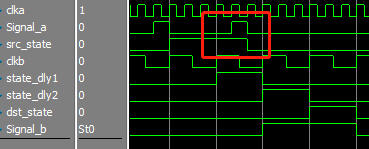

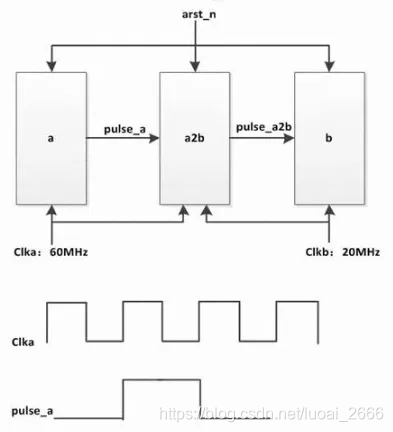

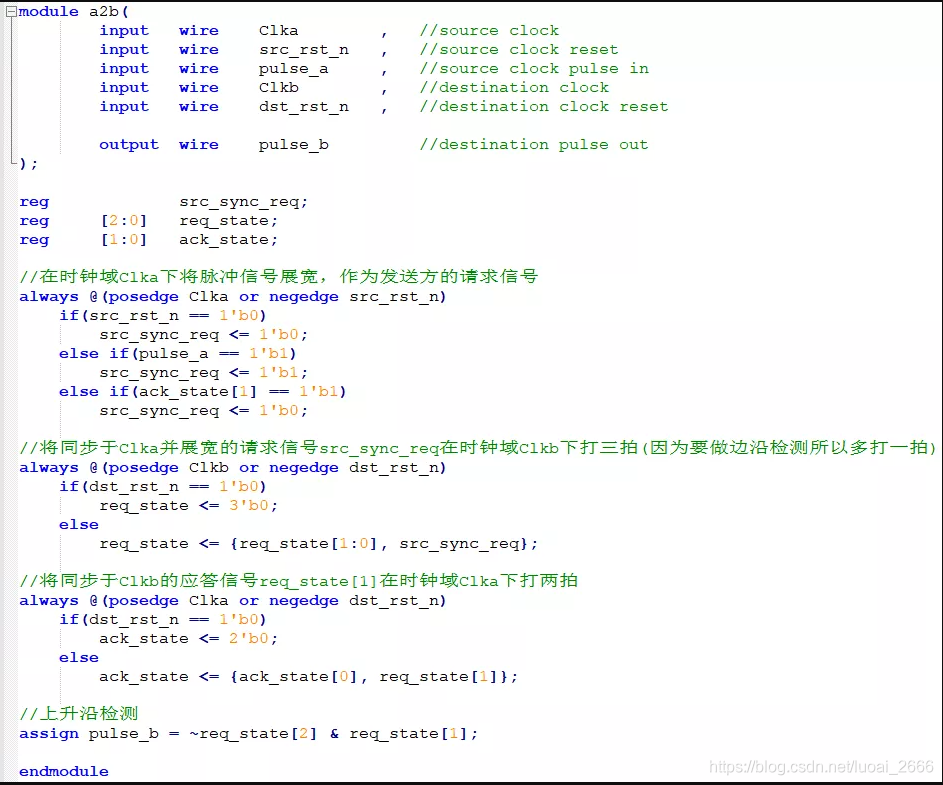

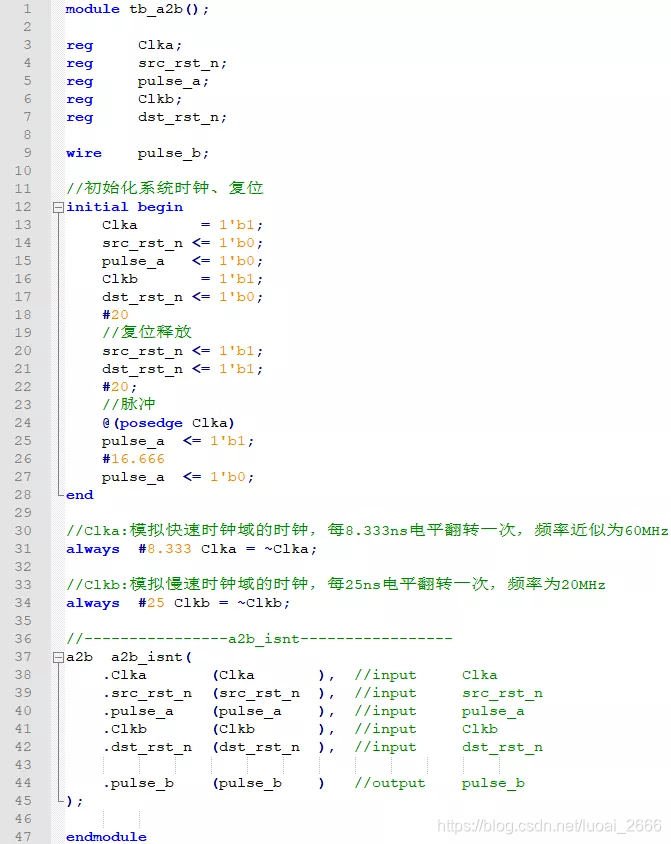

例. 一个系统有两个时钟域的电路,其时钟频率分别为fClka=64MHz和fClkb=20MHz。Clka时钟域驱动一个脉冲信号pulse_a(位宽1bit),传输到Clkb时钟域的电路中,用于触发b模块的某些动作。电路模型和关键时序如下图。请写出a2b模块的rtl代码,并给出评估,你的设计大约用了多少个寄存器?设计中请用异步低复位。(大华FPGA)

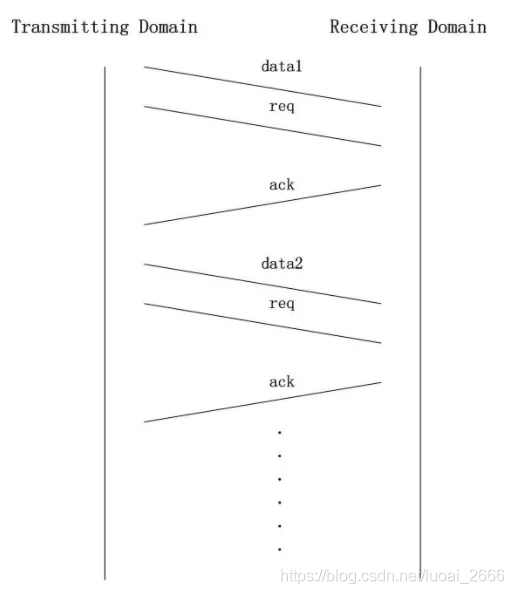

所谓握手,即通信双方使用双向控制信号进行状态指示。这个信号既有发送域给接收域的,也有接收域给发送域的。

注:握手信号法其实也用到了脉冲展宽的方法,只是展宽信号的变化条件不同。因为如果不对脉冲进行展宽慢速时钟域的时钟很有可能无法采集到快速时钟域的信号。

缺点就是延时比较久,而且不能对过近的脉冲进行完美的同步。

如果距离足够远,就可以完美同步:

智能推荐

使用JDBC连接数据库出现 The server time zone value ‘�й���ʱ��‘ is unrecognized or represents more than one解决方案_jdbc.properties timezone-程序员宅基地

文章浏览阅读553次。在 jdbc.properties 文件中的 url 后面加上 ?serverTimezone=UTC加入之前的jdbc.properties文件:user=rootpassword=12345678url=jdbc:mysql://localhost:3306/testdriverClass=com.mysql.cj.jdbc.Driver加入之后:user=rootpassword=12345678url=jdbc:mysql://localhost:3306/test?serv_jdbc.properties timezone

计算机图形学孔令德基础知识,计算机图形学基础教程孔令德答案-程序员宅基地

文章浏览阅读1.4k次。计算机图形学基础教程孔令德答案【篇一:大学计算机图形学课程设】息科学与工程学院课程设计任务书题目:小组成员:巴春华、焦国栋成员学号:专业班级:计算机科学与技术、2009级本2班课程:计算机图形学指导教师:燕孝飞职称:讲师完成时间: 2011年12 月----2011年 12 月枣庄学院信息科学与工程学院制2011年12 月20日课程设计任务书及成绩评定12【篇二:计算机动画】第一篇《计算机图形学》..._计算机图形学基础教程 孔令德 答案

python xlwings追加数据_大数据分析Python库xlwings提升Excel工作效率教程-程序员宅基地

文章浏览阅读1k次。原标题:大数据分析Python库xlwings提升Excel工作效率教程Excel在当今的企业中非常非常普遍。在AAA教育,我们通常建议出于很多原因使用代码,并且我们的许多数据科学课程旨在教授数据分析和数据科学的有效编码。但是,无论您偏爱使用大数据分析Python的程度如何,最终,有时都需要使用Excel来展示您的发现或共享数据。但这并不意味着仍然无法享受大数据分析Python的某些效率!实际上,..._xlwings通过索引添加数据

java8u211_jre864位u211-程序员宅基地

文章浏览阅读911次。iefans为用户提供的jre8 64位是针对64位windows平台而开发的java运行环境软件,全称为java se runtime environment 8,包括Java虚拟机、Java核心类库和支持文件,不包含开发工具--编译器、调试器和其它工具。jre需要辅助软件--JavaPlug-in--以便在浏览器中运行applet。本次小编带来的是jre8 64位官方版下载,版本小号u211版..._jre8是什么

kasp技术原理_KASP基因分型-程序员宅基地

文章浏览阅读5k次。KASP基因分型介绍KASP(Kompetitive Allele-Specific PCR),即竞争性等位基因特异性PCR,原理上与TaqMan检测法类似,都是基于终端荧光信号的读取判断,每孔反应都是采用双色荧光检测一个SNP位点的两种基因型,不同的SNP对应着不同的荧光信号。KASP技术与TaqMan法类似,它与TaqMan技术不同的是,它不需要每个SNP位点都合成特异的荧光引物,它基于独特的..._kasp是什么

华为p50预装鸿蒙系统,华为p50会不会预装鸿蒙系统_华为p50会预装鸿蒙系统吗-程序员宅基地

文章浏览阅读154次。华为现在比较火的还真就是新开发的鸿蒙系统了,那么在即将上市的华为p50手机上会不会预装鸿蒙系统呢?接下来我们就来一起了解一下华为官方发布的最新消息吧。1.华为p50最新消息相信大家都知道,随着华为鸿蒙OS系统转正日期临近,似乎全网的花粉们都在关注华为鸿蒙OS系统优化、生态建设等等,直接忽略了不断延期发布的华为P50手机,如今华为P50系列手机终于传来了最新的好消息,在经过一系列方案修改以后,终于被..._华为手机p50直接预装鸿蒙系统

随便推点

python用什么软件编程好-初学python编程,有哪些不错的软件值得一用?-程序员宅基地

文章浏览阅读2.1k次。Python编程的软件其实许多,作为一门面向大众的编程言语,许多修正器都有对应的Python插件,当然,也有特地的PythonIDE软件,下面我简单引见几个不错的Python编程软件,既有修正器,也有IDE,感兴味的朋友可以本人下载查验一下:1.VSCode:这是一个轻量级的代码修正器,由微软规划研发,免费、开源、跨途径,轻盈活络,界面精练,支撑常见的自动补全、语法提示、代码高亮、Git等功用,插..._python入门学什么好

pytorch一步一步在VGG16上训练自己的数据集_torch vgg训练自己的数据集-程序员宅基地

文章浏览阅读3.2w次,点赞30次,收藏307次。准备数据集及加载,ImageFolder在很多机器学习或者深度学习的任务中,往往我们要提供自己的图片。也就是说我们的数据集不是预先处理好的,像mnist,cifar10等它已经给你处理好了,更多的是原始的图片。比如我们以猫狗分类为例。在data文件下,有两个分别为train和val的文件夹。然后train下是cat和dog两个文件夹,里面存的是自己的图片数据,val文件夹同train。这样我们的..._torch vgg训练自己的数据集

毕业论文管理系统设计与实现(论文+源码)_kaic_论文系统设计法-程序员宅基地

文章浏览阅读968次。论文+系统+远程调试+重复率低+二次开发+毕业设计_论文系统设计法

在python2与python3中转义字符_Python 炫技操作:五种 Python 转义表示法-程序员宅基地

文章浏览阅读134次。1. 为什么要有转义?ASCII 表中一共有 128 个字符。这里面有我们非常熟悉的字母、数字、标点符号,这些都可以从我们的键盘中输出。除此之外,还有一些非常特殊的字符,这些字符,我通常很难用键盘上的找到,比如制表符、响铃这种。为了能将那些特殊字符都能写入到字符串变量中,就规定了一个用于转义的字符 \ ,有了这个字符,你在字符串中看的字符,print 出来后就不一定你原来看到的了。举个例子>..._pytyhon2、python3对%转义吗

java jar 文件 路径问题_「问答」解决jar包运行时相对路径问题-程序员宅基地

文章浏览阅读1.3k次。我这几天需要做一个Java程序,需要通过jar的形式运行,还要生成文件。最终这个程序是要给被人用的,可能那个用的人还不懂代码。于是我面临一个问题:生成的文件一定不能存绝对路径。刚开始我想得很简单,打绝对路径改成相对路径不就行了吗?于是有了这样的代码:String path = "../test.txt";File file = new File(path);……这个写法本身并没有问题,直接运行代码..._jar启动文件路径中存在!

微信读书vscode插件_曾经我以为 VSCode 是程序员专属的工具,直到发现了这些……...-程序员宅基地

文章浏览阅读598次。如果你知道 VSCode,一说起它,你可能第一个想到的就是把它当做一个代码编辑器,而它的界面应该可能大概率是这样的——如果你恰好又是个程序员,那你可能经常会用到它,不管是 Python、JS 还是 C++ 等各种语言对应的文件,都可以用它来进行简单的编辑和整理,甚至是运行和 debug......但是今天要讲的显然不是这些,经过小美的多方研究,发现了即使是对于大多数并不了解 VSCode,也完全不..._vscode weixin read