FPGA编程神器,亲测好用,非常舒适!_fpga助手-程序员宅基地

技术标签: 生产力工具 自动生成状态机 fpga开发 自动例化 verilog语法检查 VScode

今天给大家安利一款免费的FPGA编程神器,名为Digital IDE 。你能想到的功能他都具备,你想不到的功能他也具备。如何使用见文末。

功能大全

标★的是我认为非常棒的功能,并且是一般工具所不具备的。

语言支持

- 语言高亮

- 文件标志

- 定义跳转★

- 悬停提示

- 工程结构★

- 语法诊断

- 自动格式

- 自动补全

- 语言翻译

- 快速例化★

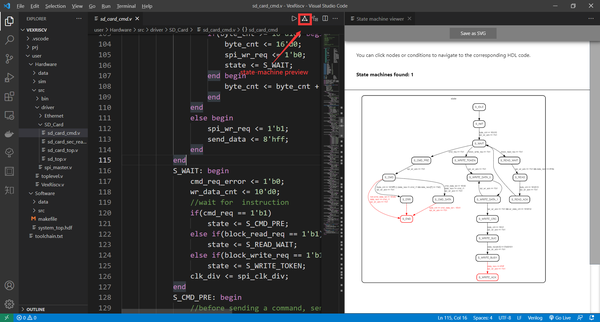

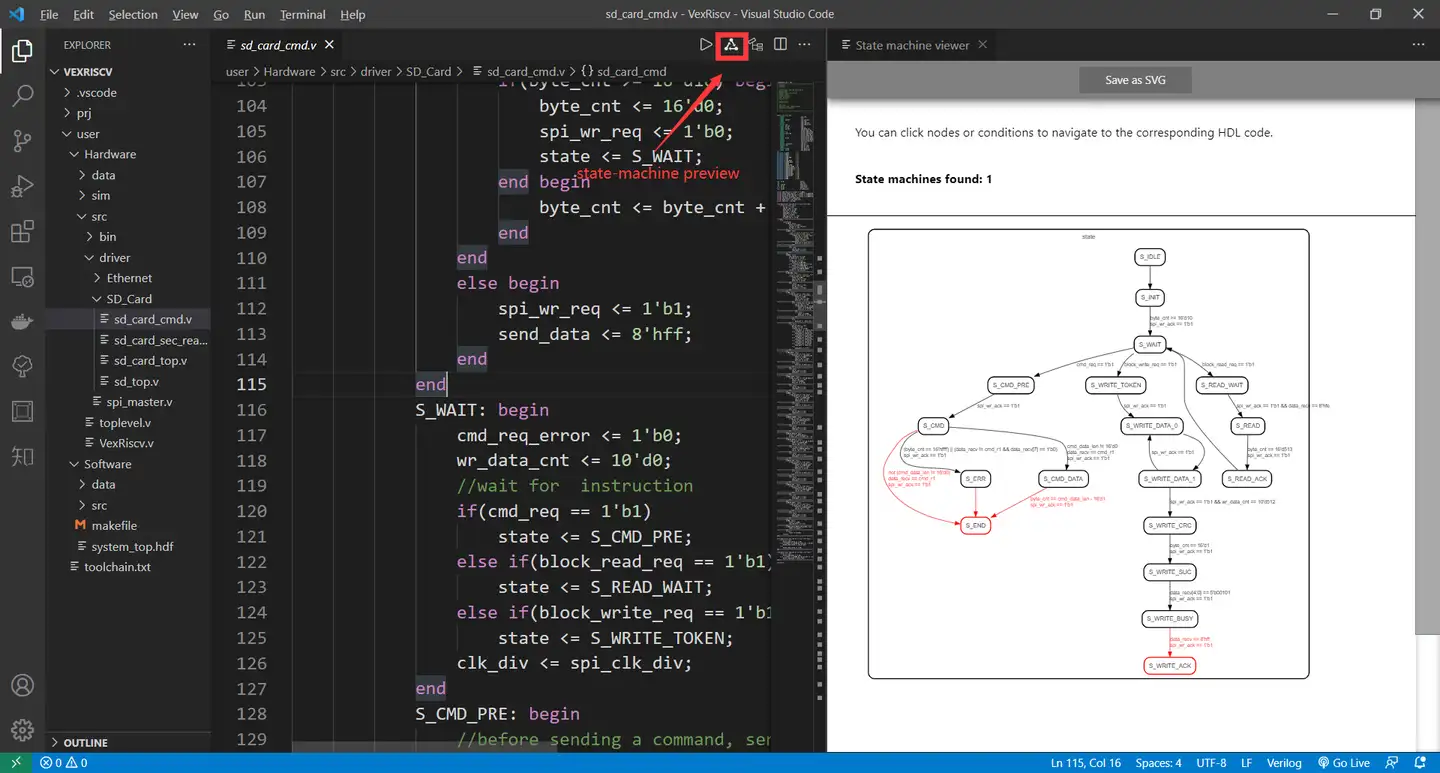

- 状态转移图自动生成★

仿真功能

-

自动生成test bench★

-

vivado快速仿真

-

iverilog快速仿真

支持常见功能库

vivado开发辅助

ZYNQ开发辅助

功能介绍

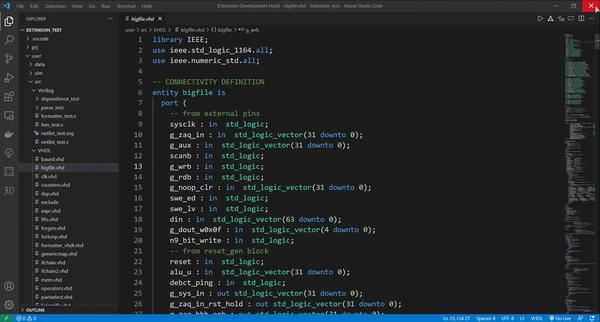

语言支持

提供前端代码设计所需的基本语言服务

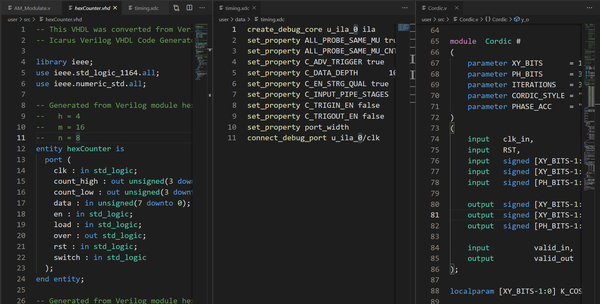

语言高亮

- Verilog

- SystemVerilog

- VHDL

- TCL (包括xdc、sdc、fdc约束文件)

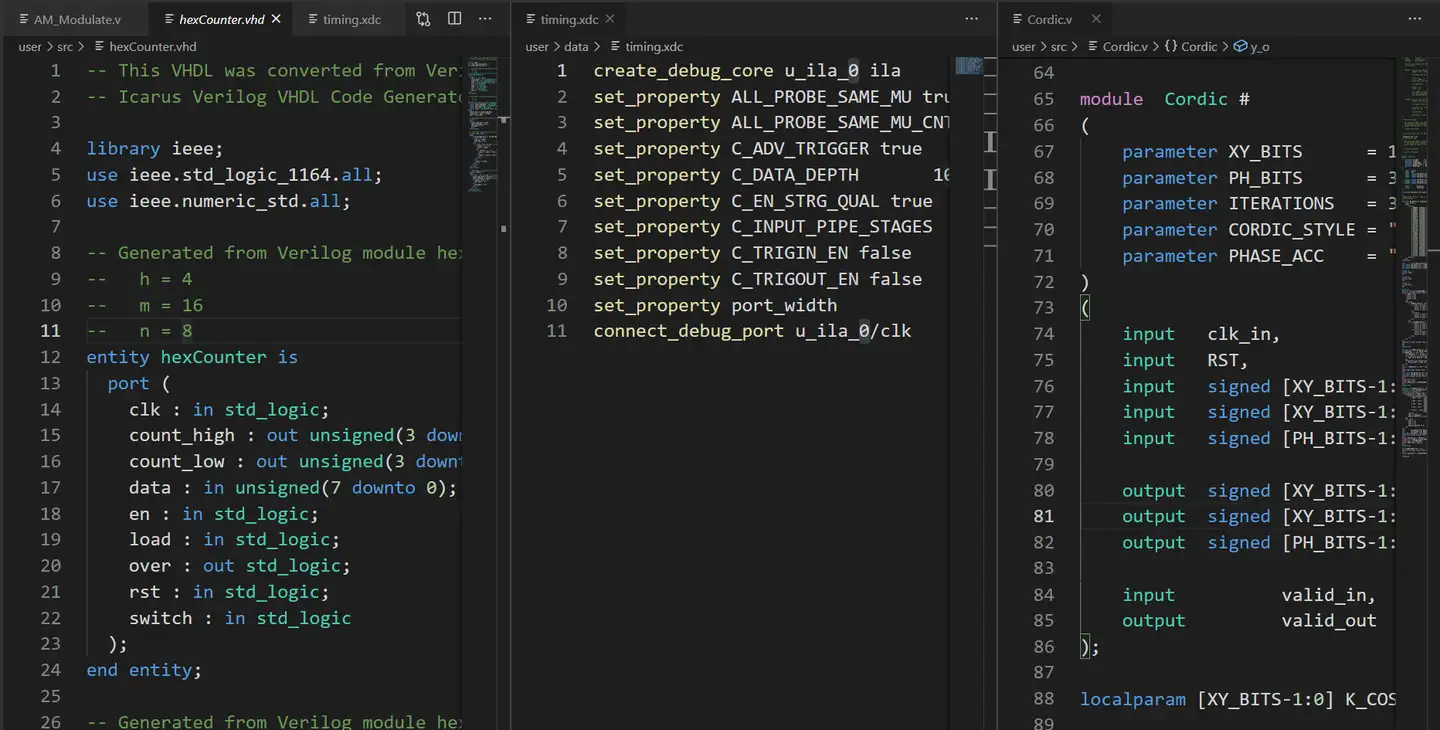

语法诊断

该语法诊断可以针对不同的语言类型灵活使用不同的诊断器

在该功能中默认使用的是vivado系列,可以根据已有环境搭配不同的诊断组合,但当选择default时则认为关闭诊断

针对 verilog 以及 systemverilog

HDL.linting.vlog.linter 支持的有:

- vivado

- modelsim

- iverilog

- verilator

- verible

针对 vhdl

HDL.linting.vhdl.linter 支持的有:

- vivado系列

- modelsim系列

- ghdl

针对自动语法检查导致不太好的编码体验,设置了两种触发检查的模式。运行模式在设置中 HDL.linting.mode 可进行更改,默认为auto模式,自动触发,即在打开文件和保存文件时触发语法检查功能。还有一种为手动触发的manual模式,在所需要的检查的文件页面上右击,选择 syntax check 即可对当前文件进行语法检查。

文件标志

悬停提示

主要提示的内容为当前文件内定义的数据类型以及例化模块的相关信息。

【注】:悬停提示使用的是内置的vlog和vhdl解析器,目前暂时只支持简单的悬停提示

自动补全

【注】:目前自动补全只支持在verilog和systemverilog中例化模块里进行端口参数例化时的补全

定义跳转

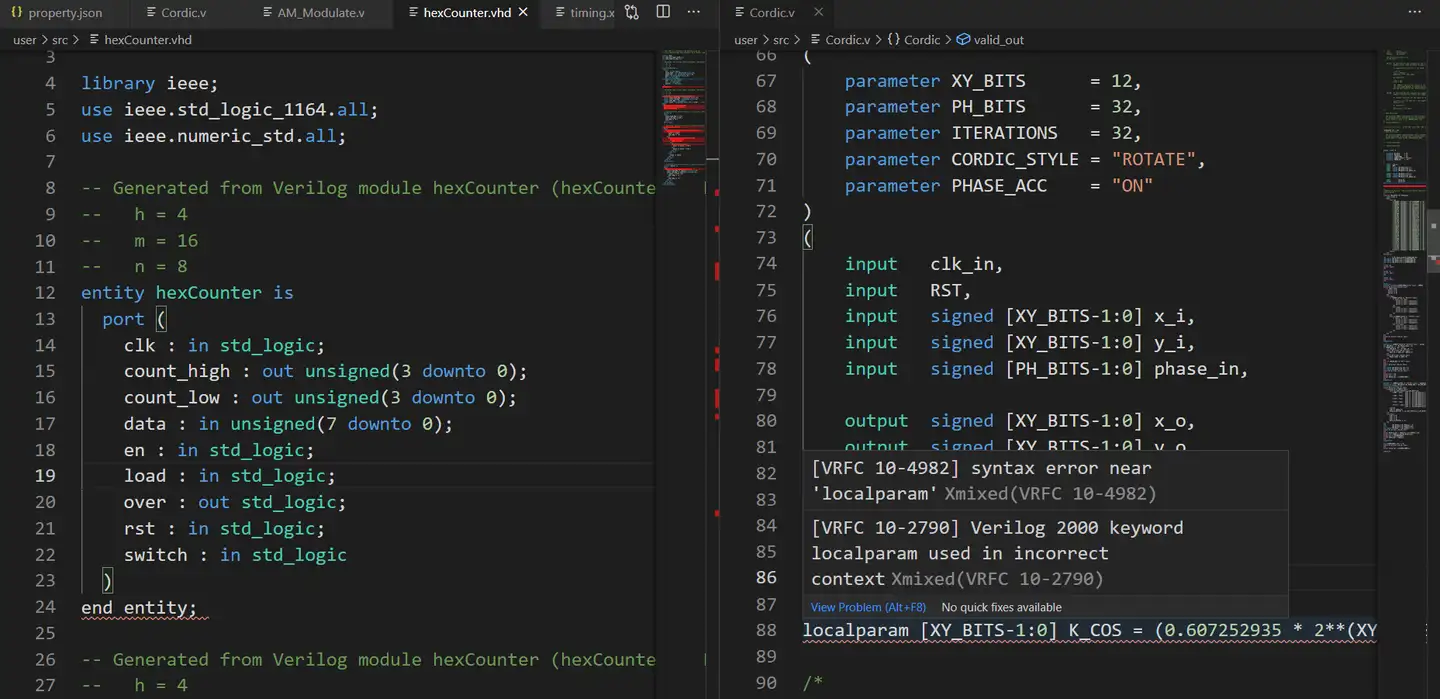

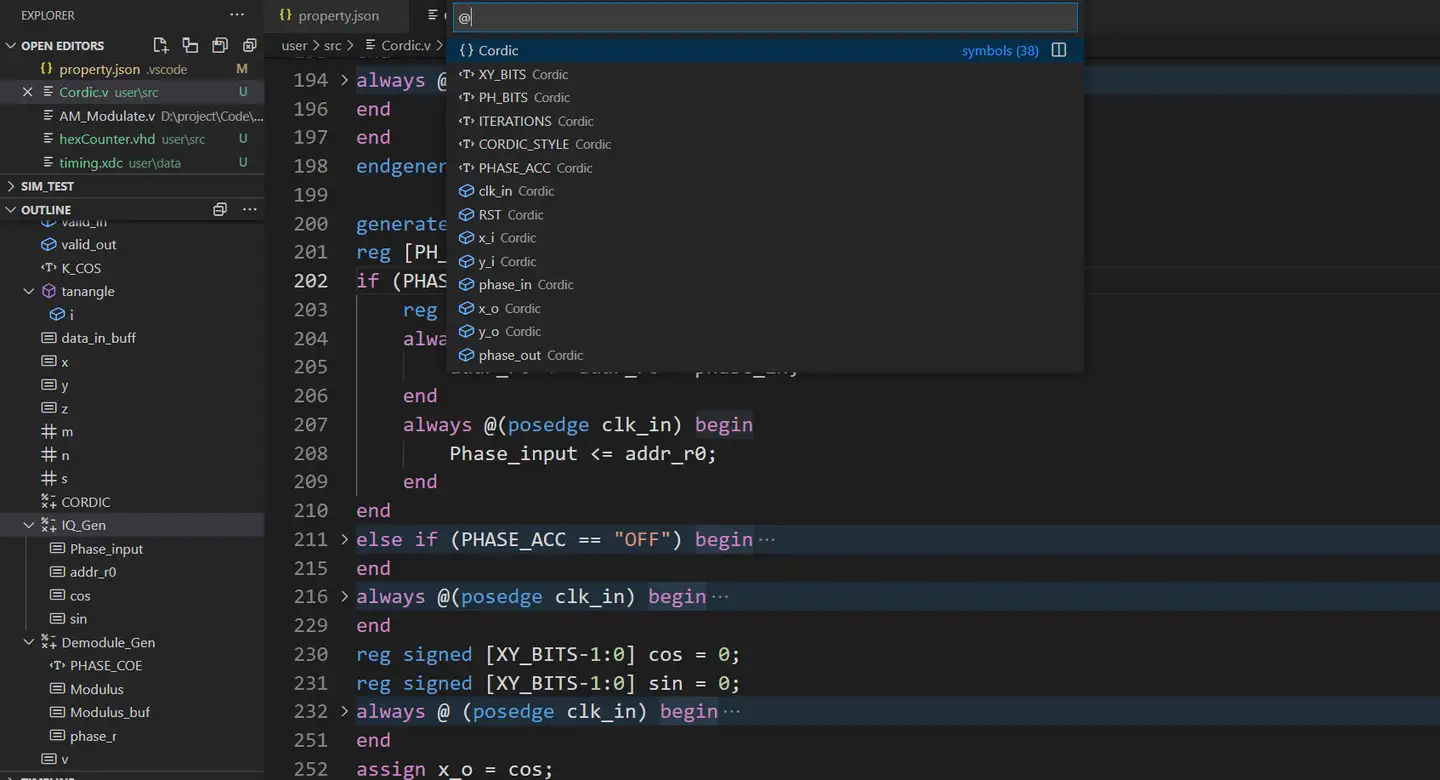

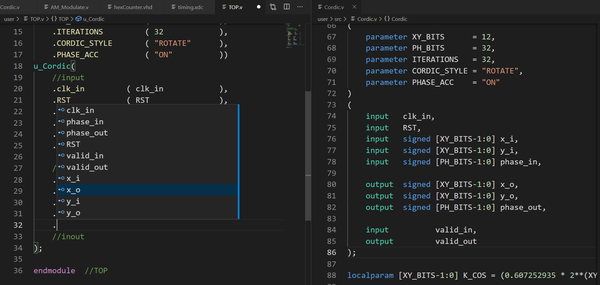

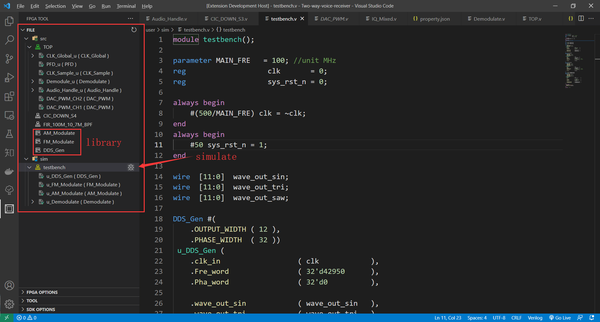

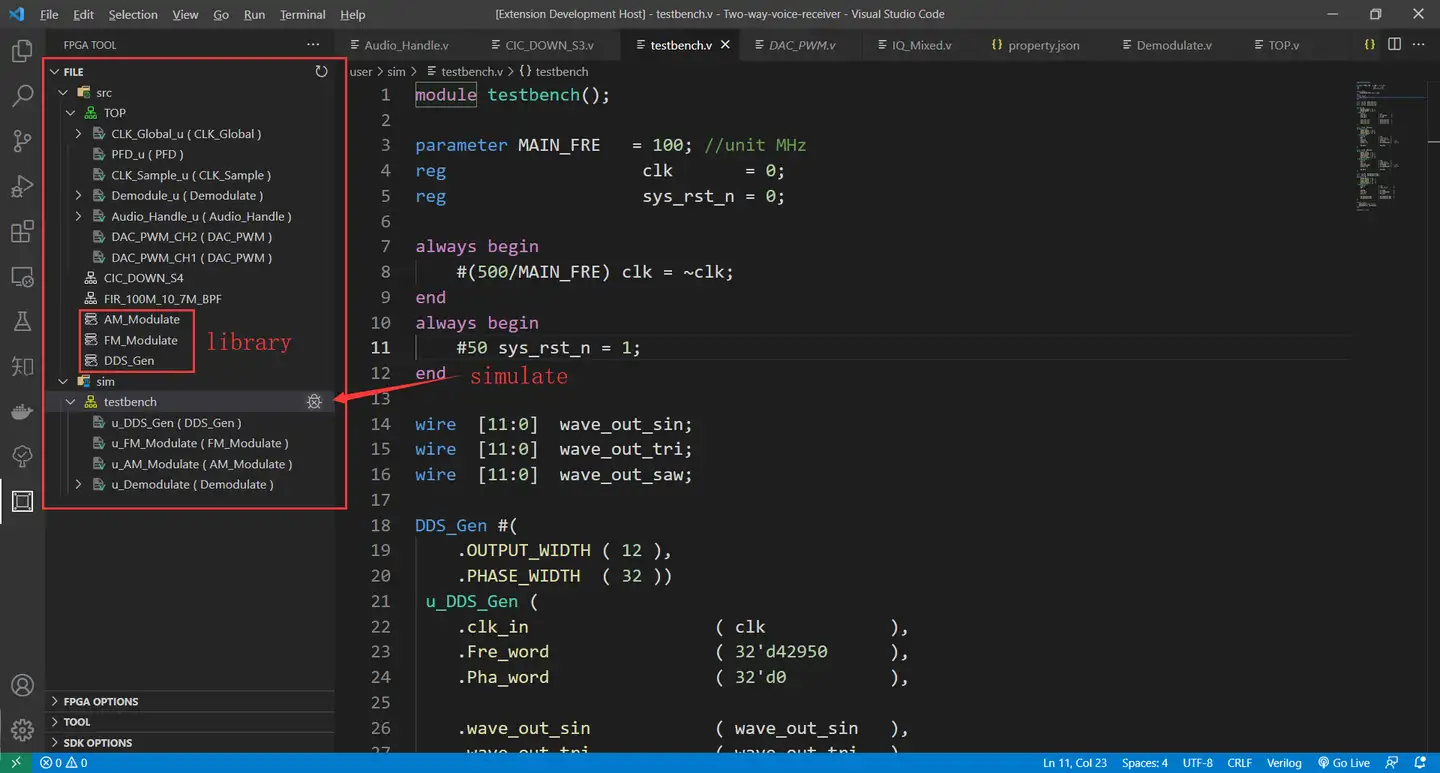

工程结构

工程结构,以层级关系显示出HDL文件之间包含与被包含关系,单击后可打开对应的文件。

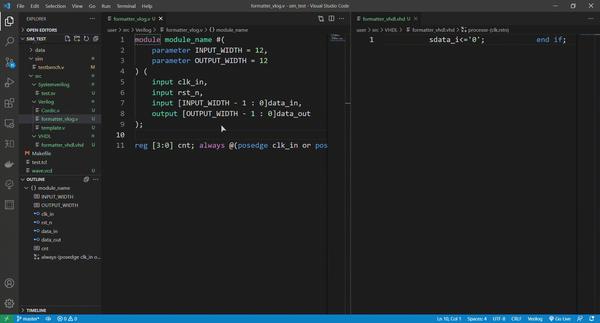

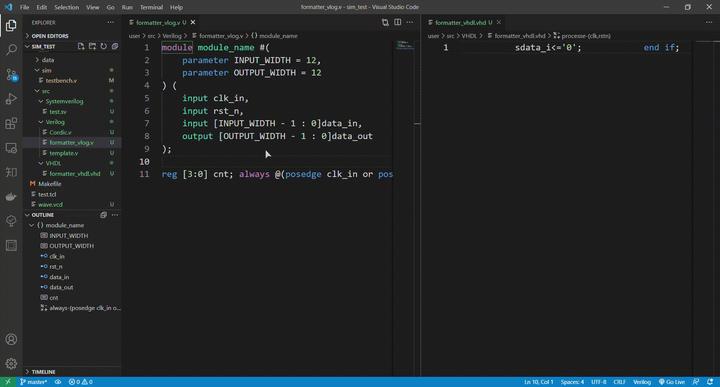

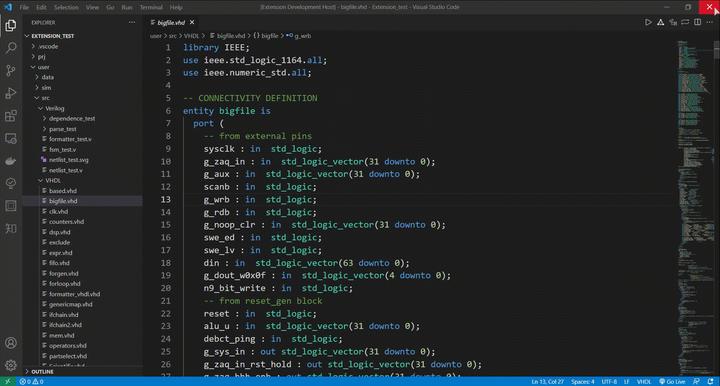

自动格式化

可以对选中的字符或者全文进行文档的格式化 vscode自带快捷键打开方式:shift + alt + f

- verilog and systemverilog

HDL.formatter.vlog.default.style

verilog 和 systemverilog格式化类型,支持三种类型

kr、ansi、gunHDL.formatter.vlog.default.args

其他参数输入,vlog的格式化使用的是istyle的webassembly因此要输入的参数请参考istyle

【注】:由于该功能是基于istyle来实现的因此对全文格式化依旧不是很完善,建议选中always语句块来进行格式化,后期会持续修复相关问题。

- vhdl

HDL.formatter.vhdl.default.align-comments

是否需要对齐注释

HDL.formatter.vhdl.default.indentation

tab所对应的空格数量

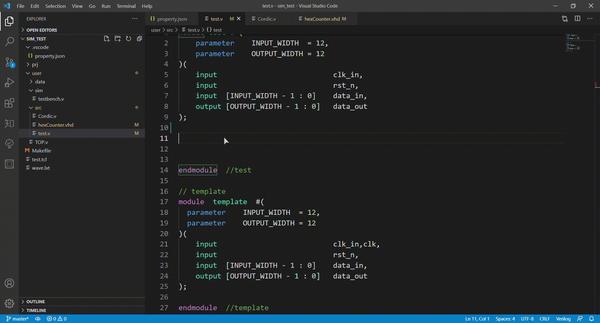

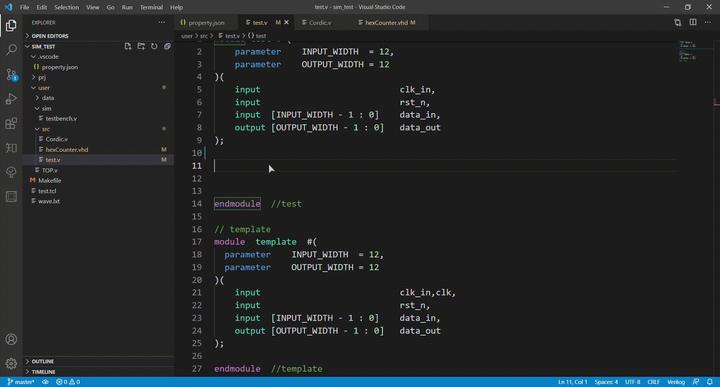

vhdl转Verilog翻译

目前只支持vhdl转Verilog的翻译功能具体使用办法见如下gif:

状态机预览

仿真功能

生成tb并例化

步骤如下:

- 使用快捷键

F1启动命令框,输入 Testbench, 选择TOOL : Testbench, 或者在需要生成并例化的文件下右击选择Testbench。 - 选择仿真文件的类型以及需要存储的位置,如果存在直接替换即可。

【注】: 如果想要更改初始的testbench file的内容则使用快捷键F1启动命令框,选择TOOL : Overwrite the template of testbench,选择要更改的仿真文件的类型,这时会打开testbench file的初始化文件在此基础上更改保存即可。此外请保留 //Instance 标志,该标志是用于识别需要例化的位置。

该功能不是很建议使用,直接在tb文件中使用instance指令生成更方便。

后期会考虑tb文件与例化模块间的智能连线。

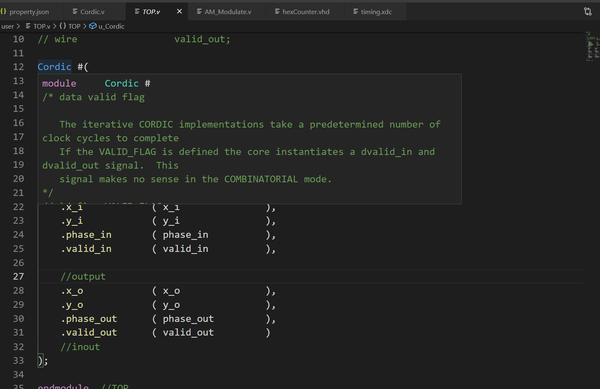

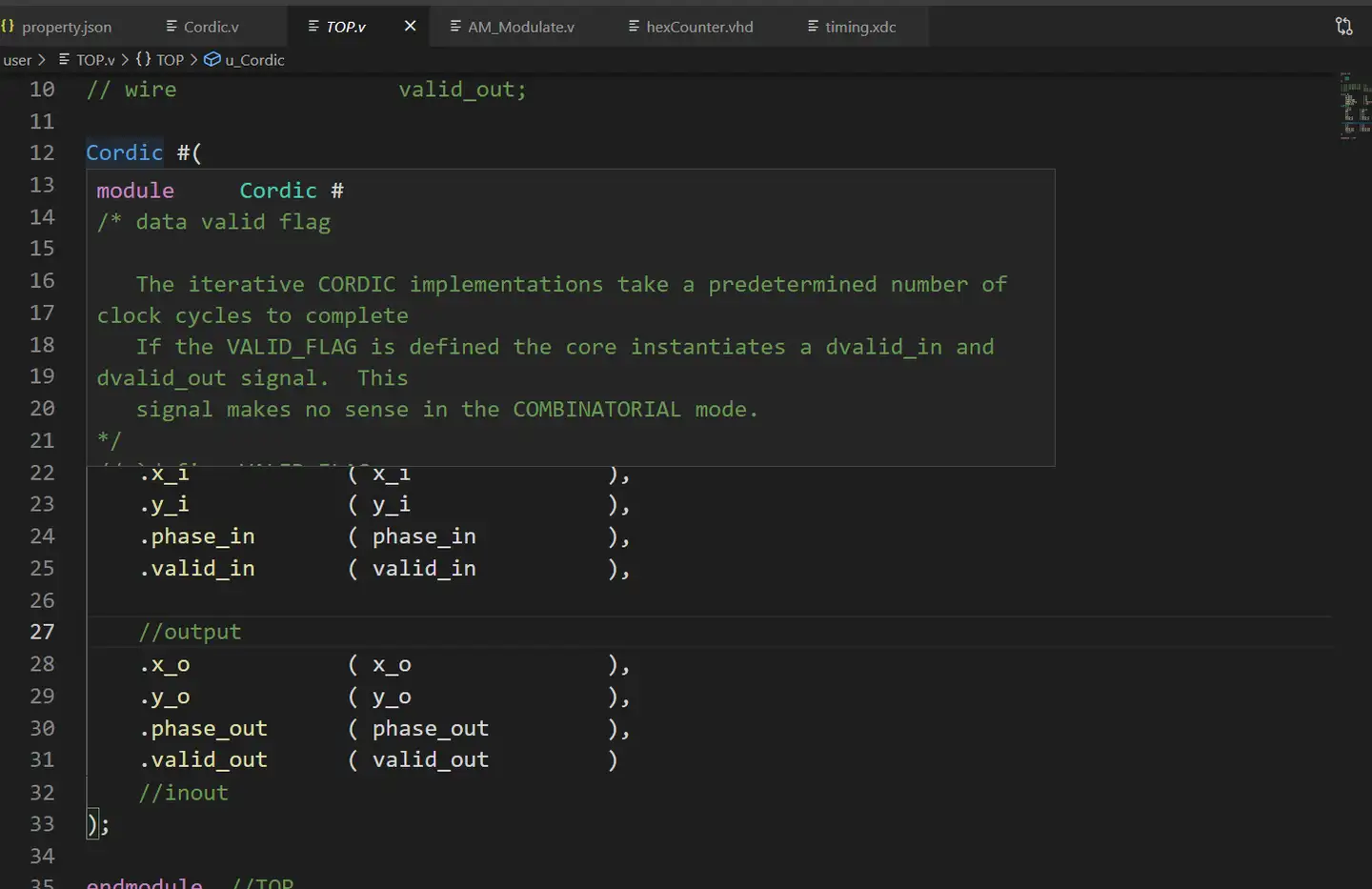

自动例化

该插件支持在Verilog文件中例化Verilog和vhdl模块,同时支持在vhdl文件中例化Verilog和vhdl模块 步骤如下:

- 将光标放置在文本需要例化处。

- 使用快捷键

F1启动命令框,输入instance,选择Tool.instance。 - 输入需要例化的模块的关键字。

- 选择需要例化的模块。

或者是使用快捷键 Alt + I 进行启动,再输入需要例化的模块的关键字,选择需要例化的模块。

【注】:在使用快捷键时其检查是否快捷键键冲突。

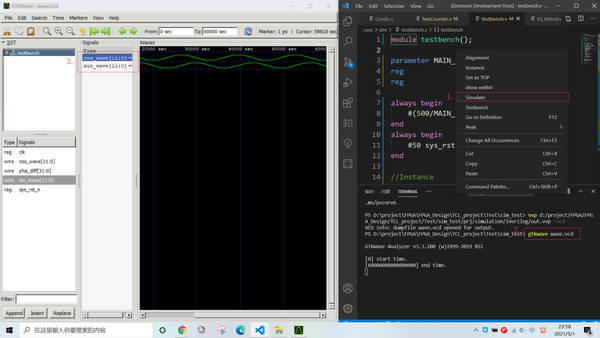

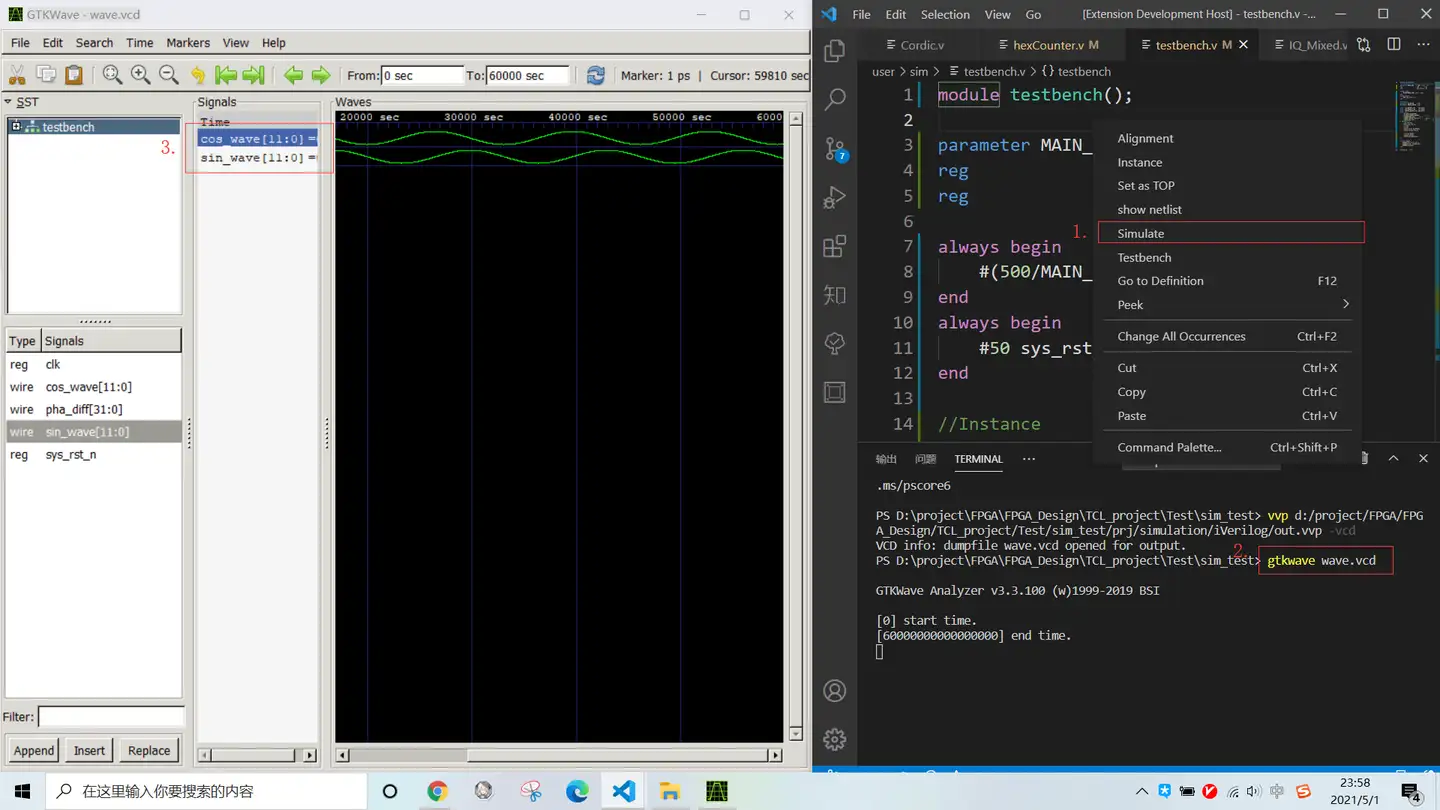

iverilog快速仿真

在0.1.18版本之后优化设计支持 include 设计

自带多文件仿真,无需 `include

支持xilinx仿真库

- 在setting中的 SIM.Xilinx.LIB.path 设置xilinx的安装路径

- 例:{xilinx安装路径}/Vivado/<版本号,例如18.3>/data/verilog/src

【注】:此功能需要iverilog和gtkwave均加入系统环境变量

modelsim快速仿真

Verilator快速仿真

常见功能库

IP_REPO

使用方式:

property.json文件中配置如下属性

"IP_REPO": [

"arm", // 包含ip CM3DbgAXI & DAPLink_to_Arty_shield

"adi" // 包含 adi 公司下所有器件ip,已去除所包含的绝对路径 取自 adi2019_r1

],

Extension HDL Lib

该扩展自带HDL功能库链接功能,在后端调用时,会自动加HDL库文件添加到后端工程中。

使用方式:

property.json文件中配置如下:

"HardwareLIB": {

"State": "virtual",

"Common" : [

"Math/Cordic.v",

"Math/Cordic.v"

// ...

],

"Customer" : [

"Relative path"

// ...

]

},

State 属性代表是加载到本地工作区还是作为远程进行链接。

virtual代表从远程虚拟包含,可以打开并更改,更改之后下次导入就是更改之后的代码。real代表将远程文件导入到该工程本地,放置到 HardwareSrc 下的lib中,此时更改不会影响库中的代码。- 【注】:当从 real 改回 virtual 时lib文件夹会被删除,请注意。

Common 属性代表插件自带的常见HDL功能库,该库的代码不太成熟,仅供参考。

【注】:当输入的是文件夹时则包含该文件夹下所有的文件。此外不建议直接更改该库中的代码,更改之后再在下一次插件更新之后会被重新覆盖,请慎重。目前已经经过仿真测试的lib路径如下

- Soc

- Math/Cordic.v

- Math/Sort3.v

- Math/Sqrt.v

- Malloc/RAM/Shift_RAM

- Apply/DSP/Advance/Communicate/Modulate

- Apply/DSP/Base/DDS

- Apply/Image (需要包含 Sort3, Sqrt, Shift_RAM)

Xilinx_lib 属性代表插件自带的Xilinx HDL功能库,主要是xilinx专用原语的调用,仅供参考。

【注】:当输入的是文件夹时则包含该文件夹下所有的文件。此外不建议直接更改该库中的代码,更改之后再在下一次插件更新之后会被重新覆盖,请慎重。目前已经经过测试的lib路径如下

- CLK/CLK_Global.v

Customer 属性代表用户自定义HDL功能库。

【注】:当输入的是文件夹时则包含该文件夹下所有的文件。该属性的使用需要对setting下的PRJ.customer.Lib.repo.path进行配置用户自定义库的根目录,在配置完成之后再在Customer 属性下配置相对路径,要求 PRJ.customer.Lib.repo.path/Customer 能够组成该文件(夹)的绝对路径。

以上功能在实际使用中由于缺少自动补全使用时确实有点麻烦,但json下好像不支持自动补全暂时还不知道原因。

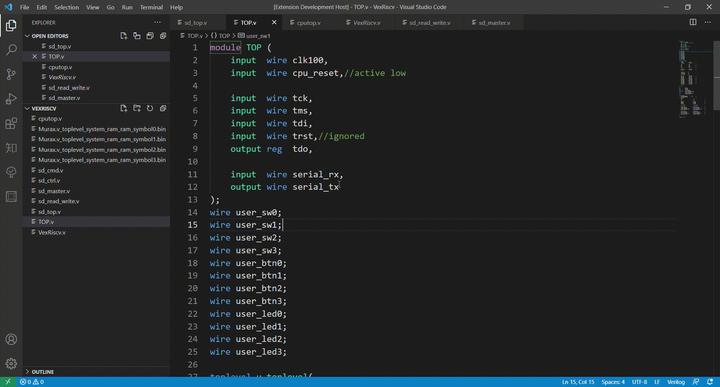

后端开发辅助功能

【注】:目前只支持在标准文件结构下的工程搭建。

启动方式

数字前端辅助功能是安装后即可使用,内置 Verilog 和 vhdl 的简单解析器,vhdl的支持后续有时间会完善。

数字后端辅助设计需要配置对应厂商的开发环境,相比于之前版本增加的功能不是很多,后期会继续补充。 现有支持vivado的辅助设计,使用方式如下:

步骤一:如果是新建工程则需要生成property文件,注明工程的相关配置

使用快捷键 ctrl+shfit+p/F1 打开命令框,输入 **generate property file** 来自动生成【注】: - 生成后进行配置,只有在保存后才会自动生成对应的文件结构。 - 通过使用快捷键 ctrl+shfit+p/F1 打开命令框,输入 overwrite 选择 Overwrite the InitPropertyParam 来改写默认的工程配置步骤二:启动方式如下:

使用快捷键 ctrl+shfit+p/F1 打开命令框,输入 launch 选择 **FPGA:Launch** 来启动使用快捷键 Alt+z 打开启动命令从功能框中点击FPGA OPTIONS下的 Launch

【注】:在设置Soc为非none时,文件结构会被更改,在文件结构更改的时候如果从有soc结构改回none,文件夹Software会被强制删除,如有重要文件请妥善保存!!!!!。

通用功能使用说明

Launch 功能,开启后端功能以 property.json 文件中配置的 TOOL_CHAIN 属性为准。目前只支持vivado。launch之后会根据 property.json 文件信息生成相应的工程。如果已经有工程的会直接打开vivado的gui界面。

- launch之后在HDL文件中右键选择 Set as Top 时会将该文件在vivado中设置为设计的顶层头文件。

- launch之后其他功能才会有效。

Simulate 功能,与在HDL文件中右键显示的simulate不同,该功能使用的是 property.json 文件中配置的 TOOL_CHAIN 属性所对应的仿真功能,即vivado自带仿真,而在其他地方打开的simulate则使用的是第三方仿真工具,用于对单个文件或者少量文件进行实时快速仿真。(目前仅iverilog)

- 在HDL文件中右键选择 Set as Testbench Top 时会将该文件设置为仿真的顶层头文件。

- 若仿真成功则会直接打开vivado的gui界面,显示仿真数据与波形。

- 若仿真失败则会在output栏输出错误日志。

Refresh 功能,更新xilinx工程下所包含的文件,因为包含的形式是全包含

- 包含的内容如下:

- 刷新

ip_repo_paths HardwareSrc与HardwareSim下的所有HDL文件HardwareSrc同级目录下bd和ip文件夹以及PRJ_Path中的所有 bd/ip 设计文件- lib远程链接的文件,即

HardwareLIB下配置的文件 (当HardwareLIB.State = "virtual") HardwareData下的约束文件

- 刷新

- 若单个增删某个文件只要将其在工作区下增删,扩展会自动添加到vivado中无需重新refresh

- 包含的内容如下:

Build 功能,完成综合,布局布线,你可以在 property.json 下的 enableShowlog 里选择是否将日志在终端中输出。

enableShowlog为true时只有当出现CRITICAL WARNING&ERROR时才会弹出output栏,并只输出错误与严重警告日志。- Build 功能下还细分 synth、impl、bitstream 这三个小阶段的功能。

Program 功能,一键下载。只是下载暂时不支持固化。

GUI 功能,如果需要IP设计,功能时序仿真或者bd设计时选择

GUI,之后就会自动打开图形界面。【注】:- 打开GUI后,打开对应工程的vscode,以及对应的

HardWare运行终端不能人为删除,删除后整个vivado的gui界面会自动关闭,若不保存则可能会导致设计丢失。 - 如果直接关闭vivado的gui界面或者删除*

HardWare* 运行终端则不会将PRJ_Path文件夹下的IP和bd设计文件移动HardwareSrc的同级目录下。虽然不会产生什么影响但分散的设计不方便管理,所以建议使用功能栏 FPGA OPTIONS 中的 Exit 进行退出。 - 功能栏 TOOL 中选择 Clean 时也会将工程中的IP和bd设计文件进行移动到

HardwareSrc的同级目录下,同时将整个工程进行删除。

- 打开GUI后,打开对应工程的vscode,以及对应的

【注】:SDK相关功能还不完善后续准备开放,用于替代xilinx的SDK,彻底解决xilinx SDK使用卡顿问题。

vivado开发辅助

由于目前只支持vivado的相关功能,因此对于vivado开发辅助见通用功能使用说明即可。 【注】:对于property.json文件中的 Device 属性目前已有的如下:

- xc7z020clg400-2

- xc7a35tftg256-1

- xc7a35tcsg324-1

- xc7z035ffg676-2

- xc7z020clg484-1

但支持的器件并不仅限于此,理论上可以支持vivado所能支持的所有器件,你可以直接将你的器件直接写在 Device 属性下,也可以将你的器件通过 FPGA:Add devices to the database 命令将其添加到数据库中,也可以通过 FPGA:Remove the device from the database 将其从数据库中删除。

quartus开发辅助

icestorm开发辅助

soc开发辅助

ZYNQ开发辅助

针对 Zynq 器件在新建工程时可以通过配置bd file来快速搭建想要的Zynq平台。具体 property.json 配置如下

"SOC_MODE": {

"soc": "ps7_cortexa9_0",

"bd_file": "zynq_default"

}

RISC开发辅助

Cortex-M开发辅助

调试开发辅助

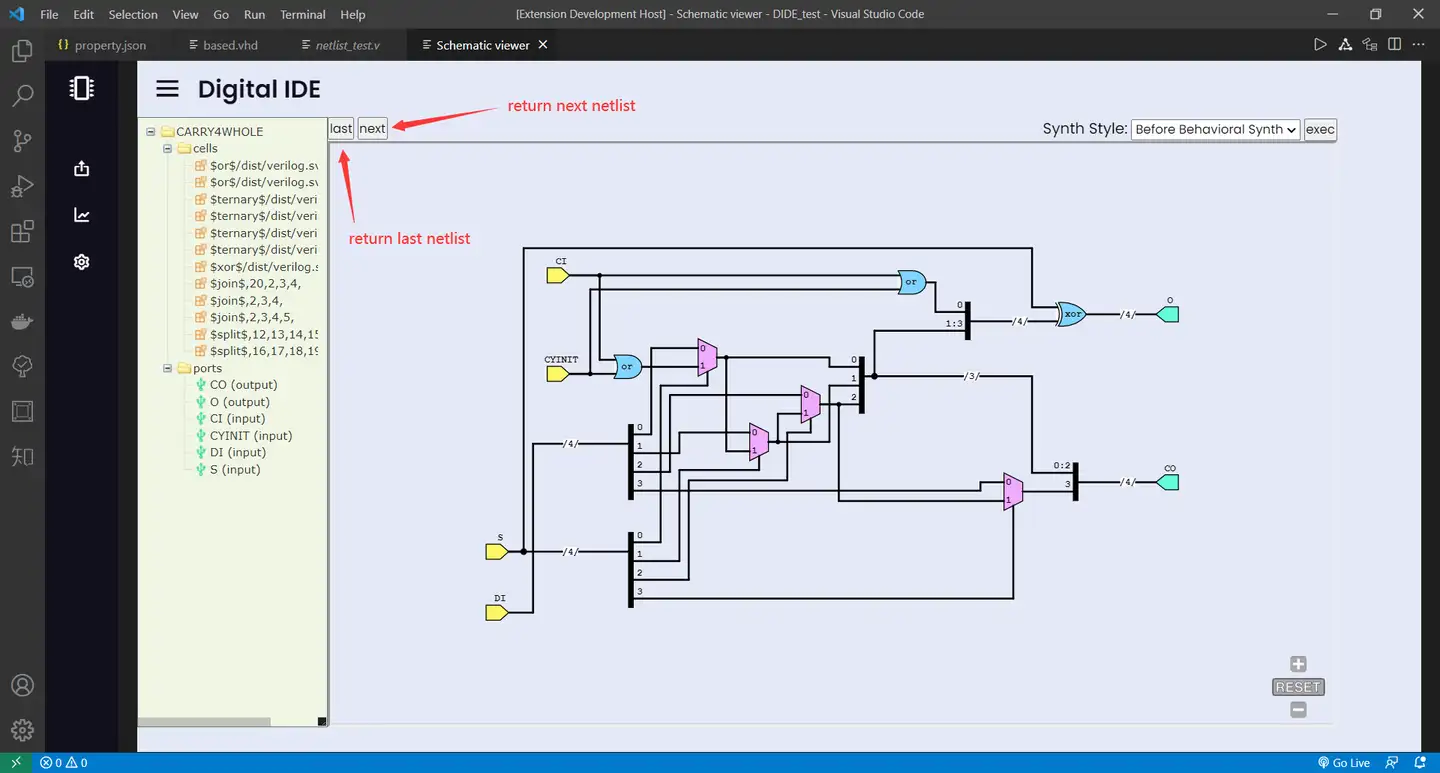

Schematic Viewer

插件使用 yosys 0.10 版本的内核(开源的yosysjs为0.5版本)进行指定工程的综合(可全平台运行),并展示综合后的网络图

该功能目前处于测试阶段,支持 include 以及多文件工程。

使用方式

- 点击右上角的图标进行面板的创建

- 或者在project structure中选择需要显示的模块,或者在文件中右击选择

show netlist

如何获取上述功能

只需两步即可具备大部分功能:

- step1:安装VScode

- step2:在VScode中安装Digital IDE插件

转载自:Digital IDE (FPGA Develop Support) 开发手册-version0.1.22

更详细的使用可以从链接中的原文或者git上找:

https://github.com/Bestduan/fpga_support_plug

智能推荐

关于UnityShader中的TRANSFER_SHADOW_CASTER_NORMALOFFSET内置宏-程序员宅基地

文章浏览阅读4.2k次,点赞4次,收藏10次。书上关于阴影部分虽然篇幅不多,但实际上有非常多的内容,尤其是相当多的宏与函数,而且官方文档也少得可怜,再翻下一章之前,我决定把这些用到的宏能弄明白的先弄明白,要不然就像狗熊掰棒子一样什么都落不下,在后续的博客中记录一下,当做笔记,如果有哪里说得有错误,还望批评指正。再UnityCG.cginc中可以找到TRANSFER_SHADOW_CASTER_NORMALOFFSET唯一的一处定义..._transfer_shadow_caster_normaloffset

Vue3+vite搭建基础架构(10)--- 使用less和vite-plugin-vue-setup-extend-程序员宅基地

文章浏览阅读1.5k次,点赞15次,收藏16次。这里记录下自己在Vue3+vite的项目使用less来写样式以及使用vite-plugin-vue-setup-extend直接定义组件name,不使用ts语法,方便以后直接使用。_vite-plugin-vue-setup-extend

ext4文件系统镜像制作_制作ext4镜像-程序员宅基地

文章浏览阅读267次。ext4文件系统镜像制作_制作ext4镜像

面试笔试---linux知识点_如何能够使用原先的ls命令-程序员宅基地

文章浏览阅读2.5k次。linux是一个开源、免费的操作系统,其稳定性、安全性、处理多并发已经得到业界的认可,目前很多中型,大型甚至是巨型项目都在使用linux。linux内核:redhat 、红旗linux、ubuntu、suse、fedora,它们的内核都是一样的(Note:linux其实是一个统称,就比如面条是一个统称,可以有哨子面、阳春面、打卤面等) linux的特点_如何能够使用原先的ls命令

matlab实时脚本使用_matlab实时脚本和脚本的区别-程序员宅基地

文章浏览阅读9.9k次,点赞4次,收藏39次。在本文中,我将介绍 MathWorks 在 MATLAB 软件中新增的一种交互式实时脚本文件——Live Script。下面首先认识什么是 Live Script ?什么是 Live Script ?Live Script 是 MATLAB Live Editor 应用程序输出的文件格式,在 Live Editor 交互式环境中,Live Script 可以包含 MATLAB 代码和输出结果(函数图像等),加上格式化文本、图片、超链接和 LaTeX 公式等元素,就可以成为一篇交互式叙述文本,用户可以用来分享_matlab实时脚本和脚本的区别

MRCTF 2020 Crypto writeup_ctf vigen猫re-程序员宅基地

文章浏览阅读2.5k次。MRCTF 2020 Crypto writeup_ctf vigen猫re

随便推点

新功能|Mail GPU Counter模块新增GPU图元处理和GPU Shader Cycles_uwa 捕获gpu元数据原理-程序员宅基地

文章浏览阅读550次。GPU检测分析又添Buff_uwa 捕获gpu元数据原理

webform计算某几列结果_1+x 证书 Web 前端开发初级实操考试(试卷5 )-程序员宅基地

文章浏览阅读3.4k次。本文编写于 439 天前,最后修改于 366 天前,其中某些信息可能已经过时。Web前端开发初级模拟测试卷(五)PDF版点击查看共55道题 总分:200分一、单选题共30题,60分1.在弹性盒子中,以下不属于justify-content的值是()DA flex-startB centerC space-betweenD end2.alt和title属性的特点表述正确的是()BA 不同的..._在javascript中,把字符串“789”转换为整型值789的正确方法是()avar str="789

Ubuntu软件包管理工具_请先确保软件包管理工具可用-程序员宅基地

文章浏览阅读2.8k次。本文详细的介绍了在Ubuntu/Debian下如何管理软件包。主要介绍了apt-get, apt-cache, apt-file, apt-key命令的用法。_请先确保软件包管理工具可用

wordpress手动升级为最新版本最稳妥的办法_wordpress模板升级-程序员宅基地

文章浏览阅读1.5k次。升级之前先备份,包括数据库和程序,这个是必备程序,以防出错,升级有风险,备份是必须。第一步、下载最新的WordPress安装包官网下载地址:https://cn.wordpress.org/latest-zh_CN.zip小技巧,官网下载比较慢,可以使用迅雷下载,尝试过很快。下载后,解压。第二步、替换原网站目录中的文件1、先将除了 wp-content 目录下,和 wp-config.php 配置文件的文件全部替换掉。2、将wp-content目录下除了 uploads、themes和 p._wordpress模板升级

UnicodeDecodeError: 'gbk' codec can't decode byte 0xe9 in position 7581: illegal multibyte sequence-程序员宅基地

文章浏览阅读3.2k次,点赞11次,收藏10次。 这个问题是在我在读取一段文本时出现的错误,当时的代码是这样的: def getMovieList(item): items = {} f = open(item,"r") #这句的问题 movie_content = f.readlines() f.close() for movie in movie_content: mo..._gbk' codec can't decode byte 0xe9 in position 7581: illegal multibyte s

[STM32U5]【NUCLEO-U5A5ZJ-Q测评】高速USB-程序员宅基地

文章浏览阅读13次。1、STM32U5 Series系列有几个型号内部嵌入了 USB OTG 高速设备/主机/OTG 外设,并集成了收发器,.这些型号包括STM32U59x/5Ax/5Fx/5Gx。如果要使用高速USB,必须确保内部的USB PHY PLL产生精确的60MHz时钟。可以看到数据发送比较稳定,测试发现我的电脑串口来不及接收更快的数据和更大的数据包。内部嵌入高速USB PHY可以省掉了使用外部高速USB外设带来的麻烦,这样对有高速数据传输需求的项目带来更多的便利。USB协议栈使用USBX。来源:21ic.com。