2022东北大学软件学院计算机组成原理实验报告(七段数码管+乘法器+单周期CPU)_东北大学计算机组成原理实验报告七段数码管-程序员宅基地

东北大学软件学院计算机组成原理实验报告:总共有3个实验:1.七段数码管 2.乘法器 3.单周期CPU 。这门课最终得分94。

一.实验目的

1. 组合逻辑设计实验目的:

(1). 学习Logisim数字逻辑电路设计和模拟仿真平台的使用;

(2). 掌握组合逻辑电路的设计方法;

(3). 掌握带有无关项的数字逻辑电路化简方法;

(4). 掌握七段数码管的工作原理;

(5). 设计七段数码管译码电路,并且进行仿真测试。

2. 时序逻辑设计实验目的:

(1). 掌握使用FSM进行时序逻辑电路设计的总体流程;

(2). 理解Moore型有限状态机和Mealy型有限状态机的不同;

(3). 理解并掌握两种状态编码方式(二进制编码和独热编码);

3.单周期CPU设计实验目的:

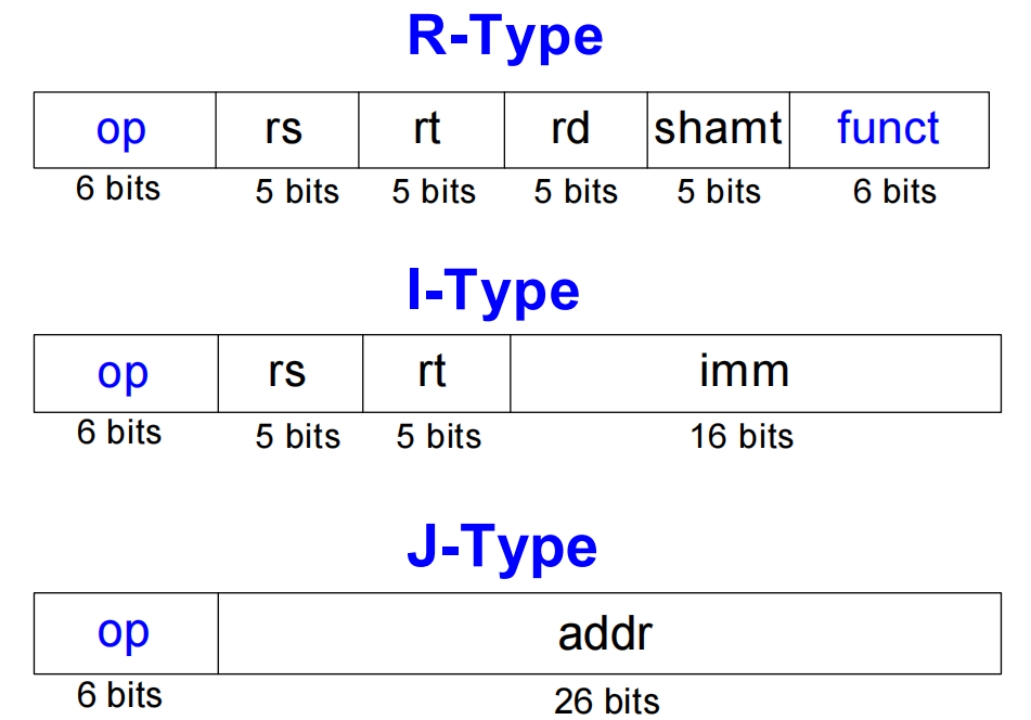

(1). 掌握MIPS体系结构,指令系统;

(2). 掌握MIPS机器指令三种类型指令的结构;

(3). 理解并掌握三种类型指令的执行过程;

(4). 掌握MIPS存储组件(寄存器,ROM,RAM)的工作原理;

(5). 掌握单周期MIPS CPU设计原理。

二.实验内容

1.1 七段数码管译码电路的设计需求

(1). 正确理解和区分逻辑函数中的无关项、约束项和任意项这三个基本概念,合理地运用无关项进行逻辑化简;

(2). 使用模拟逻辑电路的图形化工具Logisim;

(3). 设计的译码电路是一个独立的子电路,并进行封装及外观设计。

1.2 设计的目标内容

(1). 设计可正常显示0-9的实验电路;

(2). 设计可正常显示0-9,大于9显示字母“E”的实验电路;

(3). 设计可正常显示0-F的实验电路;

(4). 设计可正常显示0-F(数字和字母)并有极性控制的实验电路;

(5). 设计七段数码管译码电路的测试电路,该测试电路可使用拨码开关作为测试输入源,七段数码管模块作为测试输出。

2.时序逻辑设计

2.1 时序逻辑设计的设计需求

(1). 了解掌握有限状态机的基本原理,能够选择Moore型或Mealy型有限状态机设计乘法器;

(2). 深入了解乘法器设计的原理;

(3). 输入和输出的结果能够以十进制显示,并且能够正确显示结果;

2.2 设计的目标内容

(1). 可设计8位*8位,结果16位的基本乘法电路和控制器并能够正确计算和显示结果,电路设计美观,封装合理;

(2). 设计快速乘法器;

(3). 对基本乘法器和快速乘法器测试电路。

3.单周期CPU设计

3.1 单周期CPU的设计需求

(1). 设计一个MIPS体系结构的CPU,该CPU能够执行R类型、lw、sw、beq和bne类型的指令;

(2). 该CPU能够实现测试的用例,并且输出正确结果。

3.2 设计的目标内容

(1). 设计构建CPU所必要的组件,包括ALU、ROM、RAM,寄存器文件,电路设计美观,封装合理;

(2). 设计并实现MIPS单周期CPU数据通路和控制器,能够设计测试用例进行有效测试。

三.实验环境

-

七段数码管译码电路实验中使用的logisim库有:线路、逻辑门、存储库和输入输出。

-

乘法器设计的实验中使用的logisim库有:线路、逻辑门、存储库、复用器、运算器和输入输出。

-

单周期CPU实验中使用的logisim库有:线路、逻辑门、存储库、复用器、运算器和输入输出。

四.实验过程

1.组合逻辑设计

1.1 七段数码管译码电路的设计思路

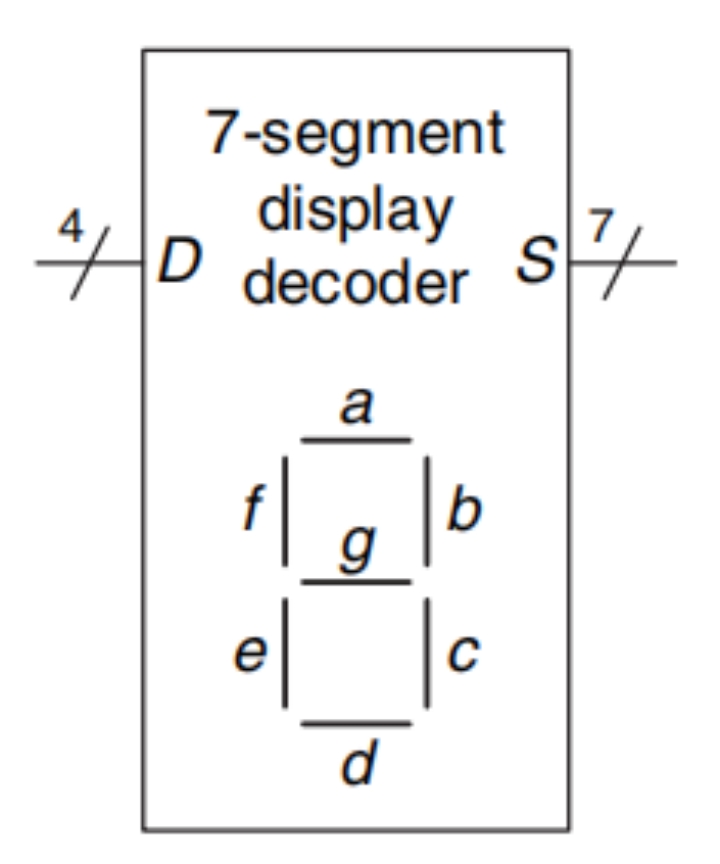

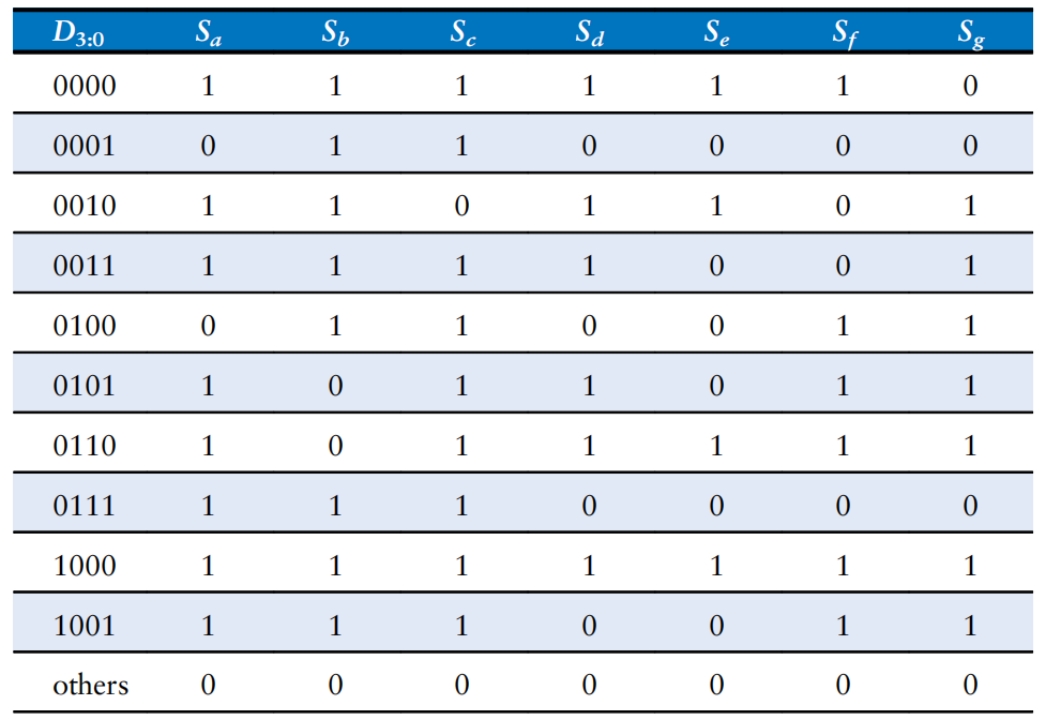

七段数码管显示译码器通过4位数据的输入,产生7位输出以控制发光二极管来显示数字0到9,这7位输出我们称为段a到段g。

图 1 七段数码管显示译码器电路符号

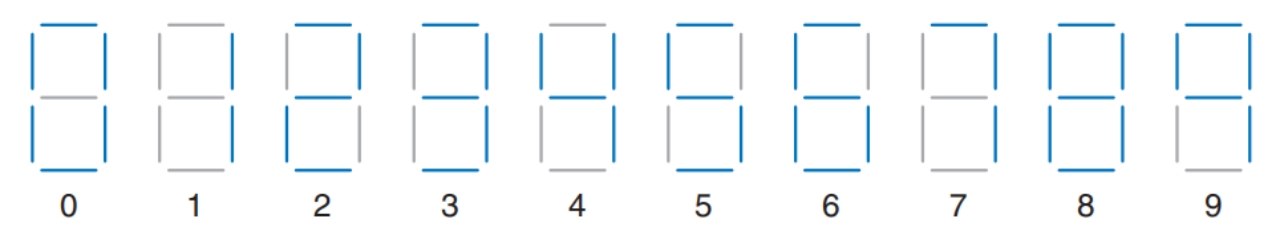

图 2 七段数码管显示的数字

图 3 七段数码管显示译码器真值表

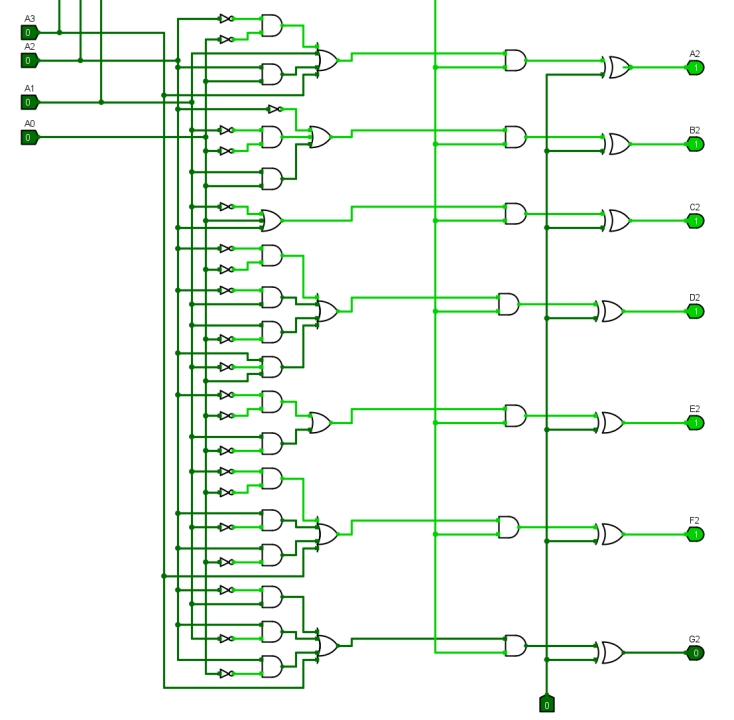

1.2 设计方案

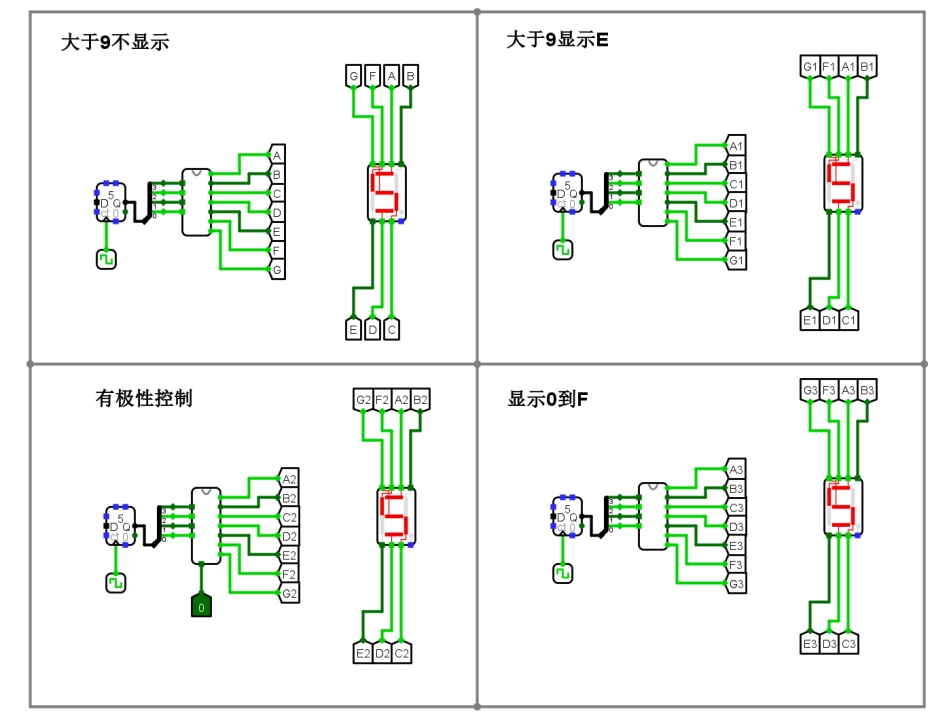

我总共设计了四种类型的方案,分别是只显示0到9且大于9不显示的电路、显示0到9且大于9显示E的电路、显示0到F的电路和显示0到F且有极性控制的电路。在这四种方案中,我认为显示0到F且有极性控制的电路最具有创新性。有极性控制能够扩大七段数码管的通用性,做到能共阳极或共阴极。

1.3 创新点

创新点是实现显示0到F且有极性控制的译码器。为了能够实现10到15显示字母,在原来的基础上,我多加考虑了1010到1111的真值表。为了实现极性的控制,在原来的输出结果加上了异或门逻辑。

图 4 七段数码管有极性控制的电路

2.时序逻辑设计

2.1 乘法器的设计思路

(1). 乘法器的原理

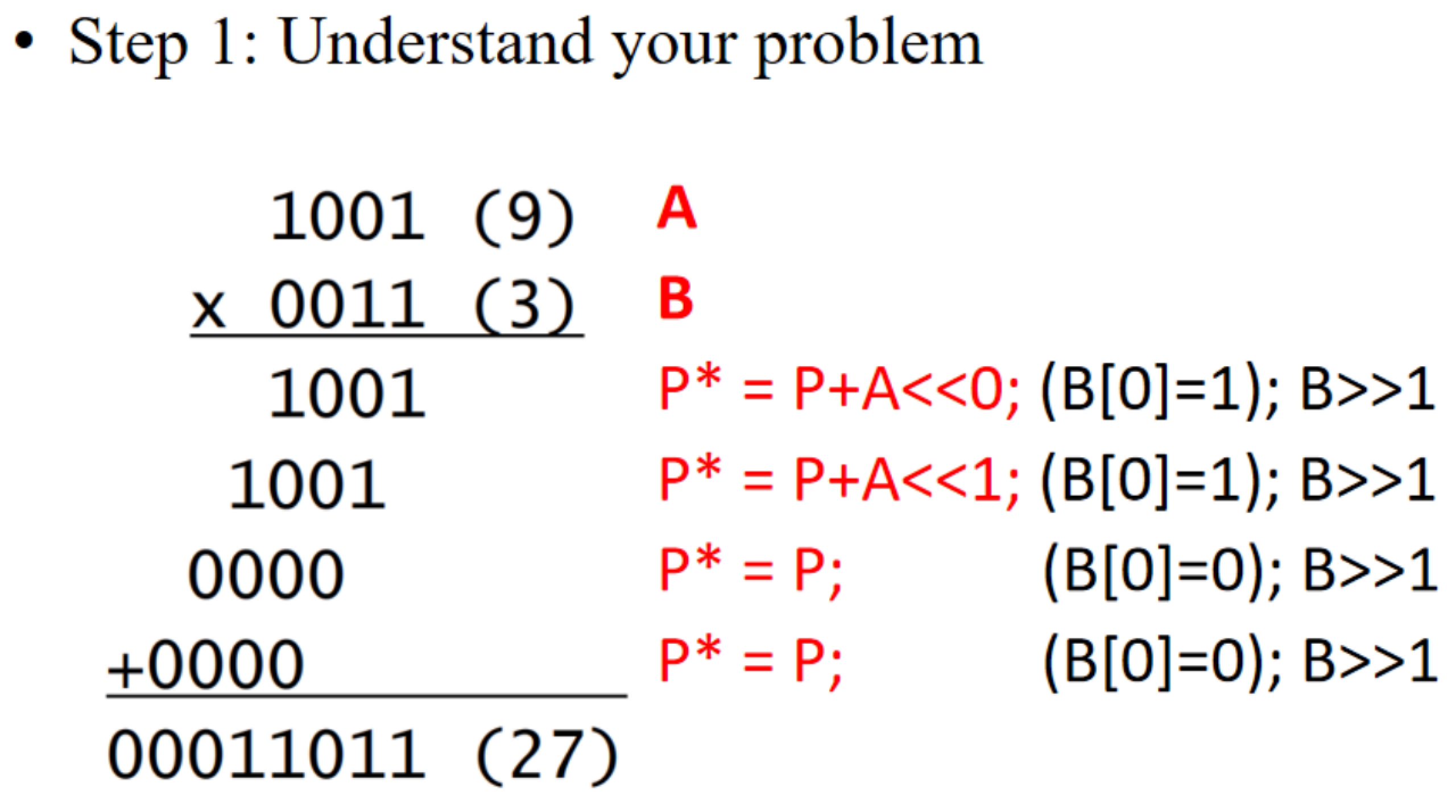

在设计乘法器之前,我们要理解乘法器的原理。在做乘法运算时,分为乘数和被乘数。我们记被乘数为A,乘数为B。乘法的计算过程如下图所示:

图 5 乘法的计算过程

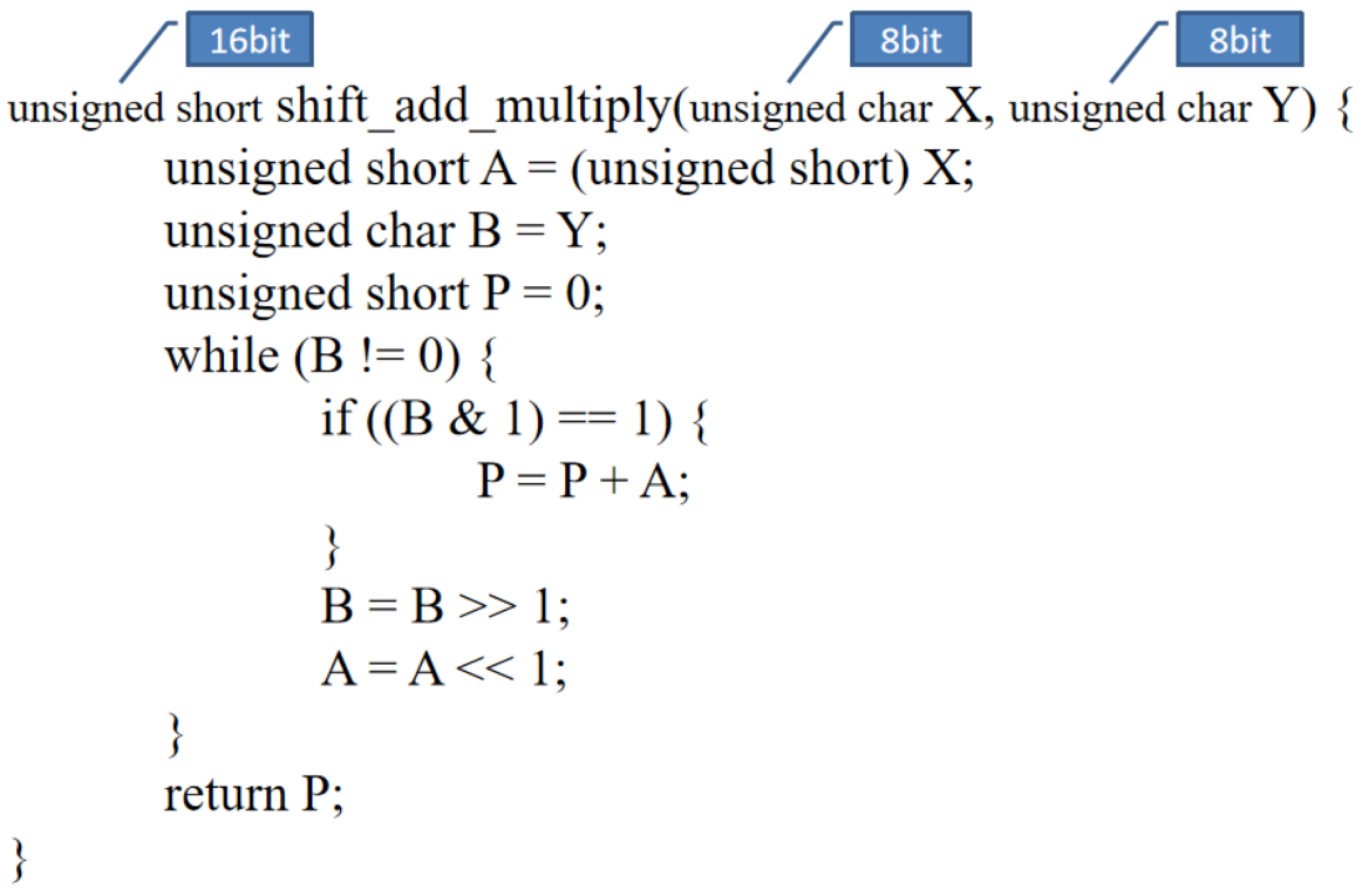

我们记乘数的每一位相乘后得到的结果为P,在乘法运算中,需要判断乘数是否为0,若乘数不是0,则进一步判断乘数的最低位是否为0,如果最低位是0,则P还是原来的结果,如果最低位是1,则P等于P加上A左移一位后的结果。我们可以用C语言代码的形式表示出乘法运算的整个流程。

图 6 乘法器C语言代码

(2). 修改变量的状态

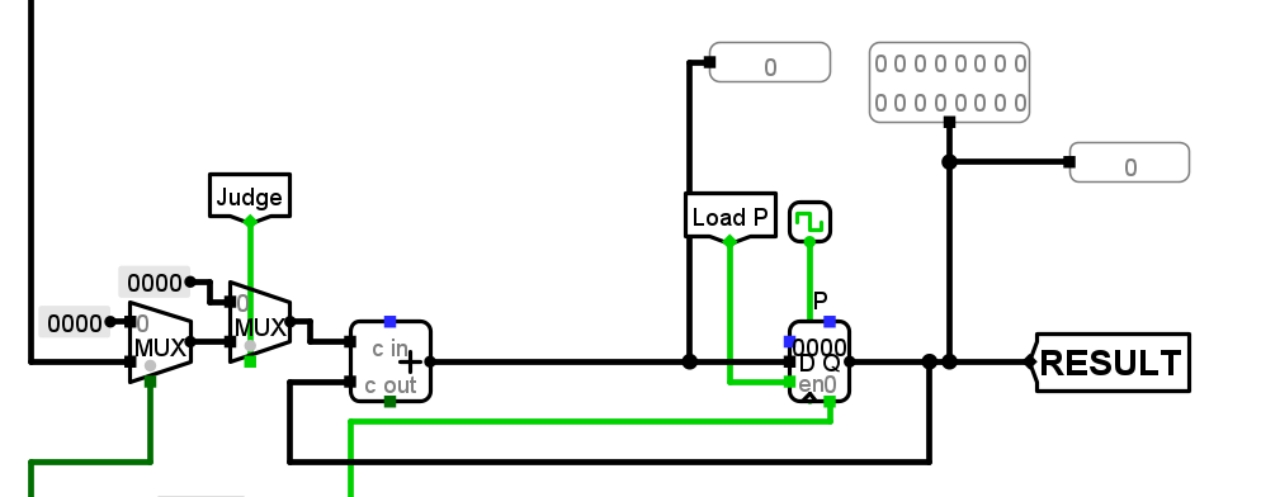

对于变量的修改,我们需要在电路图中实现。对于“P*=P+A”,我们在开始的时候给P赋值为0, 当进行第一步运算时,且最低位为1,那么P*的值就等于0加A,其实就是等于A。我使用了多路选择器,其中的Jugdge信号是根据判断乘数Y的最低位是否为0得到的,Load P也是根据判断乘数Y的最低位是否为0得到的。我分析得到,当乘数的最低位是0时,Load P和judge都为0;当乘数的最低位是1时,Load P和judge为1。

| B[0] | jugdge | Load P |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 1 | 1 |

表 1 judge和Load P的真值表

图 7 实现P*=P+A

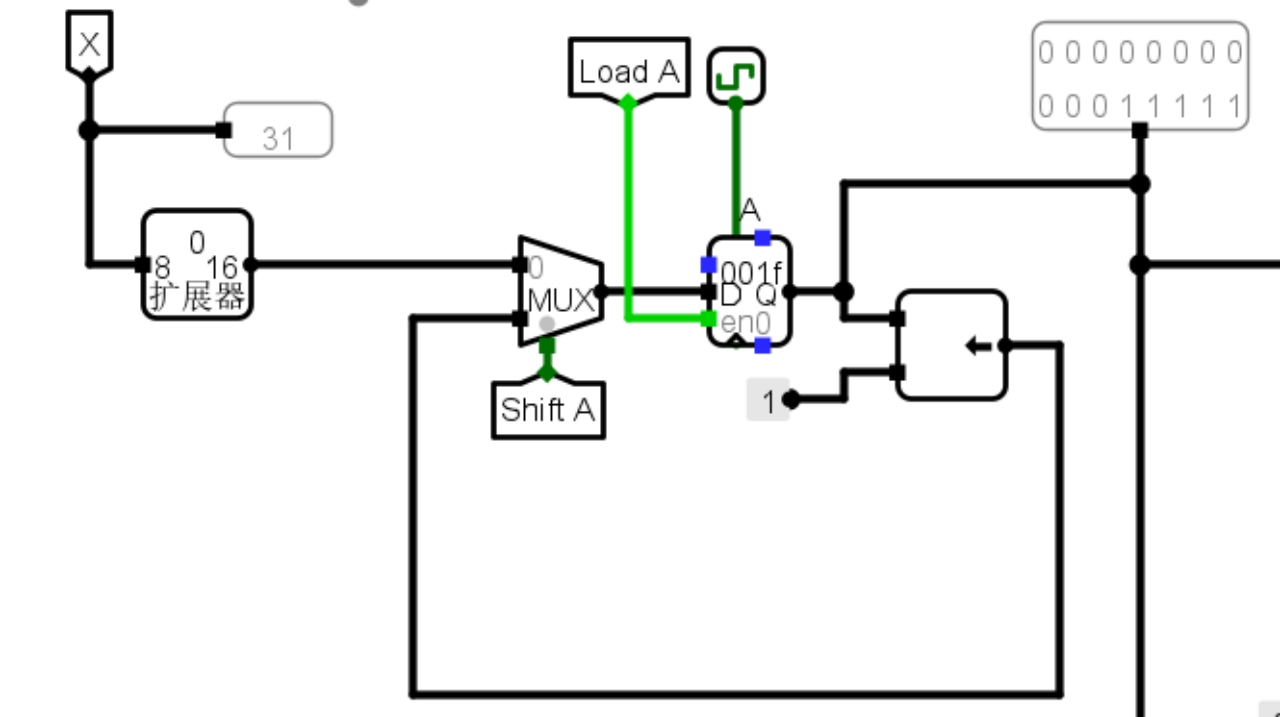

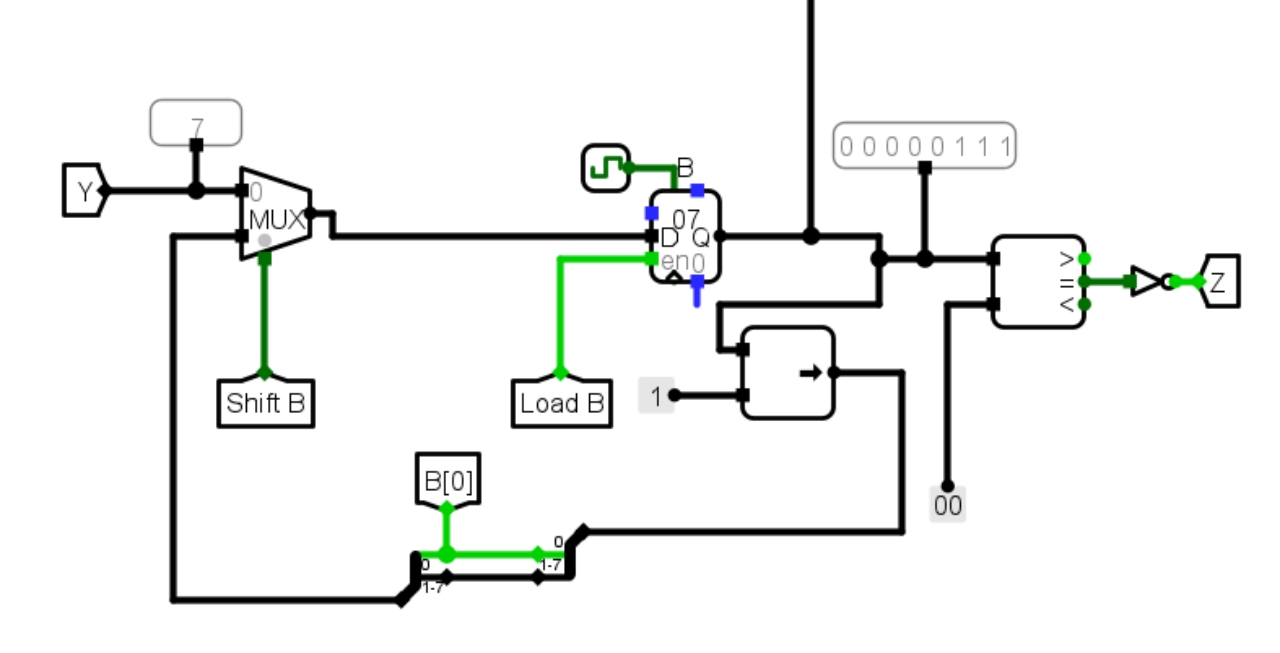

对于“B = B >> 1”和“A = A << 1”,我使用的是移位器来实现。在电路实现中我增加了Shift A和Shift B这两个信号,用来控制多路选择器,在最开始时,选择的是第0路,之后才会选择第1路,也就是移位后的A和B。

图 8 实现A = A << 1

图 9 实现B = B >> 1

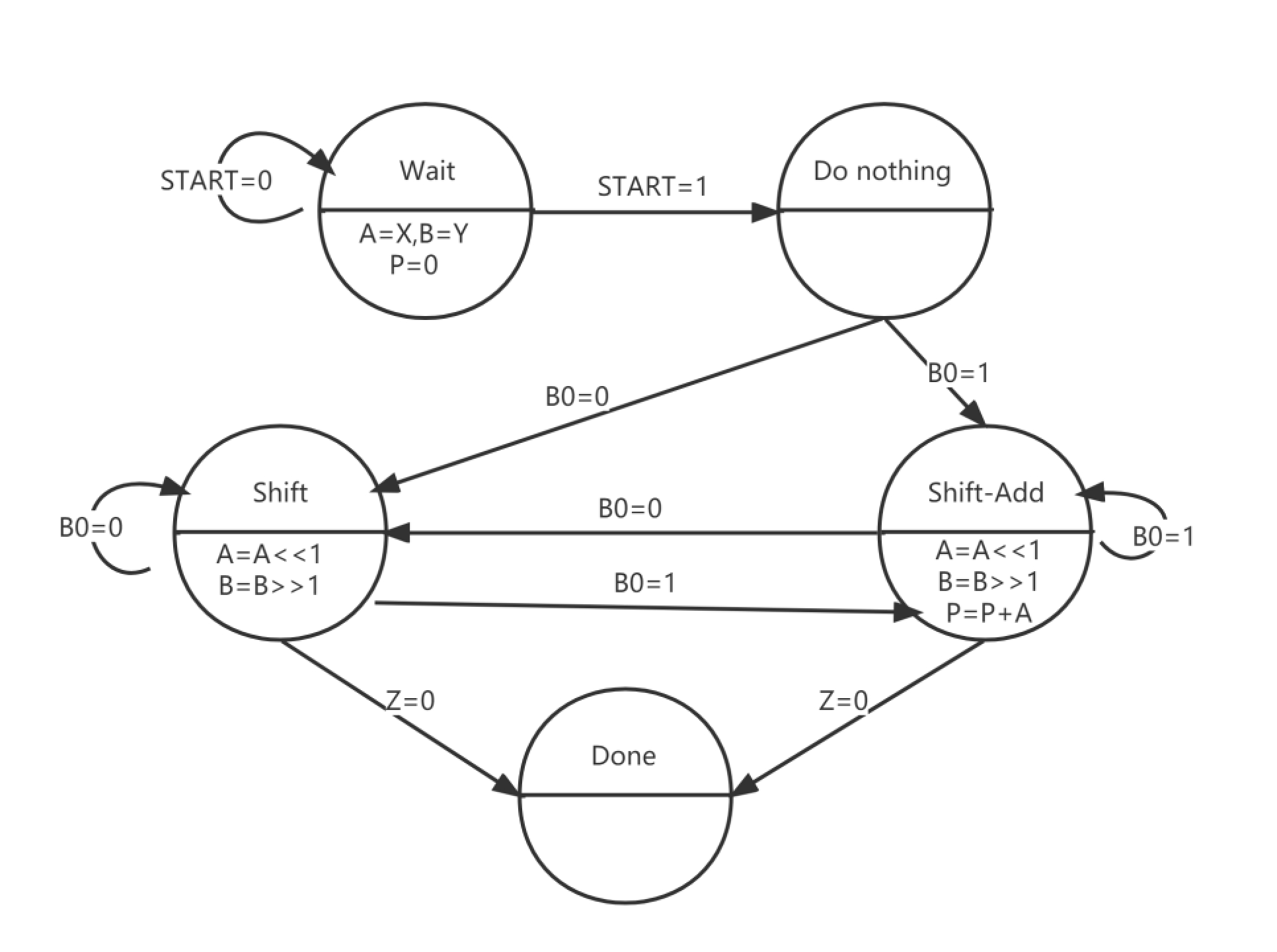

(3). 使用有限状态机实现乘法器的控制器

我设计的有限状态机中总共有5个状态,采用二进制编码的状态编码方式,我给这些状态分别记为000、001、010、011和100。

| 状态名称 | 二进制编码 | ||

|---|---|---|---|

| S2 | S1 | S0 | |

| Wait | 0 | 0 | 0 |

| Do nothing | 0 | 0 | 1 |

| Shift | 0 | 1 | 0 |

| Shift-Add | 0 | 1 | 1 |

| Done | 1 | 0 | 0 |

表 2 五种状态的二进制编码

可选择的状态机类型有Moore型和Mealy型,我使用的是Moore型的状态机,输出只取决于系统的状态。

| 当前状态****S2 S1 S0 | LA | SA | LB | SB | LP |

|---|---|---|---|---|---|

| 000 | 1 | 0 | 1 | 0 | 1 |

| 001 | 0 | 0 | 0 | 0 | 0 |

| 010 | 1 | 1 | 1 | 1 | 0 |

| 011 | 1 | 1 | 1 | 1 | 1 |

| 100 | 0 | 0 | 0 | 0 | 0 |

表 3 Moore型有限状态机输出表

| 当前状态S2 S1 S0 | 输入START | 输入B0 | 输入Z | 下一状态S2 S1 S`0 |

|---|---|---|---|---|

| 000 | 1 | 001 | ||

| 001 | 1 | 0 | 1 | 010 |

| 001 | 1 | 1 | 1 | 011 |

| 010 | 1 | 0 | 1 | 010 |

| 010 | 1 | 1 | 1 | 011 |

| 010 | 1 | 0 | 0 | 100 |

| 011 | 1 | 0 | 1 | 010 |

| 011 | 1 | 1 | 1 | 011 |

| 011 | 1 | 0 | 0 | 100 |

表 4 状态转移表

图 10 状态转换图

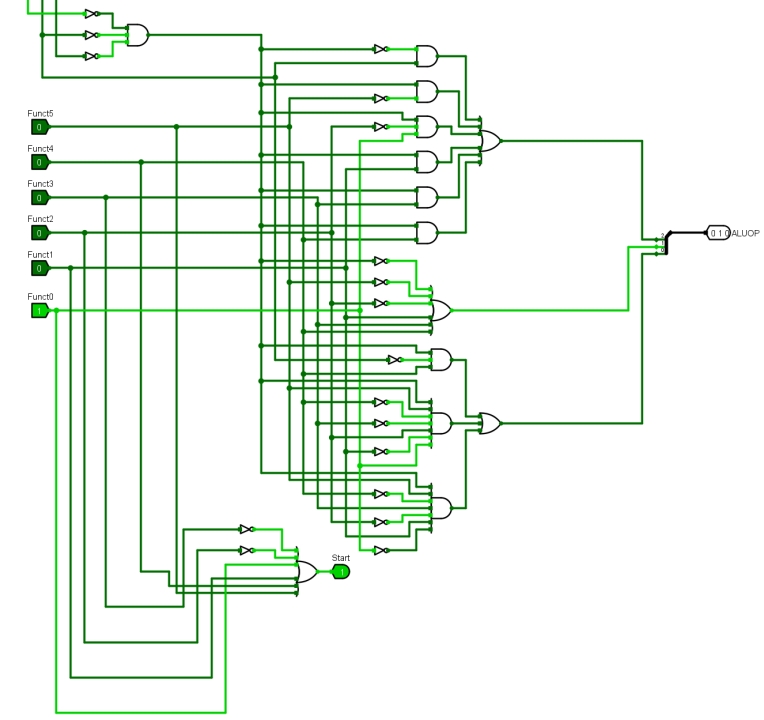

图 11 有限状态机电路图

2.2 设计方案

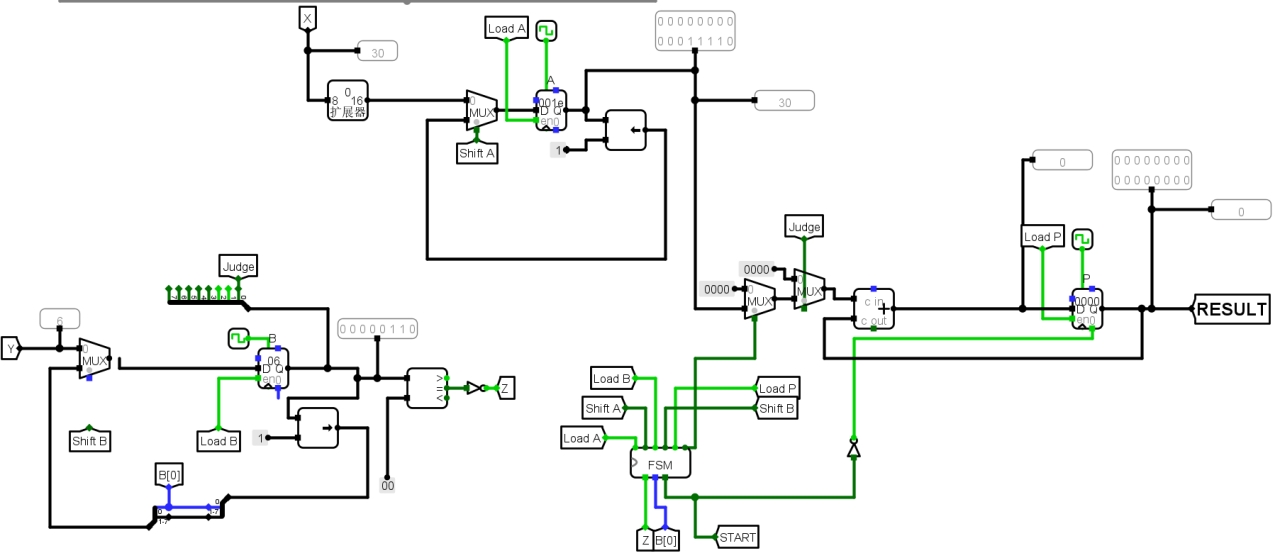

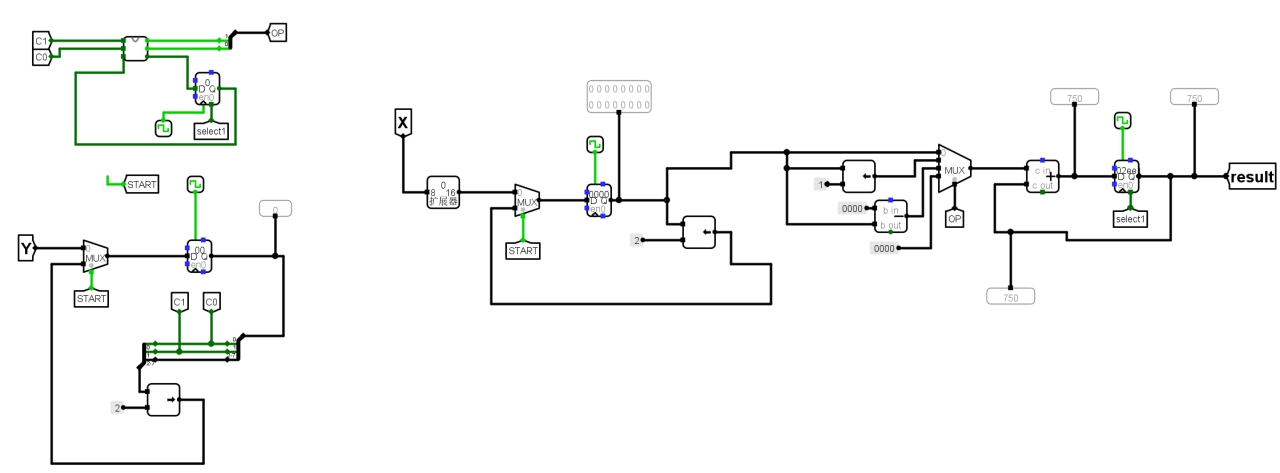

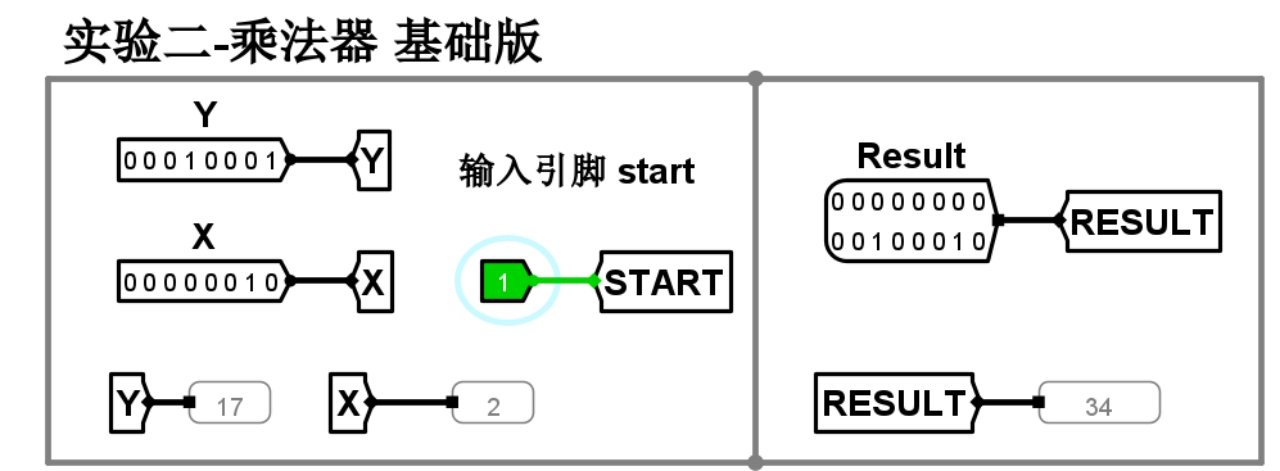

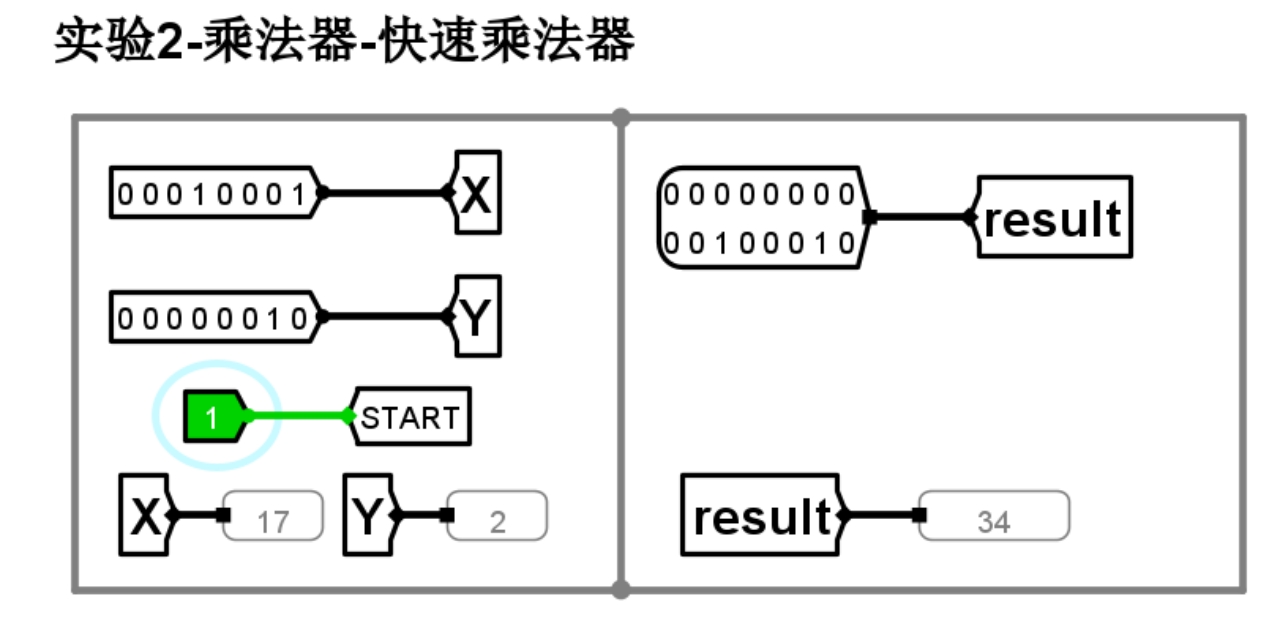

总共有两种设计方案,分别设计了的8位*8位,结果16位的基本乘法电路和moore型的控制器和快速乘法器。

图 12 基本乘法电路

2.3 创新点

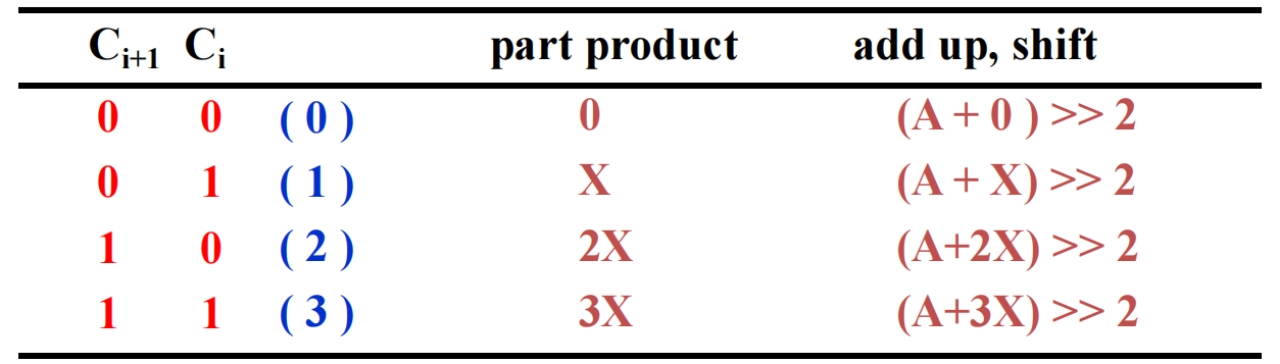

设计了快速乘法器,与基础版的乘法器不同的是,快速乘法器每一次运算的是两位(第0位和第1位),从而达到快速乘法的目的,提高计算的效率。

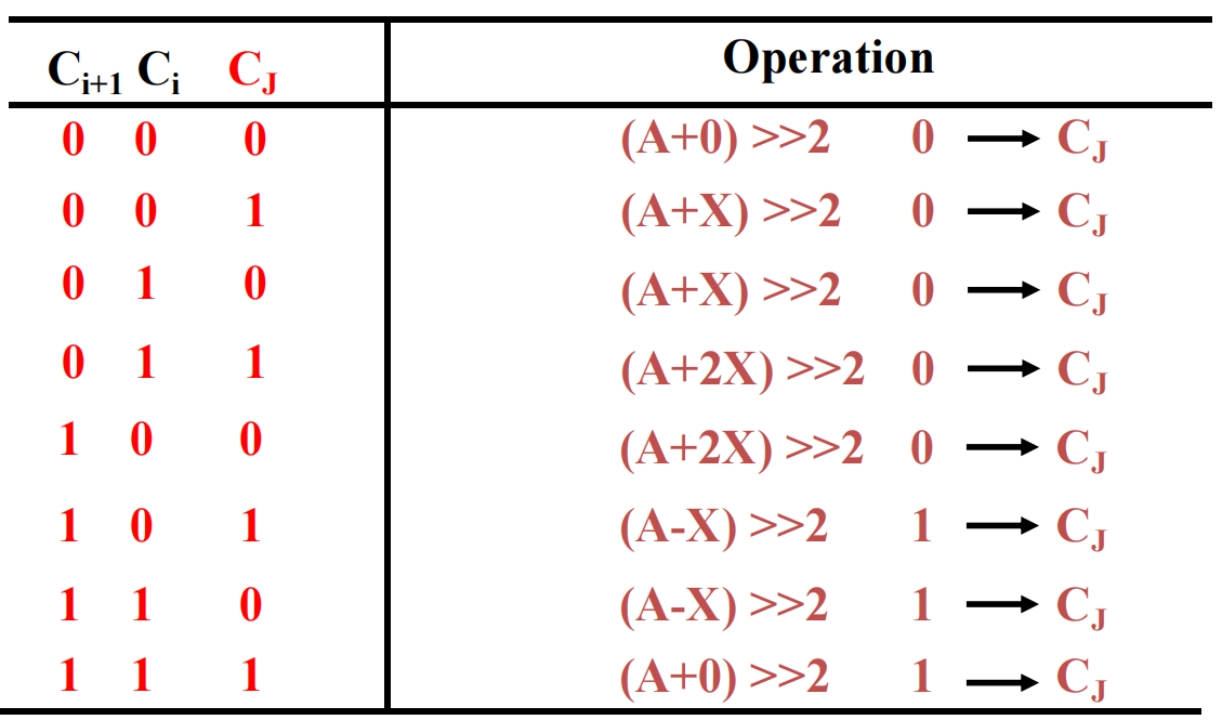

其中的A+3X是当成(A-X)+4X,这就需要引入CJ,CJ用来标记是否欠账,如果欠账了,则需要在下一步进行+X操作。

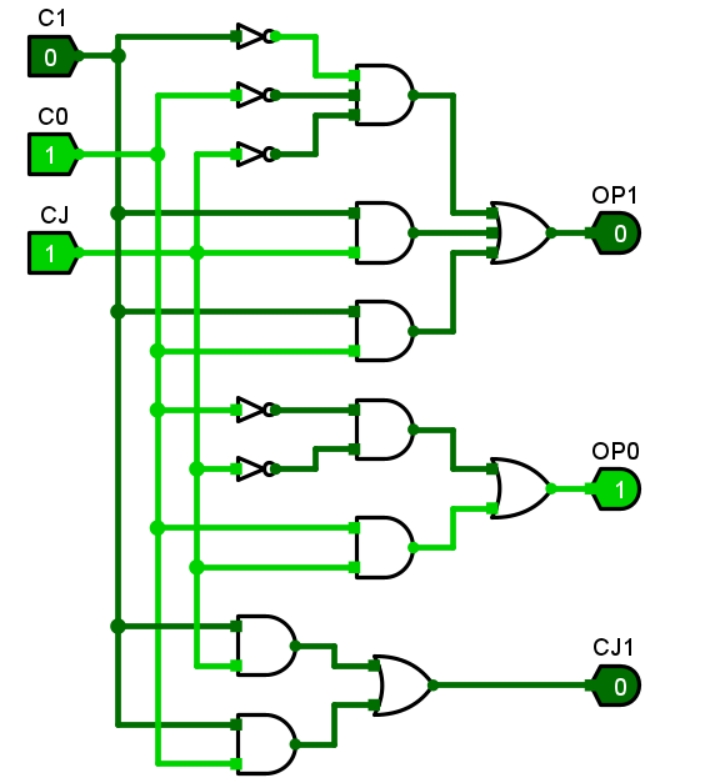

对于4中操作,我把它们看成是4种状态,用二进制编码表示出这4种状态。

| 操作 | OP1 | OP0 |

|---|---|---|

| **(A+**X) >>2 | 0 | 0 |

| (A+2X) >>2 | 0 | 1 |

| (A-X) >>2 | 1 | 0 |

| (A+0) >>2 | 1 | 1 |

图 13 四种状态的二进制编码

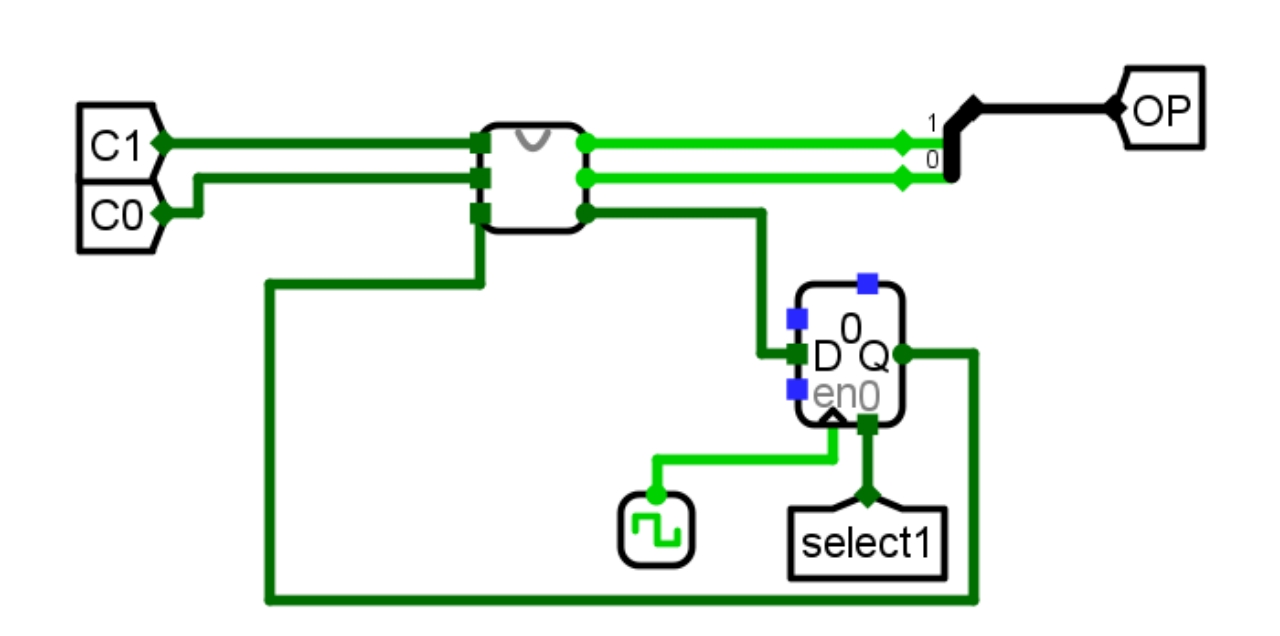

针对CJ,共有两种可能的情况,并且CJ的值与当前的最低两位相关,为此我设计了有限状态机。

图 14 有限状态机状态转移表

图 15 有限状态机电路图1

图 16 有限状态机电路图2

图 17 快速乘法器电路图

3.单周期CPU设计

3.1 设计所需组件

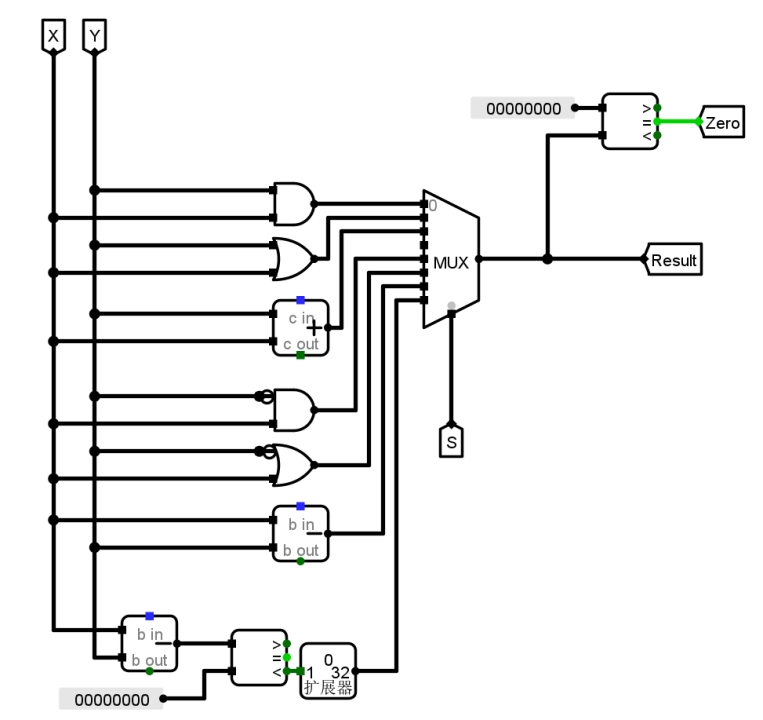

(1). ALU的设计

设计的ALU共有6种功能,并且有Zero信号用来表示最终的结果是否为0。设计的思想是3位的ALUOP作为多路选择器的选择信号,从而控制哪一路输出。

| ALUOP | 功能 |

|---|---|

| 000 | X AND Y |

| 001 | X OR Y |

| 010 | X + Y |

| 011 | 未使用 |

| 100 | X AND Y’ |

| 101 | X OR Y’ |

| 110 | X - Y |

| 111 | SLT |

图 18 ALU的功能

图 19 ALU设计电路

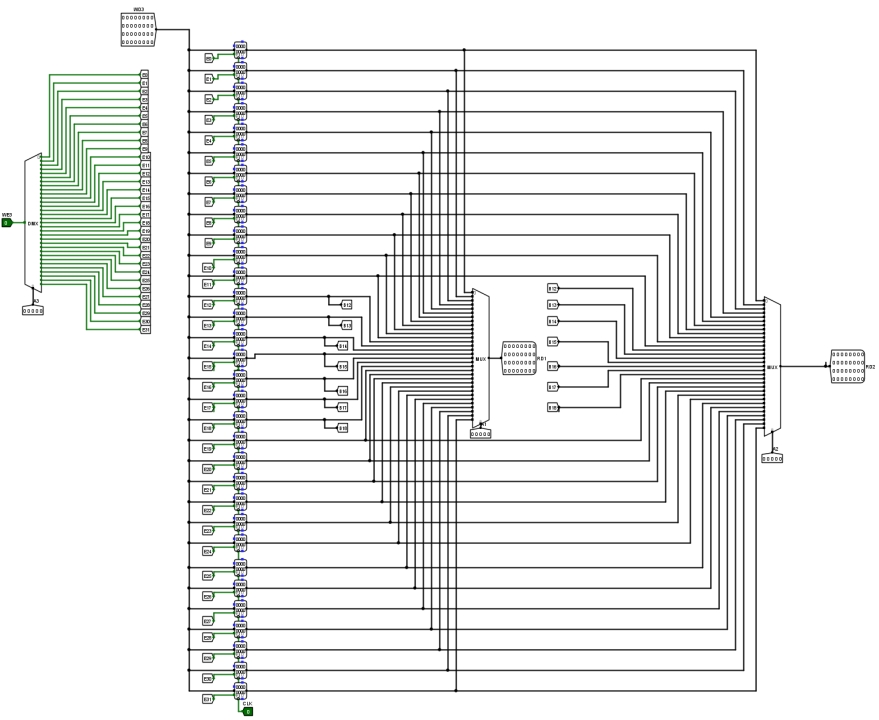

(2).寄存器文件的设计

设计了有一个写地址端口、一个写数据端口、一个写使能端口、两个读数据端口、两个读地址端口的寄存器文件,其中的数据端口的数据位宽是32位,地址端口的数据位宽是5位,设计的思想是把32个寄存器并行,通过多路选择器对输出的数据的寄存器选择,通过解复用器对需要写入的的寄存器选择。

图 20 寄存器文件设计电路

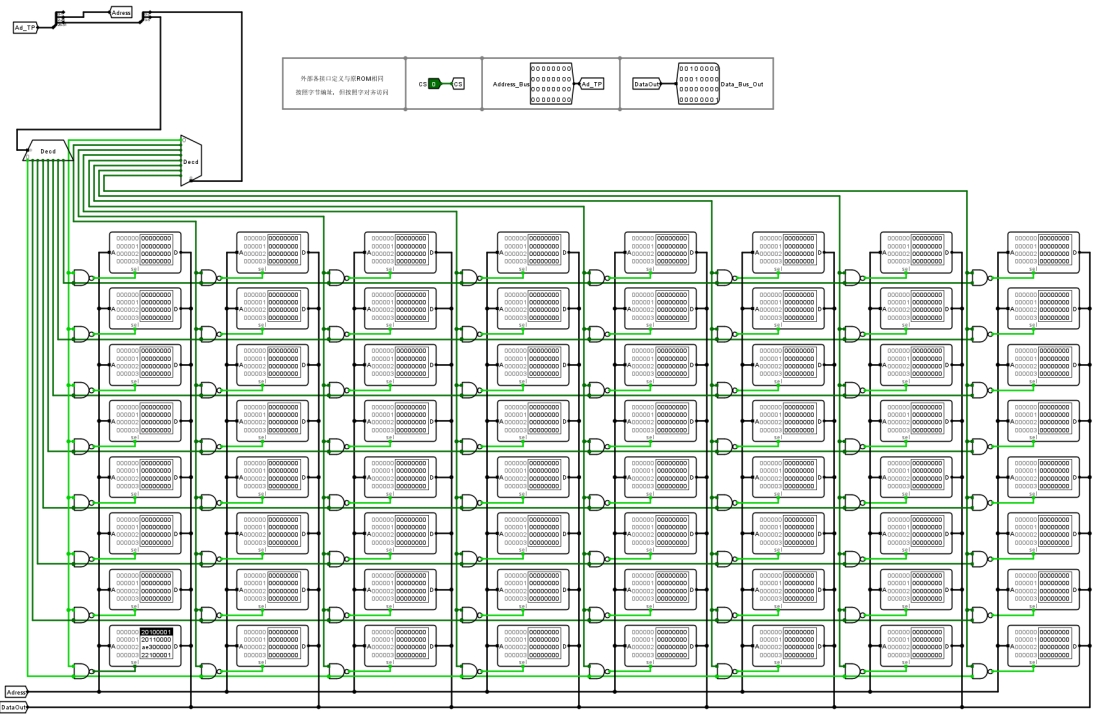

(3).Rom存储阵列的设计

Rom存储器是用来当指令存储器,程序计数器(PC)中包含当前执行指令的地址,第一步则需要从指令存储器中读取指令。我设计的Rom存储阵列由64个Rom组成,指令地址的最高6位构成存储阵列的片选逻辑。

图 21 Rom存储阵列电路

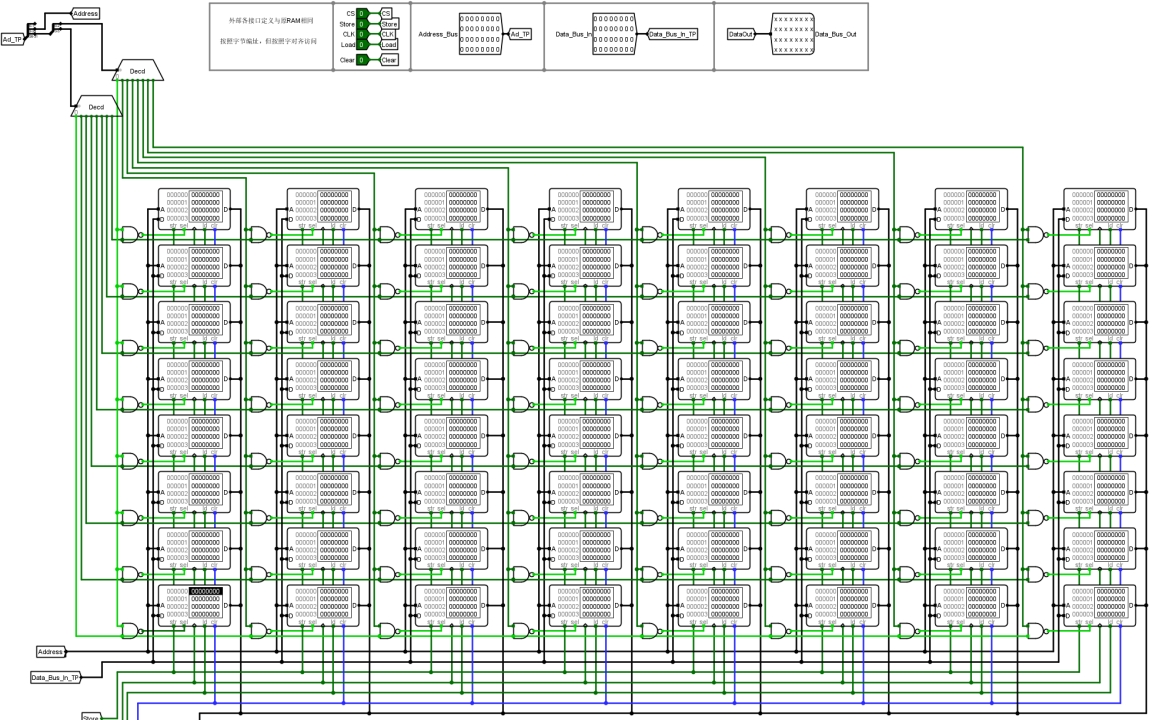

(4).Ram存储阵列的设计

Ram存储器用来当做数据存储器。对于读出指令,ALU的计算结果将连接到数据存储器的地址。从数据存储器中读取的数据将出现在RD上,并在时钟周期结束时写入到寄存器文件中的目的寄存器。我设计的Rom存储阵列由64个rom存储器组成,通过地址的高6位进行片选。

图 22 Ram存储阵列电路

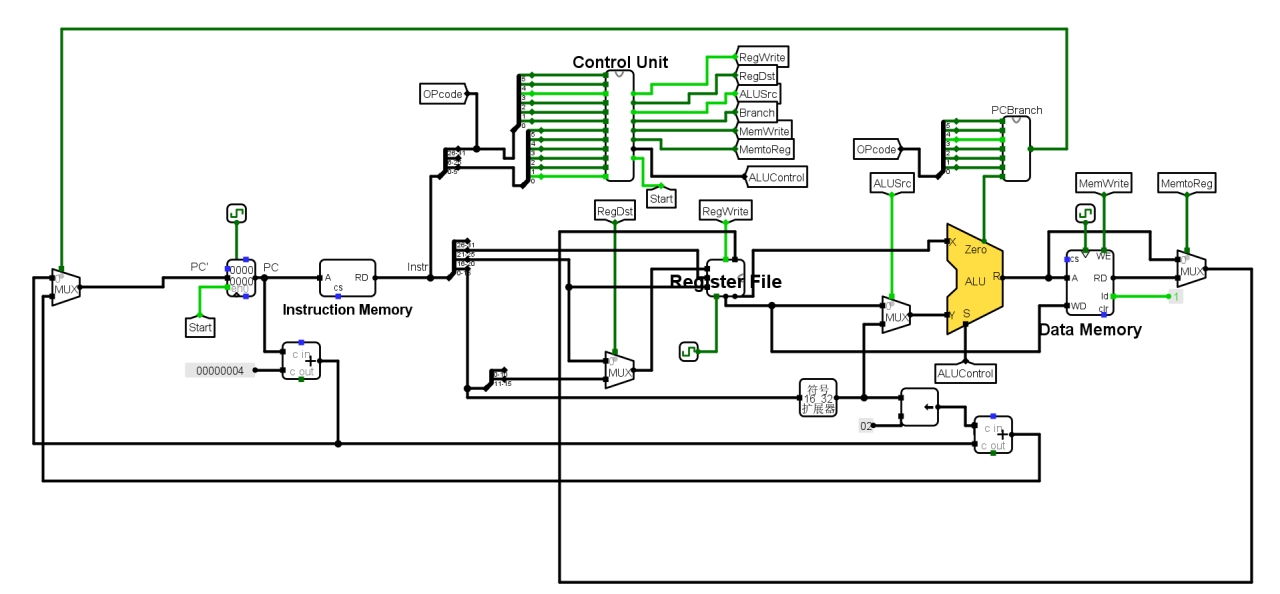

3.2 设计数据通路

设计了有3种类型指令的数据通路,包括R类型、lw、sw、addi、beq和ben指令的数据通路。

在设计数据通路前,需要熟悉了解这三种类型指令的格式。对于以上指令外,我还扩展了系统调用指令syscall。当运行该指令时,终止CPU的运行。

图 23 三种类型指令的格式

| 指令 | 描述 |

|---|---|

| lw | 字载入 |

| sw | 字存储 |

| addi | 立即数加法 |

| beq | 如果相等则跳转 |

| bne | 如果不相等则跳转 |

表 5 指令描述

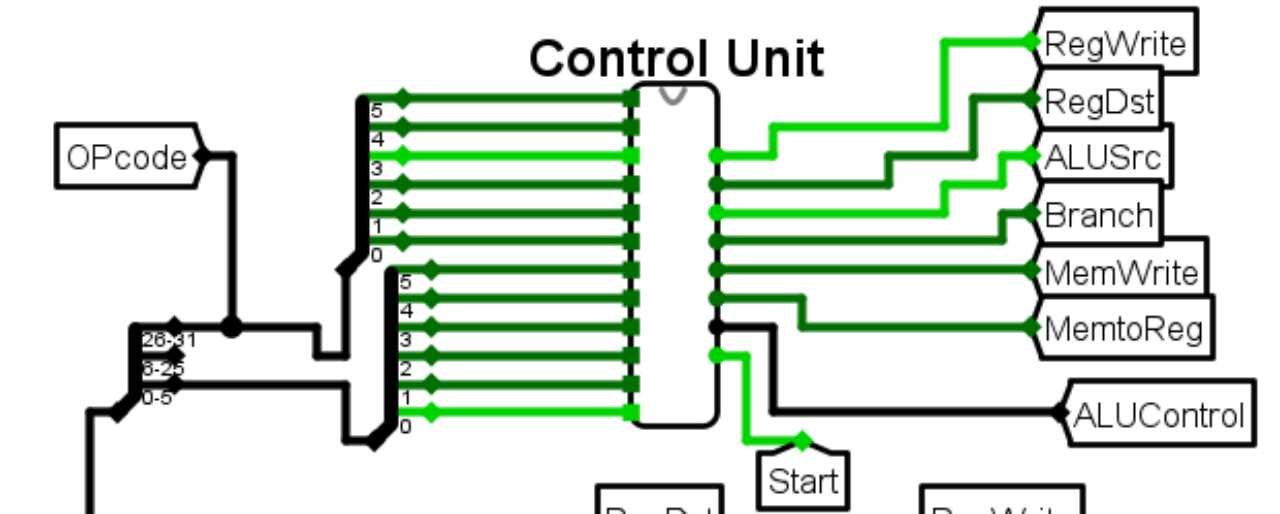

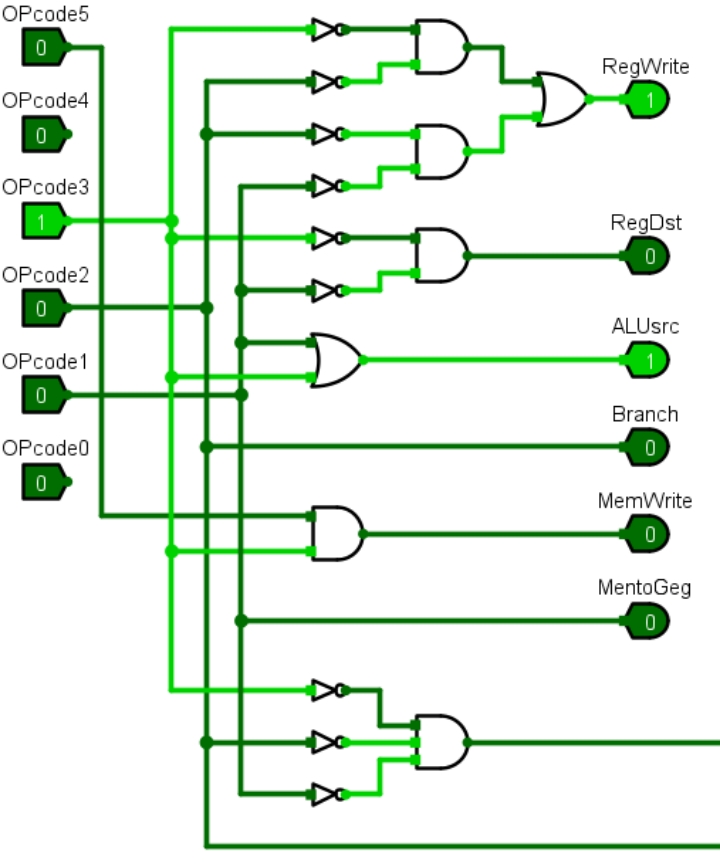

3.3设计控器

对于各种指令不同的数据通路,我设计了控制器输出多个控制信号。控制单元主要分为主译码器和复译码器。控制单元是基于指令中的opcode字段和funct字段计算控制信号。大多数的控制信号来自opcode字段,但是R-类型指令也使用funct字段决定ALU的操作。为了简化组合逻辑,我把控制单元分成了两个组合逻辑部分。如图19所示,主译码器从opcode中计算出大部分的输出信号,同时也会产生一个两位的ALUOP信号,ALU译码器使用ALUOP信号并且结合funct字段计算ALUControl。

所有的R-类型指令使用相同的主译码器值,因为它们的差异仅仅在于ALU译码器的输出。对于所有不需要写入寄存器文件的指令(sw和beq、bne),不必关心RegDst和MemtoReg信号,所以我在真值表中把它们记为X。

图 24 完整的单周期MIPS处理器

图 25 控制器

图 26 主译码器电路

图 27 ALU译码器电路

| ALUOP | funct | ALUControl |

|---|---|---|

| 00 | X | 010 |

| X1 | X | 110 |

| 1X | 100000 | 010 |

| 1X | 100010 | 110 |

| 1X | 100100 | 000 |

| 1X | 100101 | 001 |

| 1X | 101010 | 111 |

图 28 ALU译码器真值表

| 指令 | 操作码 | RegWrite | RegDst | ALUsrc | Branch | MemWrite | MentoReg | ALUOP |

|---|---|---|---|---|---|---|---|---|

| R-类型 | 000000 | 1 | 1 | 0 | 0 | 0 | 0 | 10 |

| lw | 100011 | 1 | 0 | 1 | 0 | 0 | 0 | 00 |

| sw | 101011 | 0 | X | 1 | 0 | 1 | X | 00 |

| beq | 000100 | 0 | X | 0 | 1 | 0 | X | 01 |

| bne | 000101 | 0 | X | 0 | 1 | 0 | X | 01 |

| addi | 001000 | 1 | 0 | 1 | 0 | 0 | 0 | 00 |

图 29 主译码器真值表

| 指令 | 操作码 | ALU-ZERO | PCBranch |

|---|---|---|---|

| beq | 000100 | 0 | 1 |

| bne | 000101 | 1 | 1 |

图 30 PCBranch译码器真值表

| 指令 | funct | Start |

|---|---|---|

| syscall | 000100 | 0 |

| 其他 | 其他 | 1 |

图 31 Start真值表

五.实验结果

5.1 实验1结果

使用计数器循环递增产生0-15的二进制数传送给自己设计的七段译码电路芯片,使用七段数码管显示译码结果。四个电路分别能够实现显示0到9的数字且大于9不显示、显示0到9的数字且大于9显示E、显示0到F的且有极性控制、显示0到F的数字或字母。

图 32 七段数码管译码电路测试结果

5.2 实验2结果

以二进制形式输入乘数和被乘数,计算十进制17×2的结果,测试结果正确。

图 33 基础乘法器测试结果

图 34 快速乘法器测试结果

5.3 实验3结果

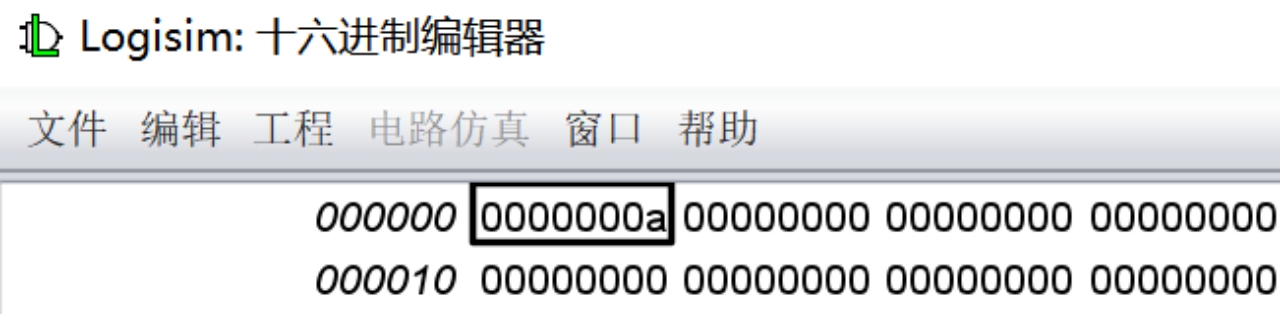

在ROM中装载老师提供的sort.hex测试代码,观察RAM中得到的排序结果,得到的排序结果正确,满足降序排序。

图 35 排序结果

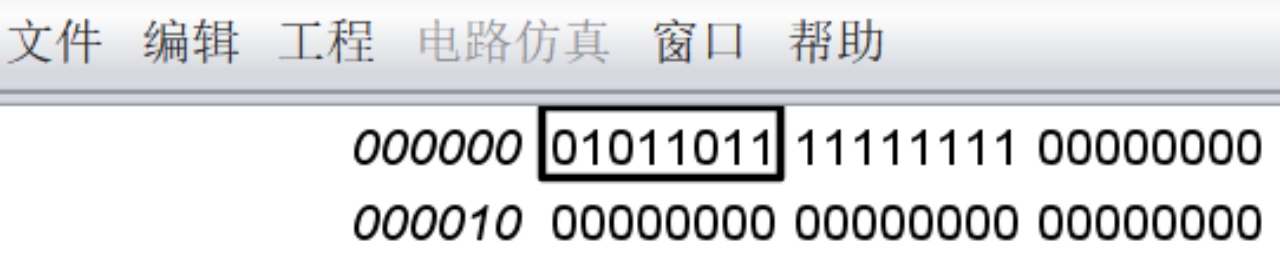

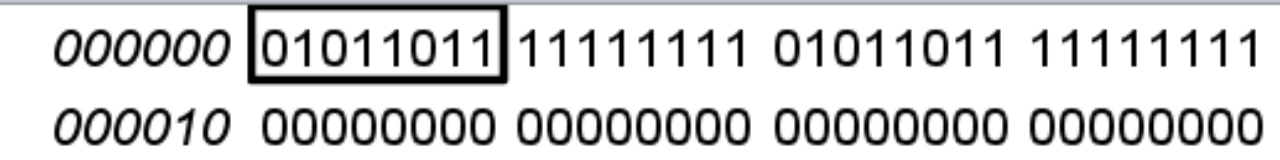

我额外地设计了以下的MIPS指令,用来测试该单周期CPU。

(1)设计测试用例

| 汇编语言 | 机器语言 |

|---|---|

| addi $ s0 ,$ 0 , 10 | 2010000a |

| addi $s1,$0,0 | 20110000 |

| sw s 0 , 0 ( s0,0( s0,0(s1) | ae300000 |

| 汇编语言 | 机器语言 |

|---|---|

| and $ s3 ,$ s1 , $ s2 | 02329824 |

| or $ s4 ,$ s1 , $ s2 | 0232a024 |

(2)测试结果

图 36 用例1测试结果

图 37 用例2输入

图 38 用例2输出

2个测试用例结果正确。

六.实验总结

在这次实验过程中,我对于卡诺图化简逻辑、无关项、乘法器原理、有限状态机和单周期CPU的知识有了更为深入的了解。在设计电路的过程中,不仅仅需要对这些知识熟悉掌握,而且还需要我们有动手实践的能力。这几个实验都是在logisim平台上完成,刚开始上手的时候,会感到有一些不适应,经过这几次实验后,我对于这个软件更加熟悉了解。当然,在实验中我也存在着不足的地方,比如在设计单周期CPU的时候,考虑不够周全,刚开始的时候设计的数据通路没有包括bne指令的,结果在对老师给的代码测试时,发现测试的结果有一些错误,后来我仔细检查了数据通路后,发现缺少了这一指令的数据通路,经过修改完善后,测试结果正常。

我认为可以创新的地方是快速乘法器,我设计的快速乘法器是一次进行两位运算的。但是我在查阅资料的过程中发现,快速乘法器可以实现一次性更多位的运算,比如一次进行3位运算,这样需要考虑的操作可能会更多。但是由于时间的关系,最终没有时间去实现这一创新。

对于这门课程,我的学习过程体验是很好的。课程中安排有实验的内容,并且安排时间给学生上机做实验,这对于深入理解教材中的知识是很有帮助的,对于我们理解计算机的一些底层的逻辑结构和原理很有帮助。姜老师对于课程的设计也很合理,把知识讲解的清晰而且易于理解。教学内容细化且富有层次,设计的思路和方法既向我们传授了知识又具有启发性。对于课程我提出的建议是,希望老师能够多安排这样的实验,比如安排对于高速缓存的设计和虚拟存储器的设计这一方面的实验内容。

总而言之,在这门课程中,教学内容成功融合了数字逻辑和计算机体系结构。介绍了很多数字系统设计的内容,最终引出了计算机体系结构,对于我们如何完美地设计复杂系统提供了很好的指导。

智能推荐

什么是内部类?成员内部类、静态内部类、局部内部类和匿名内部类的区别及作用?_成员内部类和局部内部类的区别-程序员宅基地

文章浏览阅读3.4k次,点赞8次,收藏42次。一、什么是内部类?or 内部类的概念内部类是定义在另一个类中的类;下面类TestB是类TestA的内部类。即内部类对象引用了实例化该内部对象的外围类对象。public class TestA{ class TestB {}}二、 为什么需要内部类?or 内部类有什么作用?1、 内部类方法可以访问该类定义所在的作用域中的数据,包括私有数据。2、内部类可以对同一个包中的其他类隐藏起来。3、 当想要定义一个回调函数且不想编写大量代码时,使用匿名内部类比较便捷。三、 内部类的分类成员内部_成员内部类和局部内部类的区别

分布式系统_分布式系统运维工具-程序员宅基地

文章浏览阅读118次。分布式系统要求拆分分布式思想的实质搭配要求分布式系统要求按照某些特定的规则将项目进行拆分。如果将一个项目的所有模板功能都写到一起,当某个模块出现问题时将直接导致整个服务器出现问题。拆分按照业务拆分为不同的服务器,有效的降低系统架构的耦合性在业务拆分的基础上可按照代码层级进行拆分(view、controller、service、pojo)分布式思想的实质分布式思想的实质是为了系统的..._分布式系统运维工具

用Exce分析l数据极简入门_exce l趋势分析数据量-程序员宅基地

文章浏览阅读174次。1.数据源准备2.数据处理step1:数据表处理应用函数:①VLOOKUP函数; ② CONCATENATE函数终表:step2:数据透视表统计分析(1) 透视表汇总不同渠道用户数, 金额(2)透视表汇总不同日期购买用户数,金额(3)透视表汇总不同用户购买订单数,金额step3:讲第二步结果可视化, 比如, 柱形图(1)不同渠道用户数, 金额(2)不同日期..._exce l趋势分析数据量

宁盾堡垒机双因素认证方案_horizon宁盾双因素配置-程序员宅基地

文章浏览阅读3.3k次。堡垒机可以为企业实现服务器、网络设备、数据库、安全设备等的集中管控和安全可靠运行,帮助IT运维人员提高工作效率。通俗来说,就是用来控制哪些人可以登录哪些资产(事先防范和事中控制),以及录像记录登录资产后做了什么事情(事后溯源)。由于堡垒机内部保存着企业所有的设备资产和权限关系,是企业内部信息安全的重要一环。但目前出现的以下问题产生了很大安全隐患:密码设置过于简单,容易被暴力破解;为方便记忆,设置统一的密码,一旦单点被破,极易引发全面危机。在单一的静态密码验证机制下,登录密码是堡垒机安全的唯一_horizon宁盾双因素配置

谷歌浏览器安装(Win、Linux、离线安装)_chrome linux debian离线安装依赖-程序员宅基地

文章浏览阅读7.7k次,点赞4次,收藏16次。Chrome作为一款挺不错的浏览器,其有着诸多的优良特性,并且支持跨平台。其支持(Windows、Linux、Mac OS X、BSD、Android),在绝大多数情况下,其的安装都很简单,但有时会由于网络原因,无法安装,所以在这里总结下Chrome的安装。Windows下的安装:在线安装:离线安装:Linux下的安装:在线安装:离线安装:..._chrome linux debian离线安装依赖

烤仔TVの尚书房 | 逃离北上广?不如押宝越南“北上广”-程序员宅基地

文章浏览阅读153次。中国发达城市榜单每天都在刷新,但无非是北上广轮流坐庄。北京拥有最顶尖的文化资源,上海是“摩登”的国际化大都市,广州是活力四射的千年商都。GDP和发展潜力是衡量城市的数字指...

随便推点

java spark的使用和配置_使用java调用spark注册进去的程序-程序员宅基地

文章浏览阅读3.3k次。前言spark在java使用比较少,多是scala的用法,我这里介绍一下我在项目中使用的代码配置详细算法的使用请点击我主页列表查看版本jar版本说明spark3.0.1scala2.12这个版本注意和spark版本对应,只是为了引jar包springboot版本2.3.2.RELEASEmaven<!-- spark --> <dependency> <gro_使用java调用spark注册进去的程序

汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用_uds协议栈 源代码-程序员宅基地

文章浏览阅读4.8k次。汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用,代码精简高效,大厂出品有量产保证。:139800617636213023darcy169_uds协议栈 源代码

AUTOSAR基础篇之OS(下)_autosar 定义了 5 种多核支持类型-程序员宅基地

文章浏览阅读4.6k次,点赞20次,收藏148次。AUTOSAR基础篇之OS(下)前言首先,请问大家几个小小的问题,你清楚:你知道多核OS在什么场景下使用吗?多核系统OS又是如何协同启动或者关闭的呢?AUTOSAR OS存在哪些功能安全等方面的要求呢?多核OS之间的启动关闭与单核相比又存在哪些异同呢?。。。。。。今天,我们来一起探索并回答这些问题。为了便于大家理解,以下是本文的主题大纲:[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JCXrdI0k-1636287756923)(https://gite_autosar 定义了 5 种多核支持类型

VS报错无法打开自己写的头文件_vs2013打不开自己定义的头文件-程序员宅基地

文章浏览阅读2.2k次,点赞6次,收藏14次。原因:自己写的头文件没有被加入到方案的包含目录中去,无法被检索到,也就无法打开。将自己写的头文件都放入header files。然后在VS界面上,右键方案名,点击属性。将自己头文件夹的目录添加进去。_vs2013打不开自己定义的头文件

【Redis】Redis基础命令集详解_redis命令-程序员宅基地

文章浏览阅读3.3w次,点赞80次,收藏342次。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。当数据量很大时,count 的数量的指定可能会不起作用,Redis 会自动调整每次的遍历数目。_redis命令

URP渲染管线简介-程序员宅基地

文章浏览阅读449次,点赞3次,收藏3次。URP的设计目标是在保持高性能的同时,提供更多的渲染功能和自定义选项。与普通项目相比,会多出Presets文件夹,里面包含着一些设置,包括本色,声音,法线,贴图等设置。全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,主光源和附加光源在一次Pass中可以一起着色。URP:全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,一次Pass可以计算多个光源。可编程渲染管线:渲染策略是可以供程序员定制的,可以定制的有:光照计算和光源,深度测试,摄像机光照烘焙,后期处理策略等等。_urp渲染管线